没有合适的资源?快使用搜索试试~ 我知道了~

首页MSP430G2553中文手册:低功耗混合信号控制器特性概览

MSP430G2553中文手册:低功耗混合信号控制器特性概览

需积分: 10 13 下载量 104 浏览量

更新于2024-07-18

收藏 1.82MB PDF 举报

MSP430G2553中文数据手册是一份详细介绍了TI公司出品的MSP430系列微控制器MSP430G2x53的具体特性和功能的手册。该款微控制器具有以下核心特点: 1. 低功耗设计:MSP430G2553的工作电压范围广泛,从1.8V至3.6V,特别适合低功耗应用,如在1MHz频率下,工作模式下的电流仅为230μA,而在待机模式下,能耗更是低至0.5μA,甚至在关闭模式下保持RAM保持功能时,能耗仅0.1μA。 2. 串行通信支持:它配备了通用串行通信接口(USCI),包括增强型UART,支持自动波特率检测和IrDA编码/解码功能,这使得设备能够进行高效的数据传输。 3. 多模式操作:除了标准模式和低功耗模式,还提供5种节能模式,满足不同场景下的能源管理需求。模拟信号处理功能也十分强大,包括模拟信号比较、斜率检测等。 4. 高速数据转换:16位RISC架构提供了高效的指令执行速度,例如200ksps的模数转换器,这对于实时数据采集和处理非常重要。 5. 电源管理和保护:内置欠压检测器确保系统在电压不稳定时能及时响应,基本时钟模块支持多种配置,包括内部和外部频率校准。 6. 集成功能:串行编程功能允许用户在板上轻松设置,包括四路校准频率选项,最高可达16MHz,同时具备超低功耗LF震荡器。 7. 快速唤醒:能在不到1μs的时间内从待机模式唤醒,提高了系统的响应速度。 8. 安全性:通过安全熔丝机制,可以实现可编程的安全措施,确保系统的稳定运行。 这份数据手册是开发人员在设计和应用MSP430G2553时的重要参考文档,包含了丰富的技术细节和功能说明,对于理解和利用这款微控制器的各项特性具有很高的价值。

资源详情

资源推荐

MSP430G2x53

MSP430G2x13

www.ti.com.cn

ZHCS178G –APRIL 2011–REVISED AUGUST 2012

特特别别功功能能寄寄存存器器 (SFR)

大多数中断及模块启用位均采集在最低的地址空间里。 未分配给一个功能性用途的特别功能寄存器位本身未在器件

中出现。 简单的软件访问与这种配置一起提供。

图图例例 rw:: 可以对位进行读写操作。

rw-0,,1:: 可以对位进行读写操作。 由 PUC 对其进行复位或置位。

rw-(0,,1):: 可以对位进行读写操作。 由 POR 对其进行复位或置位。

器件中不存在 SFR 位。

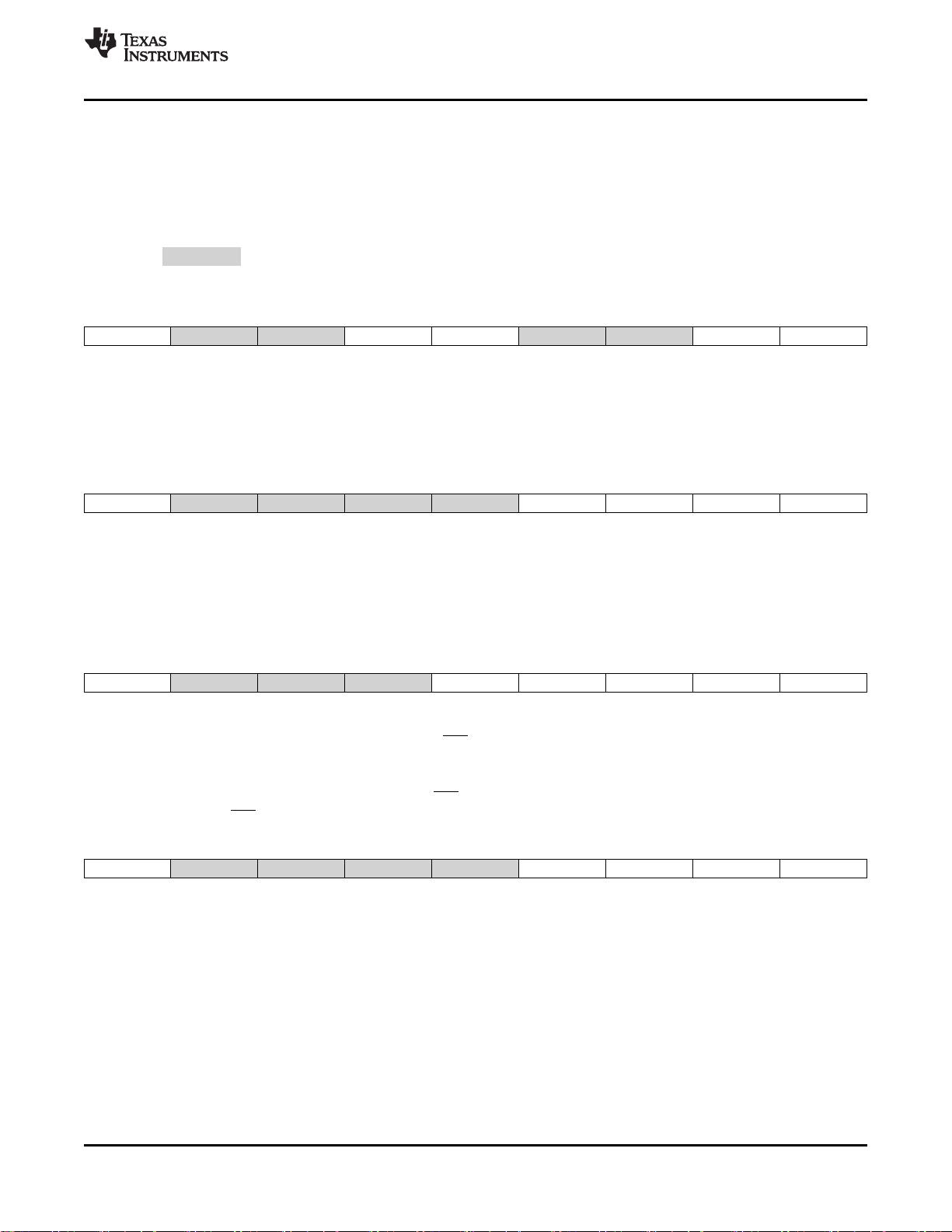

Table 6. 中中断断启启用用寄寄存存器器 1 和和 2

地地址址 7 6 5 4 3 2 1 0

00h ACCVIE NMIIE OFIE WDTIE

rw-0 rw-0 rw-0 rw-0

WDTIE 安全装置定时器中断启用。 如果选择的是安全装置模式,则处于非激活状态。 如果安全装置定时器被配置成间隔定时器

模式,则处于激活状态。

OFIE 振荡器故障中断启用

NMIIE (不)可屏蔽中断启用

ACCVIE 闪存访问冲突中断启用

地地址址 7 6 5 4 3 2 1 0

01h UCB0TXIE UCB0RXIE UCA0TXIE UCA0RXIE

rw-0 rw-0 rw-0 rw-0

UCA0RXIE USCI_A0 接收中断启用

UCA0TXIE USCI_A0 发送中断启用

UCB0RXIE USCI_B0 接收中断启用

UCB0TXIE USCI_B0 发送中断启用

Table 7. 中中断断标标志志寄寄存存器器 1 和和 2

地地址址 7 6 5 4 3 2 1 0

02h NMIIFG RSTIFG PORIFG OFIFG WDTIFG

rw-0 rw-(0) rw-(1) rw-1 rw-(0)

WDTIFG 安全装置定时器溢出(在安全装置模式中)或安全密钥冲突上的设置。

V

CC

加电时的复位或者一个处于复位模式的RST/NMI 引脚的复位条件。

OFIFG 振荡器故障时的标志设定。

PORIFG 加电复位中断标志。 在 V

CC

加电时设定。

RSTIFG 外部复位中断标志。 在处于复位模式中的RST/NMI 引脚上设定一个复位条件。 V

CC

加电时复位。

NMIIFG 通过RST/NMI 引脚进行设定

地地址址 7 6 5 4 3 2 1 0

03h UCB0TXIFG UCB0RXIFG UCA0TXIFG UCA0RXIFG

rw-1 rw-0 rw-1 rw-0

UCA0RXIFG USCI_A0 接收中断标志

UCA0TXIFG USCI_A0 发送中断标志

UCB0RXIFG USCI_B0 接收中断标志

UCB0TXIFG USCI_B0 发送中断标志

Copyright © 2011–2012, Texas Instruments Incorporated 13

MSP430G2x53

MSP430G2x13

ZHCS178G –APRIL 2011–REVISED AUGUST 2012

www.ti.com.cn

内内存存组组织织

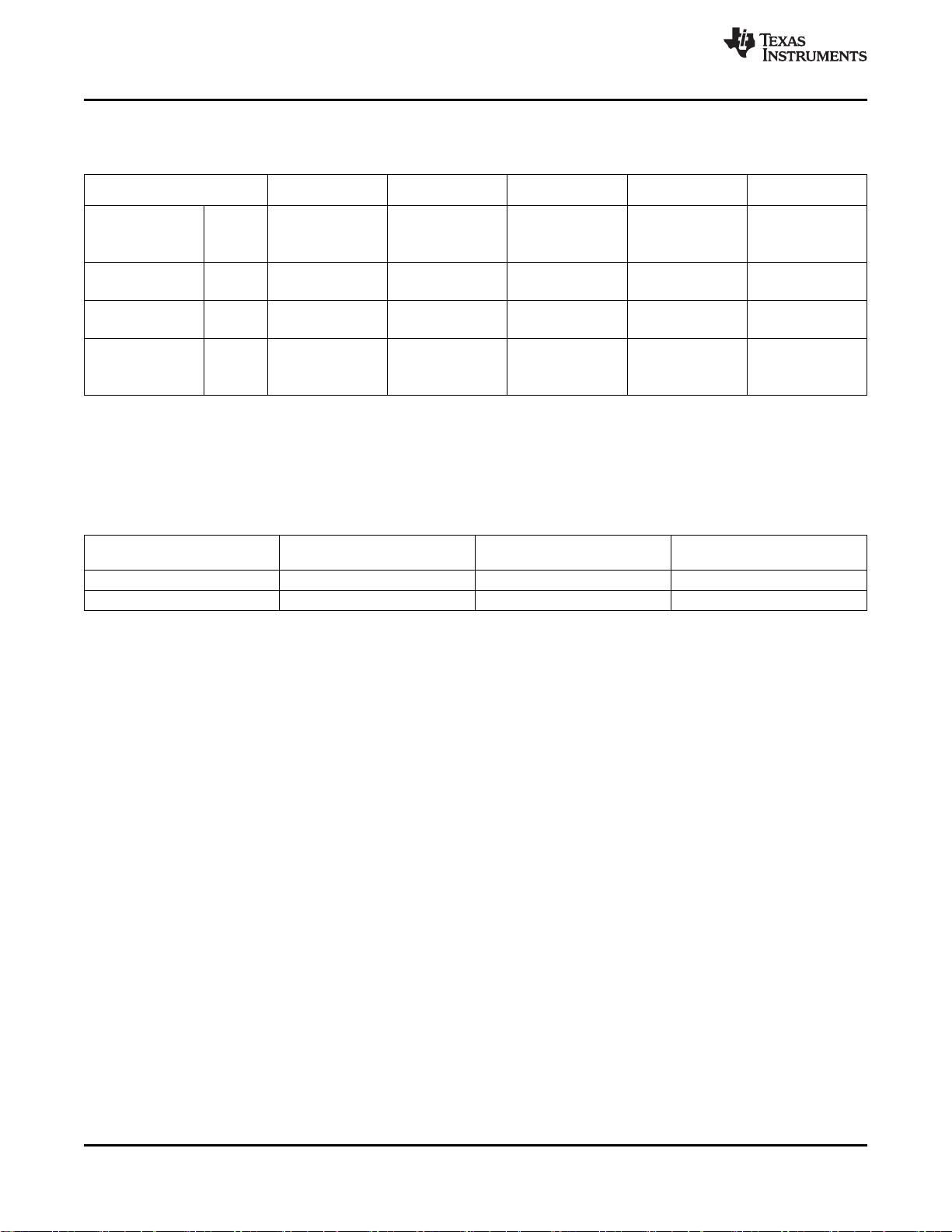

Table 8. 内内存存组组织织

MSP430G2153 MSP430G2253 MSP430G2353 MSP430G2453 MSP430G2553

MSP430G2113 MSP430G2213 MSP430G2313 MSP430G2413 MSP430G2513

内存 尺寸 1kB 2kB 4kB 8kB 16kB

主:中断矢量 闪存 0xFFFF 至 0xFFC0 0xFFFF 至 0xFFC0 0xFFFF 至 0xFFC0 0xFFFF 至 0xFFC0 0xFFFF 至 0xFFC0

主:代码内存 闪存 0xFFFF 至 0xFC00 0xFFFF 至 0xF800 0xFFFF 至 0xF000 0xFFFF 至 0xE000 0xFFFF 至 0xC000

信息内存 尺寸 256 字节 256 字节 256 字节 256 字节 256 字节

闪存 010FFh 至 01000h 010FFh 至 01000h 010FFh 至 01000h 010FFh 至 01000h 010FFh 至 01000h

RAM 尺寸 256 字节 256 字节 256 字节 512 字节 512 字节

0x02FF 至 0x0200 0x02FF 至 0x0200 0x02FF 至 0x0200 0x03FF 至 0x0200 0x03FF 至 0x0200

外设 16 位 01FFh 至 0100h 01FFh 至 0100h 01FFh 至 0100h 01FFh 至 0100h 01FFh 至 0100h

8 位 0FFh 至 010h 0FFh 至 010h 0FFh 至 010h 0FFh 至 010h 0FFh 至 010h

8 位 SFR 0Fh 至 00h 0Fh 至 00h 0Fh 至 00h 0Fh 至 00h 0Fh 至 00h

引引导导载载入入程程序序 (BSL)

MSP430 BSL 使用户能够采用一个 UART 串行接口进行闪存或 RAM 编程。 通过 BSL 对 MSP430 内存的访问由

用户规定的密码来提供保护。 如需了解 BSL 及其可实现方案的完整说明和特性,请查阅

《借助引导载入程序来进

行

MSP430

编程用户指南》

(文献编号:SLAU319)。

Table 9. BSL 功功能能引引脚脚

20 引引脚脚 PW 封封装装

BSL 功功能能 28 引引脚脚 PW 封封装装 32 引引脚脚 RHB 封封装装

20 引引脚脚 N 封封装装

数据发送 3 - P1.1 3 - P1.1 1 - P1.1

数据接收 7 - P1.5 7 - P1.5 5 - P1.5

闪闪存存

闪存可存储器通过 Spy-Bi-Wire/JTAG 端口进行编程或由 CPU 进行系统内编程。 CPU 能执行到闪存的单字节和单

字写入操作。 闪存的特性包括:

• 闪存具有 n 个主内存段和 4 个均为 64字节的信息内存段(A 至 D)。 主内存中每一段的大小为 512 字节。

• 0 至 n 段可以一步擦除,也可以单独地擦除每一段。

• A 至 D 段可以单独擦除,也可将 0 至 n 段作为一个组进行擦除。 A 至 D 段也被称为

信息内存

。

• A 段包含校准数据。 在复位之后,提供防止段 A 被编程及擦除的保护。 可以将其解锁,但如果需要器件专用的

校准数据,应注意不要将该段擦除。

14 Copyright © 2011–2012, Texas Instruments Incorporated

DCO(RSEL,DCO+1)

DCO(RSEL,DCO)

average

DCO(RSEL,DCO) DCO(RSEL,DCO+1)

32 × f × f

f =

MOD × f + (32 – MOD) × f

MSP430G2x53

MSP430G2x13

www.ti.com.cn

ZHCS178G –APRIL 2011–REVISED AUGUST 2012

外外设设

通过数据、地址和控制总线将外设连接至 CPU,并可采用所有的指令对外设进行处理。 如需了解完整的模块说明,

请查阅

《

MSP430x2xx

系列用户指南》

(文献编号:SLAU144)。

振振荡荡器器和和系系统统时时钟钟

时钟系统由基本时钟模块提供支持,此时钟模块支持一个 32768Hz 手表晶体振荡器、一个内部超低功耗低频振荡

器和一个内部数字控制振荡器 (DCO) 。 基本时钟模块专为同时满足低系统成本及低功耗要求而设计。 内部 DCO

提供了一个快速接通时钟源并可在不到 1µs 的时间里实现稳定。 基本时钟模块提供了以下时钟信号:

• 辅助时钟 (ACLK),此时钟由一个 32768 Hz 手表晶振或内部 LF 振荡器提供信号源。

• 主时钟 (MCLK),CPU 所采用的系统时钟。

• 系统子时钟 (SMCLK),外设模块所采用的子系统时钟。

用于校准 DCO 输出频率的 DCO 设定值存储于信息内存的 A 段中。

主主 DCO 特特性性

• 由 RSELx 选择的所有范围与 RSELx + 1 重叠:RSELx = 0 与 RSELx = 1 重叠,。。。 RSELx=14 与

RSELx=15 重叠。

• DCO 控制位 DCOx 具有一个由参数 S

DCO

规定的步长。

• 调制控制位 MODx 用于选择 32 个 DCOCLK 周期之内 f

DCO(RSEL,DCO+1)

的使用频度。 频率 f

DCO(RSEL,DCO)

用

于剩余的周期。 该频率是一个平均值,等于:

Copyright © 2011–2012, Texas Instruments Incorporated 15

MSP430G2x53

MSP430G2x13

ZHCS178G –APRIL 2011–REVISED AUGUST 2012

www.ti.com.cn

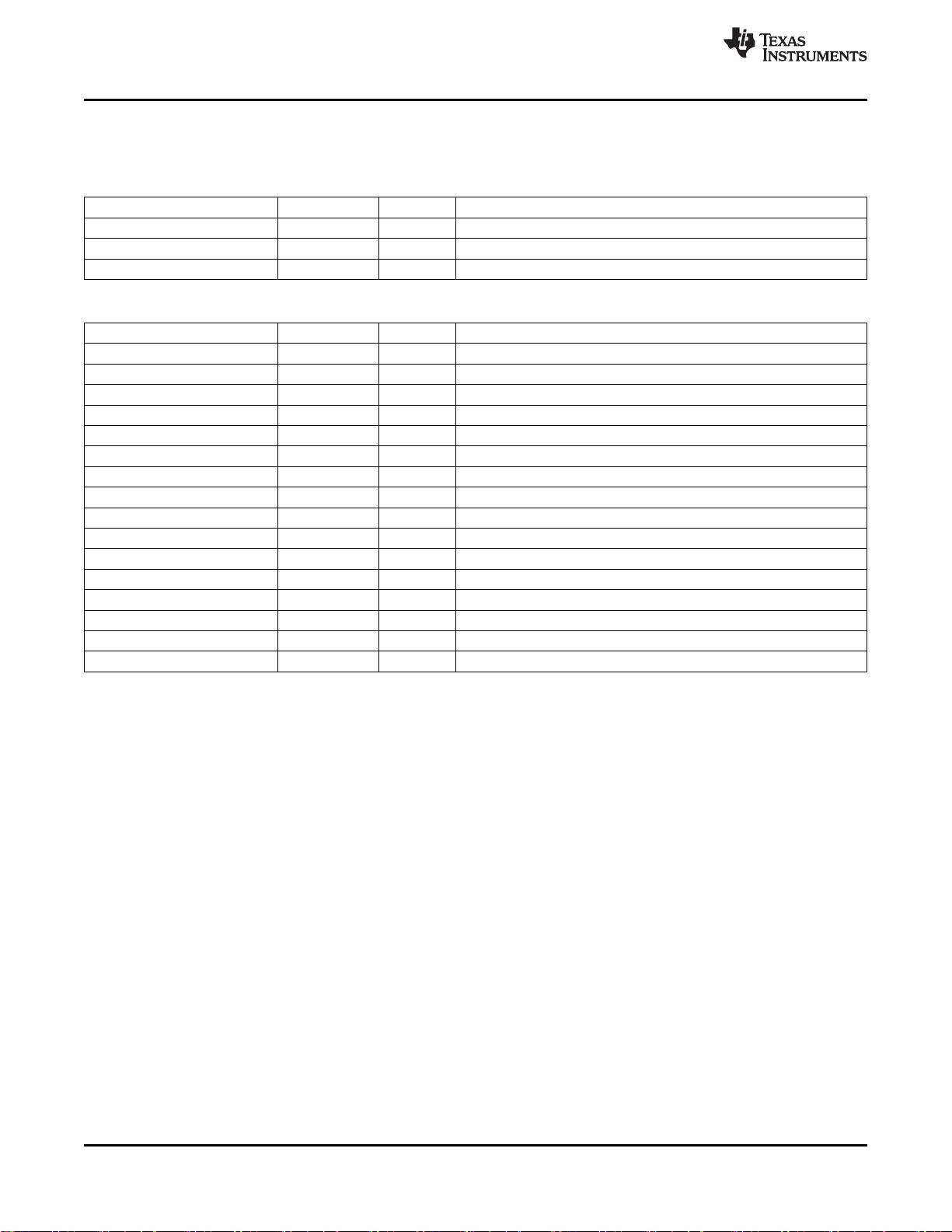

校校准准数数据据存存储储于于信信息息内内存存的的 A 段段

将校准数据存储起来,用于 DCO 及以一种组织结构为标志-长度-数值的 ADC10。

Table 10. ADC 校校准准标标志志所所采采用用的的标标志志

名名称称 地地址址 值值 说说明明

TAG_DCO_30 0x10F6 0x01 V

CC

=3V 时 DCO 频率校准,而在校准时 T

A

=30°C

TAG_ADC10_1 0x10DA 0x10 ADC10_1 校准标志

TAG_EMPTY - 0xFE 空内存区的标识符

Table 11. ADC 校校准准标标志志所所采采用用的的标标签签

标标签签 地地址址偏偏移移 尺尺寸寸 校校准准时时的的条条件件/描描述述

CAL_ADC_25T85 0x0010 字 INCHx=0x1010,REF2_5=1,T

A

=85°C

CAL_ADC_25T30 0x000E 字 INCHx=0x1010,REF2_5=1,T

A

=30°C

CAL_ADC_25VREF_FACTOR 0x000C 字 REF2_5=1,T

A

=30°C,I

VREF+

=1mA

CAL_ADC_15T85 0x000A 字 INCHx=0x1010,REF2_5=0,T

A

=85°C

CAL_ADC_15T30 0x0008 字 INCHx=0x1010,REF2_5=0,T

A

=30°C

CAL_ADC_15VREF_FACTOR 0x0006 字 REF2_5=0,T

A

=30°C,I

VREF+

=0.5 mA

CAL_ADC_OFFSET 0x0004 字 外部 VREF=1.5 V, f

ADC10CLK

=5MHz

CAL_ADC_GAIN_FACTOR 0x0002 字 外部 VREF=1.5 V, f

ADC10CLK

=5MHz

CAL_BC1_1MHZ 0x0009 字节 -

CAL_DCO_1MHZ 0x0008 字节 -

CAL_BC1_8MHZ 0x0007 字节 -

CAL_DCO_8MHZ 0x0006 字节 -

CAL_BC1_12MHZ 0x0005 字节 -

CAL_DCO_12MHZ 0x0004 字节 -

CAL_BC1_16MHZ 0x0003 字节 -

CAL_DCO_16MHZ 0x0002 字节 -

欠欠压压

欠压电路的目的是在加电及断电期间向器件提供正确的内部复位信号。

数数字字 I/O

提供了多达 3 个 8 位 I/O 端口:

• 所有单独的 I/O 位均可进行独立编程。

• 输入、输出和中断条件的任一组合(仅限端口 P1 和端口 P2)都是可行的。

• 用于端口 P1 和端口 P2(如果可用的话)的所有位的边沿可选中断输入功能。

• 所有指令均支持到端口控制寄存器的读/写访问。

• 每个 I/O 具有一个可单独编程的上拉或下拉电阻器。

• 每个 I/O 具有一个可单独编程的引脚振荡器使能位,此使能位用于启用低成本触摸屏。

WDT+ 安安全全装装置置定定时时器器

安全装置定时器 (WDT+) 模块的主要功能是在软件问题发生后执行受控的系统重启。 如果选定的时间间隔结束,

则产生一个系统复位。 如果在某种应用中不需要安全装置功能,则该模块可被禁用或配置为一个间隔定时器,并能

在选定的时间间隔上产生中断。

16 Copyright © 2011–2012, Texas Instruments Incorporated

剩余76页未读,继续阅读

qq_30448825

- 粉丝: 0

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 十种常见电感线圈电感量计算公式详解

- 军用车辆:CAN总线的集成与优势

- CAN总线在汽车智能换档系统中的作用与实现

- CAN总线数据超载问题及解决策略

- 汽车车身系统CAN总线设计与应用

- SAP企业需求深度剖析:财务会计与供应链的关键流程与改进策略

- CAN总线在发动机电控系统中的通信设计实践

- Spring与iBATIS整合:快速开发与比较分析

- CAN总线驱动的整车管理系统硬件设计详解

- CAN总线通讯智能节点设计与实现

- DSP实现电动汽车CAN总线通讯技术

- CAN协议网关设计:自动位速率检测与互连

- Xcode免证书调试iPad程序开发指南

- 分布式数据库查询优化算法探讨

- Win7安装VC++6.0完全指南:解决兼容性与Office冲突

- MFC实现学生信息管理系统:登录与数据库操作

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功