纳米100系列:Cortex-M0入门介绍

需积分: 9 190 浏览量

更新于2024-07-17

收藏 1.05MB PDF 举报

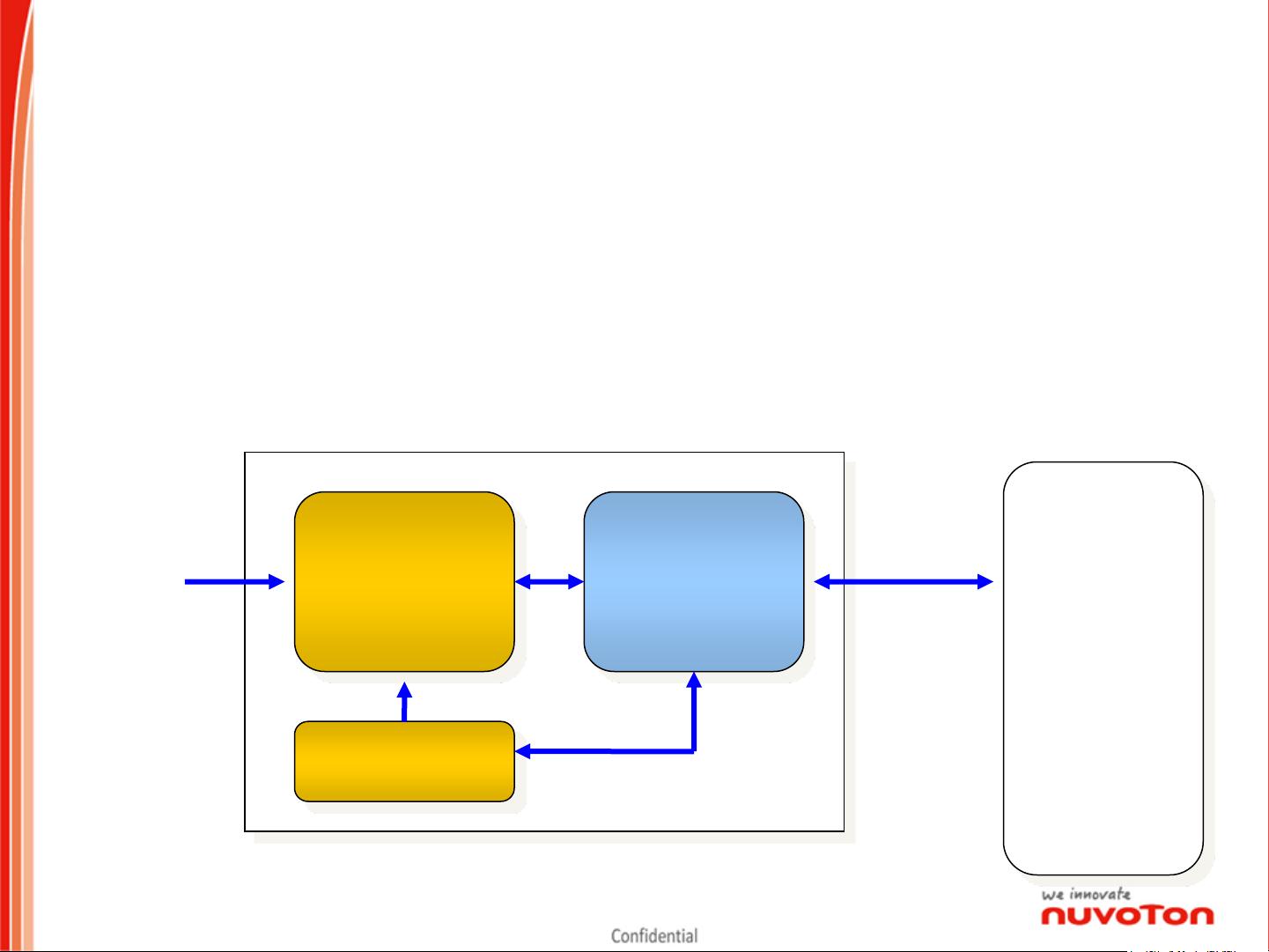

本资源是NuMicro Nano100系列培训资料,针对Cortex-M0处理器进行详细介绍。首先,讲解了ARM架构的发展路线图,明确了Cortex-M系列处理器在ARM架构中的位置,特别是Cortex-M0作为ARMv6-M的一个子集,与ARMv7-M兼容,仅支持Thumb指令集,无需混合代码。

Cortex-M0处理器的核心特性包括:

1. **处理器核心**:作为微控制器的基础,Cortex-M0提供了基本的运算和控制功能,具有56条指令,其中6条为32位长度,其余为16位长度,如BL(Branch)、DMB(Data Memory Barrier)、DSB(Data Synchronization Barrier)等。

2. **嵌套向量中断控制器(NVIC)**:负责中断管理,确保系统能够正确处理来自外设的各种中断事件,按照优先级顺序调度中断处理。

3. **系统定时器(SysTick)**:提供一个周期性的时钟源,用于计时、定时器和系统时间基准。

4. **存储器和外设**:包括程序存储器(ROM)、数据存储器(RAM),以及各种外围设备接口,如AHB-Lite总线,使得处理器能高效地与外设通信。

5. **异常模型**:Cortex-M0采用异常处理机制,异常可以是中断或硬件错误。每个异常都有编号、优先级和向量地址,向量地址固定为0,表示中断服务程序的入口点。

异常处理遵循一定的模式,每种异常类型都对应一个特定的向量地址,处理器在接收到异常后会跳转到对应的处理程序。由于不支持Interworking(混合指令集执行),程序员需注意使用自然对齐的数据访问,以充分利用硬件功能。

这份文档深入浅出地介绍了Cortex-M0处理器的基础架构,对开发人员理解和使用这种低功耗、高效的微控制器核心非常有帮助,无论是设计嵌入式系统还是进行软件开发,理解这些核心概念都是至关重要的。

2022-06-01 上传

2023-07-11 上传

2023-05-31 上传

2023-05-31 上传

2023-06-09 上传

2023-05-26 上传

2023-07-28 上传

2023-05-31 上传

2023-05-26 上传

weixin_38743481

- 粉丝: 695

- 资源: 4万+

最新资源

- 解决本地连接丢失无法上网的问题

- BIOS报警声音解析:故障原因与解决方法

- 广义均值移动跟踪算法在视频目标跟踪中的应用研究

- C++Builder快捷键大全:高效编程的秘密武器

- 网页制作入门:常用代码详解

- TX2440A开发板网络远程监控系统移植教程:易搭建与通用解决方案

- WebLogic10虚拟内存配置详解与优化技巧

- C#网络编程深度解析:Socket基础与应用

- 掌握Struts1:Java MVC轻量级框架详解

- 20个必备CSS代码段提升Web开发效率

- CSS样式大全:字体、文本、列表样式详解

- Proteus元件库大全:从基础到高级组件

- 74HC08芯片:高速CMOS四输入与门详细资料

- C#获取当前路径的多种方法详解

- 修复MySQL乱码问题:设置字符集为GB2312

- C语言的诞生与演进:从汇编到系统编程的革命