Tomasulo算法:设计、实质与执行流程

需积分: 50 28 浏览量

更新于2024-07-18

收藏 1.39MB PDF 举报

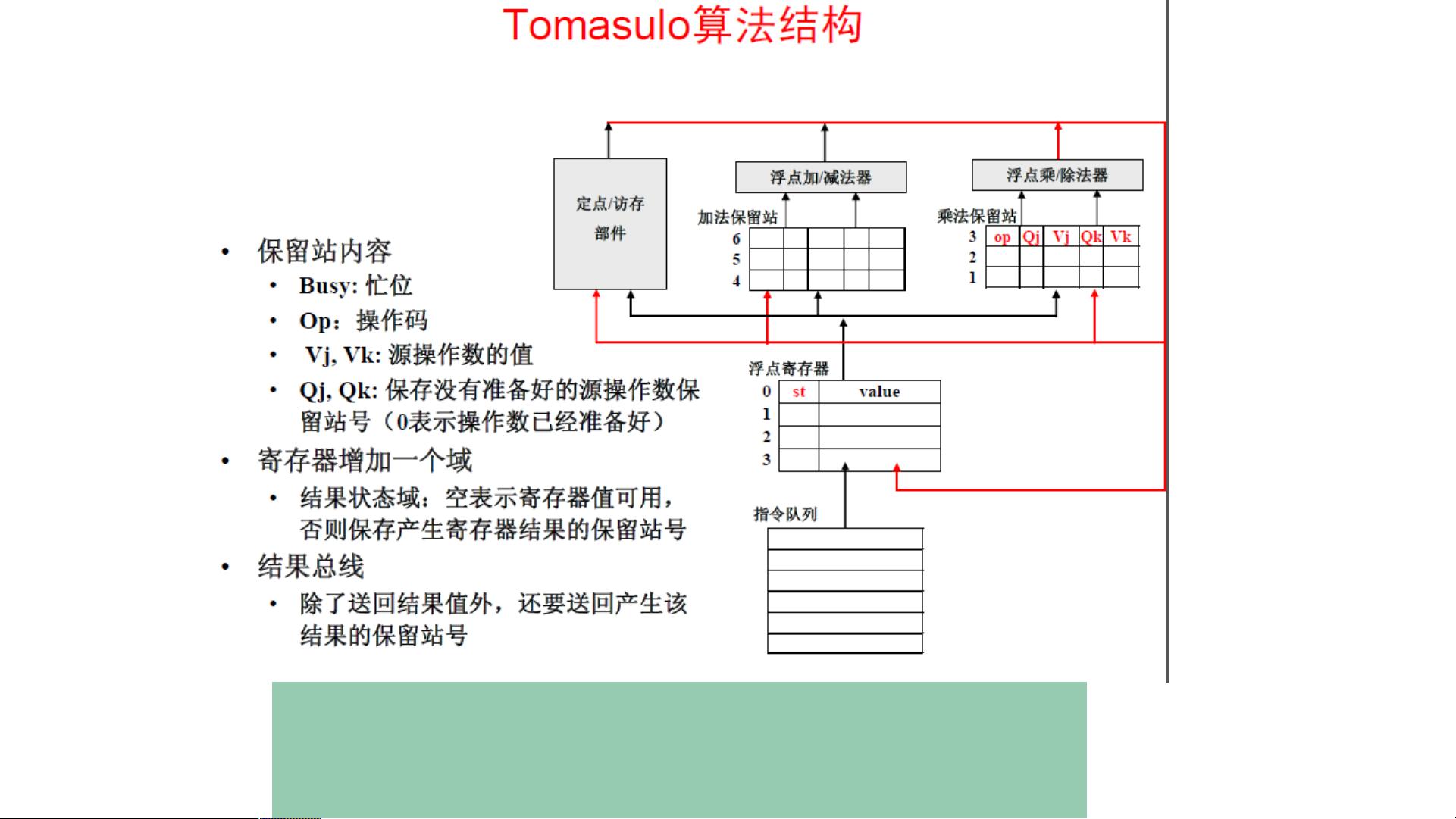

Tomasulo算法是一种高级流水线设计策略,用于解决处理器中的数据和控制相关性问题,提高处理器性能。它的核心在于动态数据通路调度和寄存器命名技术,确保指令能够有效地并行执行。

设计思路:

1. **提前预取指令**:Tomasulo算法通过设置指令缓冲区(如FP操作队列)来预先加载待执行的指令,减少流水线空转时间。

2. **数据准备监控**:算法通过记录操作数的状态(准备好了或仍在处理中),使用“保留站”来跟踪每个操作数的来源,例如浮点寄存器FP、load缓冲器等。

3. **寄存器换名技术**:当操作数未就绪时,指令中的寄存器名被替换为产生该操作数的保留站标识,通过保留站和输出逻辑实现寄存器名相关消除。

4. **通知机制**:运算结果由算术逻辑单元(ALU)通过总线通知保留站进行计算,并最终写回寄存器,保证数据的正确性。

实质:

- **指令预取与缓冲**:即将指令放入预备执行空间,确保指令流的连续性。

- **操作执行记录**:算法关注哪些操作可以立即执行,依赖于操作数的准备状态。

- **换名与记录-通知机制**:通过更名机制(FU保存指令名而非实际寄存器号),在操作数就绪时更新指令,通过通知机制协调各部分的通信。

- **三阶段流程**:包括Issue(取指令)、Execution(执行操作)和Writeresult(写回结果)。

Tomasulo算法的三个关键阶段:

1. **Issue**:从FP操作队列取出指令,如果预留站(RS)空闲,进行寄存器重命名和操作数分配。

2. **Execution**:一旦操作数准备好,执行指令,如果需要,通过公共数据总线(CDB)获取操作数。

3. **Writeresult**:完成操作后,将结果写回寄存器,并通过CDB通知等待的部件。

实例说明:

在示例中,指令执行状态分为“Exec”(执行中)、“Write”(写入阶段)和“Idle”(空闲)。如指令“LD F6 34+ R2”,当它试图读取F6的值时,如果F6尚未就绪,会进入保留站,而指令本身则会转换为保留站的标识。当F6的值准备好时,通过通知机制,该指令的寄存器名会恢复,并进行相应操作。

Tomasulo算法通过优化指令调度和寄存器管理,有效减少了数据相关和控制相关,使得处理器能够高效地处理多个指令,提高计算机体系结构的性能。

2023-05-30 上传

2023-09-16 上传

2023-03-27 上传

2023-06-12 上传

2023-06-08 上传

2023-02-22 上传

weixin_40764724

- 粉丝: 0

- 资源: 1

最新资源

- AirKiss技术详解:无线传递信息与智能家居连接

- Hibernate主键生成策略详解

- 操作系统实验:位示图法管理磁盘空闲空间

- JSON详解:数据交换的主流格式

- Win7安装Ubuntu双系统详细指南

- FPGA内部结构与工作原理探索

- 信用评分模型解析:WOE、IV与ROC

- 使用LVS+Keepalived构建高可用负载均衡集群

- 微信小程序驱动餐饮与服装业创新转型:便捷管理与低成本优势

- 机器学习入门指南:从基础到进阶

- 解决Win7 IIS配置错误500.22与0x80070032

- SQL-DFS:优化HDFS小文件存储的解决方案

- Hadoop、Hbase、Spark环境部署与主机配置详解

- Kisso:加密会话Cookie实现的单点登录SSO

- OpenCV读取与拼接多幅图像教程

- QT实战:轻松生成与解析JSON数据