Verilog HDL详解:组合电路模块与逻辑设计

需积分: 5 133 浏览量

更新于2024-07-15

收藏 3.76MB PDF 举报

"本资源主要介绍了Verilog HDL在组合电路模块设计中的应用,结合重庆大学光电工程学院的课程内容,讲解了如何使用Verilog HDL描述和实现数字逻辑电路,特别是组合逻辑电路的设计方法。"

在电子电路CAD及Verilog-HDL的课程中,我们学习了Verilog HDL这种强大的硬件描述语言,它被广泛用于数字系统的设计和描述。Verilog HDL不仅能够表示逻辑门电路和逻辑表达式,还能描述复杂的数字逻辑系统功能。它与VHDL并列为全球最流行的两种硬件描述语言,两者均在20世纪80年代中期诞生,并已成为IEEE的标准化语言。

组合逻辑电路是数字系统的基础模块,其特点是输出仅取决于当前输入,不包含任何记忆元素。组合逻辑电路包括常见的子电路,如数据选择器、编码器、解码器和代码转换器等。这些电路在设计中起到关键作用,它们通过不同的逻辑操作实现特定的功能。

在本章——组合电路模块中,我们深入探讨了以下内容:

1. **组合逻辑电路特点**:从功能上讲,组合逻辑电路的输出在任意时刻只依赖于当时的输入信号;从电路结构上看,它们不包含任何存储信息的元件,如触发器或寄存器。

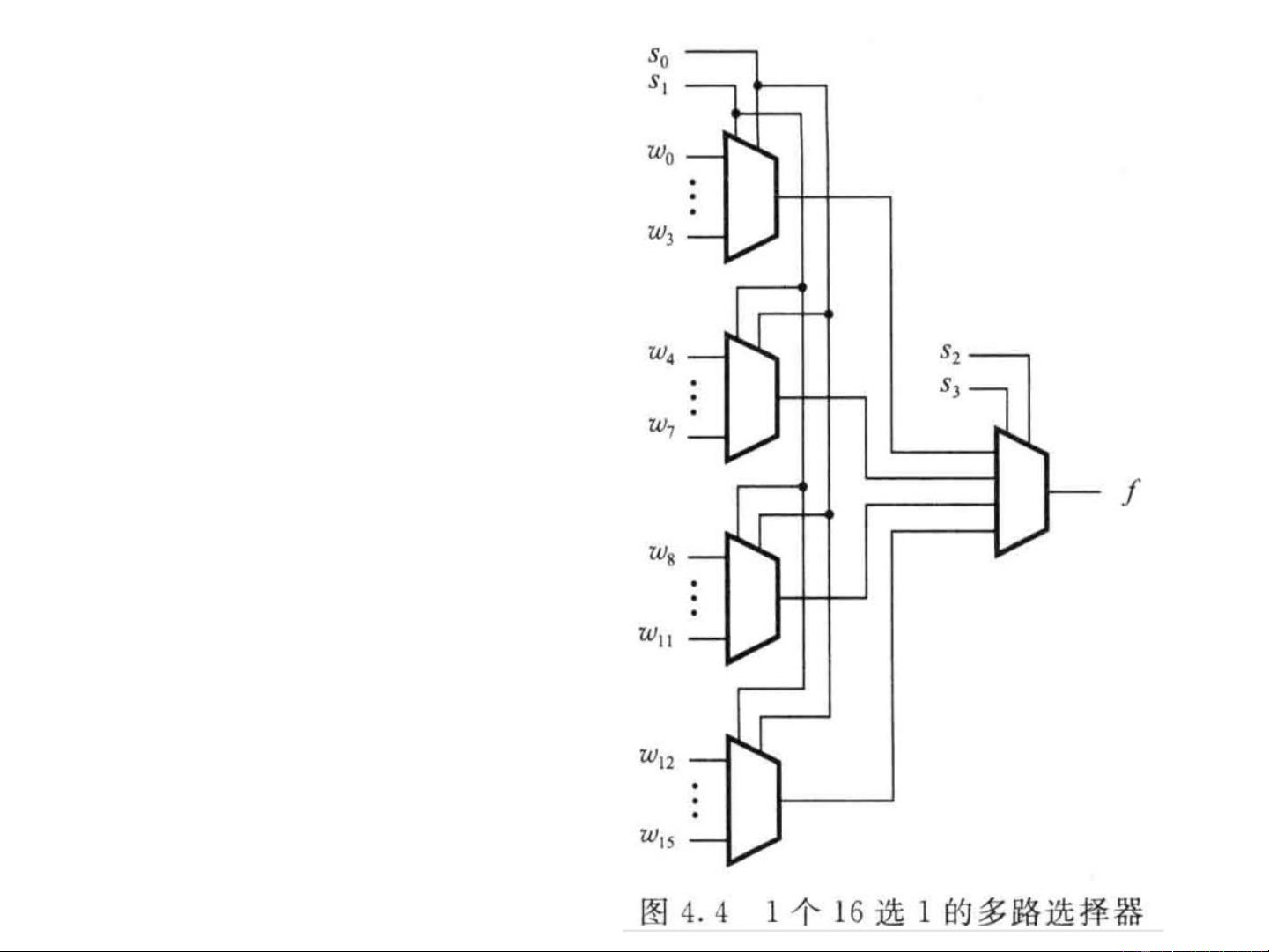

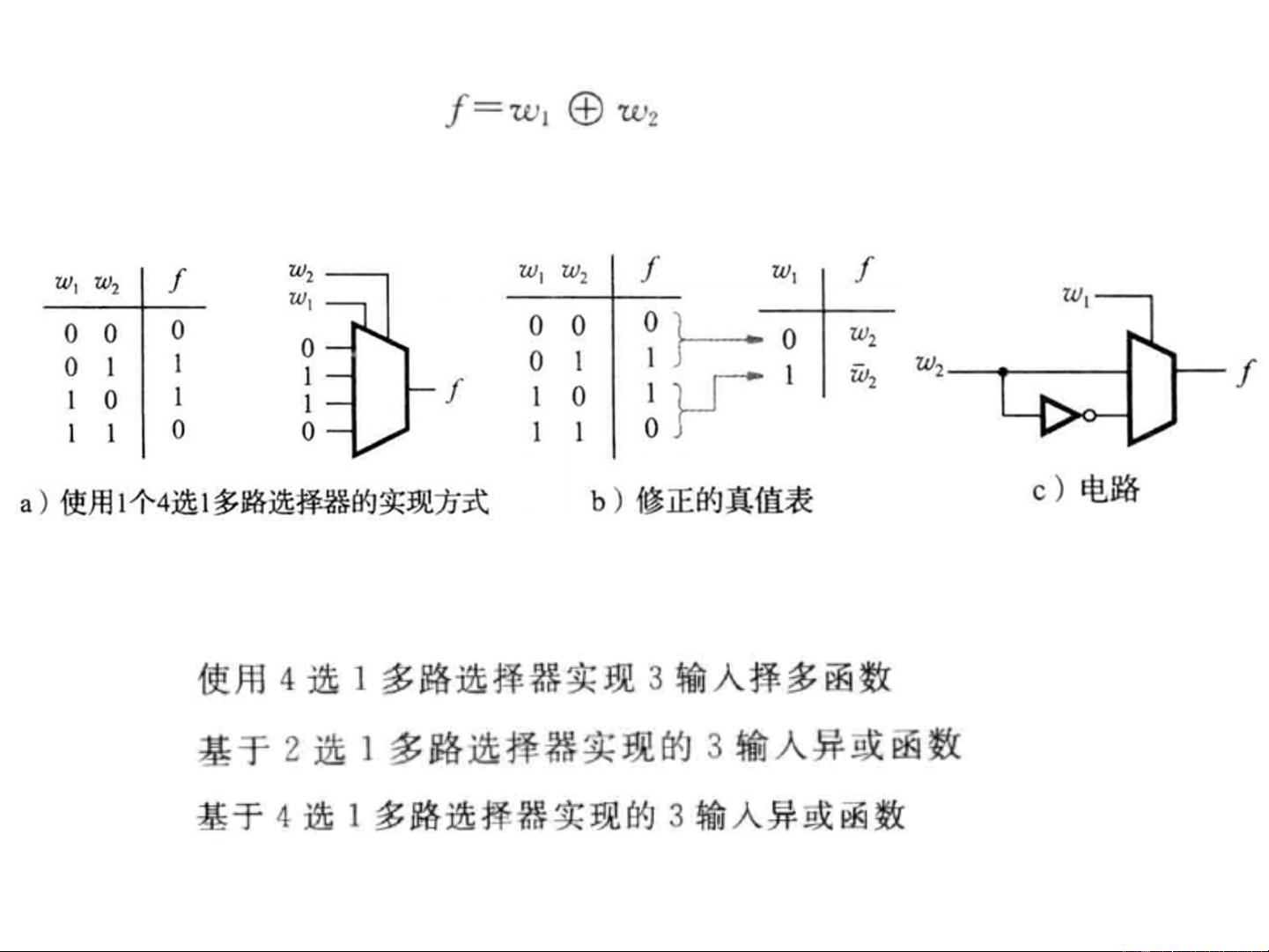

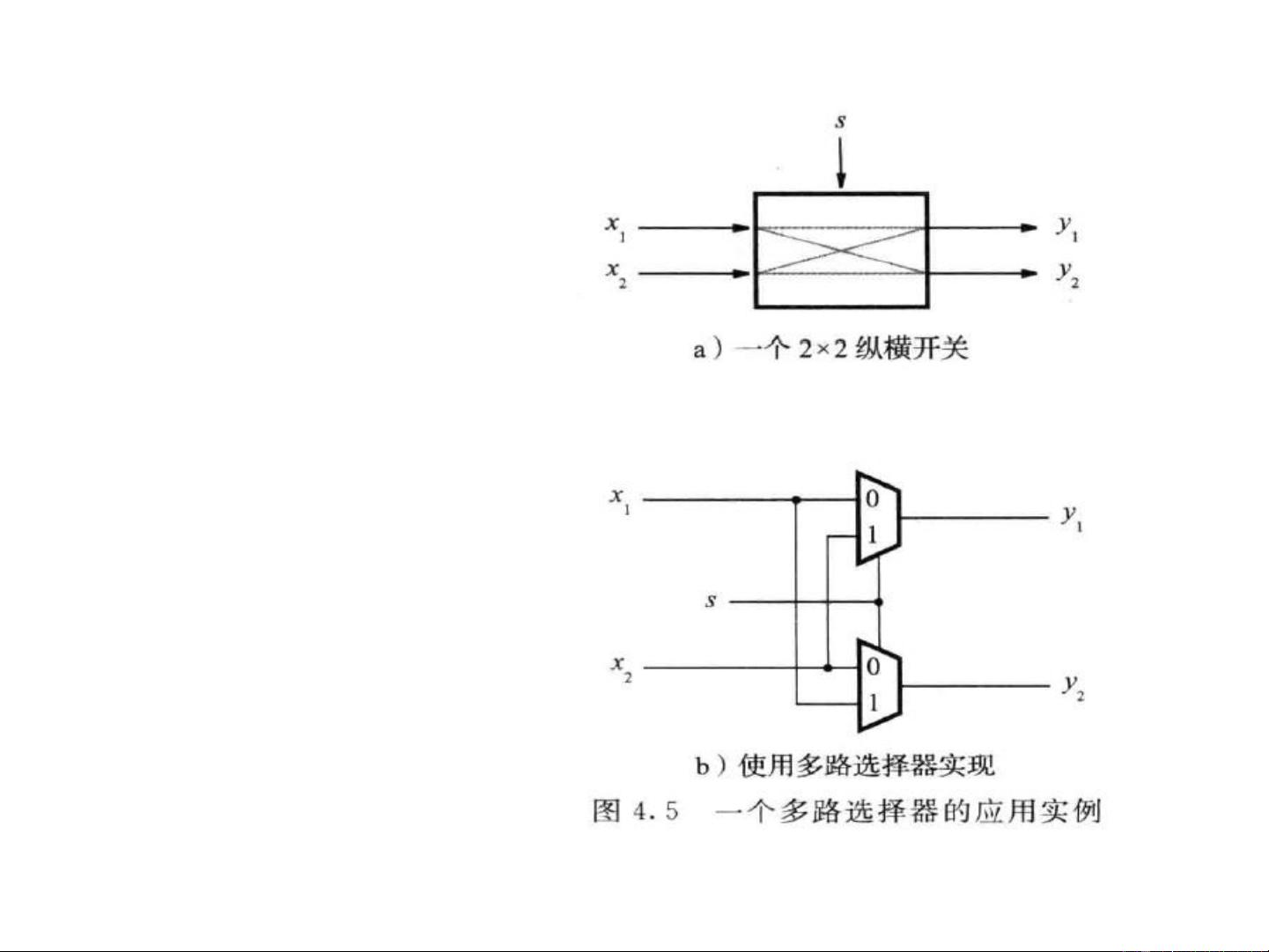

2. **多路选择器**:这是组合逻辑电路中常用的一种电路,如2选1和4选1多路选择器。2选1多路选择器通常有两种实现方式,而4选1多路选择器可以通过真值表和电路实现。多路选择器的输入端口数通常是2的幂,选择输入端的数量为log2n,其中n是数据输入的数量。

3. **逻辑函数的实现**:例如,通过香农展开定理,任何布尔函数都可以表示为多个选择器的组合。香农展开允许我们将一个复杂的逻辑函数分解为简单的余因子式,从而利用多路选择器和逻辑门实现。

4. **异或函数的实现**:异或函数是组合逻辑电路中的一个重要组成部分,可以用多路选择器和逻辑门来实现。

5. **16选1多路选择器**:通过组合五个4选1多路选择器,可以构建一个16选1的多路选择器,这展示了如何利用基础模块构建更复杂的电路。

6. **n×k纵横开关**:这是一种利用多路选择器实现逻辑交换的实例,通过选择输入信号的切换,可以实现不同输入之间的数据传输。

在实际设计中,Verilog HDL提供了丰富的结构来描述这些组合逻辑电路,如assign语句用于即时赋值,always块用于描述组合逻辑的行为。通过学习和理解这些基础知识,我们可以使用Verilog HDL进行数字系统的设计和仿真,为更高级的系统级集成打下坚实基础。

2020-05-30 上传

2018-09-30 上传

2023-07-15 上传

2024-10-17 上传

2023-04-12 上传

2023-03-23 上传

2023-06-12 上传

2023-05-25 上传

riririkakaka

- 粉丝: 0

- 资源: 3