本文档主要探讨了数字前端设计在ASIC(应用特定集成电路)开发中的关键角色,以及与FPGA(现场可编程门阵列)设计的对比。在ASIC前端设计流程中,设计师需要经历从行为级描述到物理布局的全过程,这一阶段对于决定最终芯片的性能、成本和灵活性至关重要。

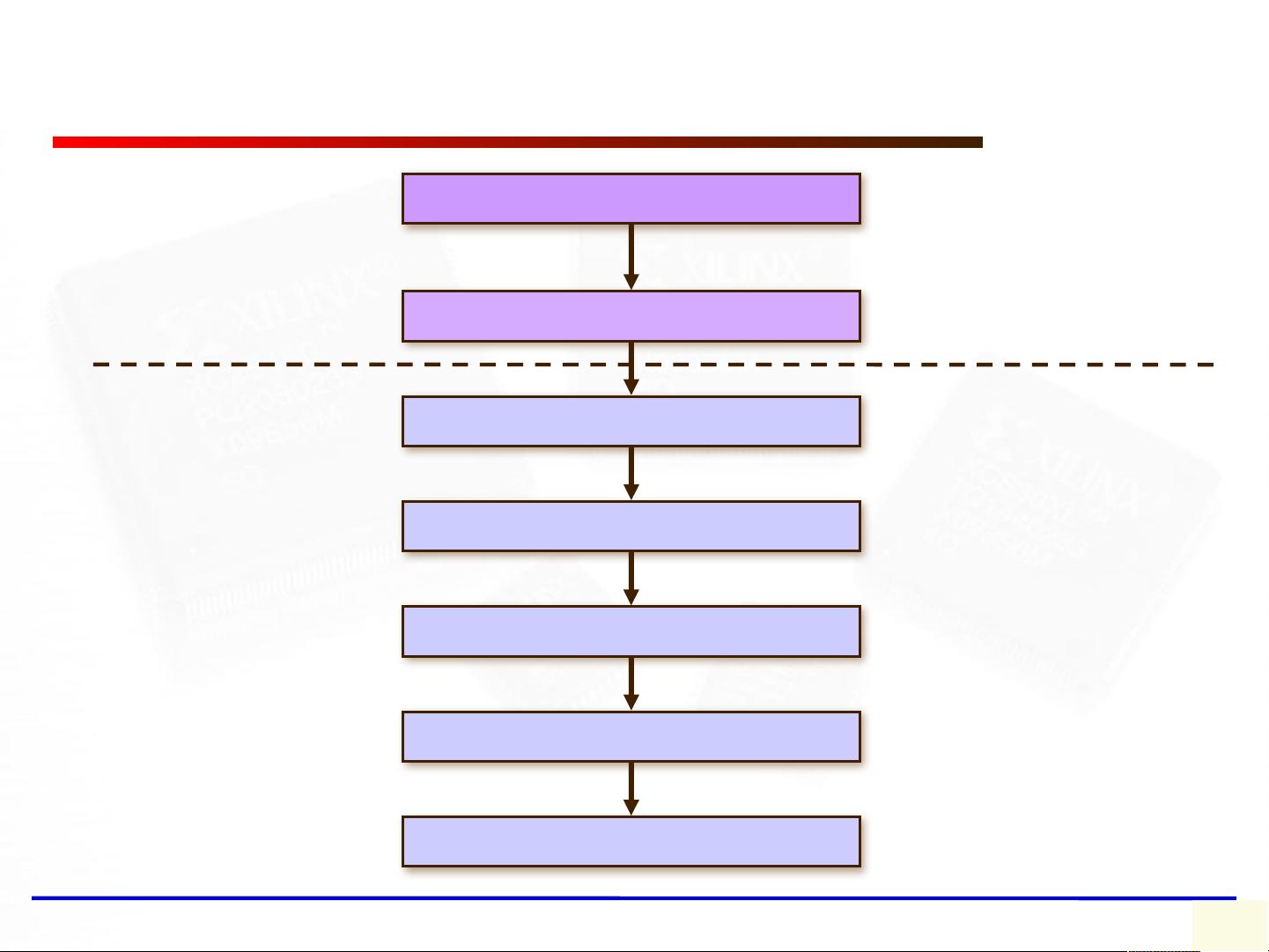

首先,让我们了解一下ASIC设计的基本流程。通常,设计过程始于行为级的设计,即用高级语言如VHDL进行描述,这涵盖了功能的逻辑实现。VHDL是一种结构化硬件描述语言,它允许工程师在抽象层次上描述系统,方便理解和调试。一旦行为级设计完成,会进入逻辑综合(synthesis)阶段,将这些高级描述转换为低级逻辑门网表,以便制造厂商能在半导体工厂中实现。

在这个过程中,critical path(关键路径)分析是一项关键任务,因为它确定了设计中的最长时间延迟路径,以确保整个系统能够满足预定的时序要求。通过优化逻辑结构和选择合适的器件技术,可以缩短关键路径,从而提高整体性能。

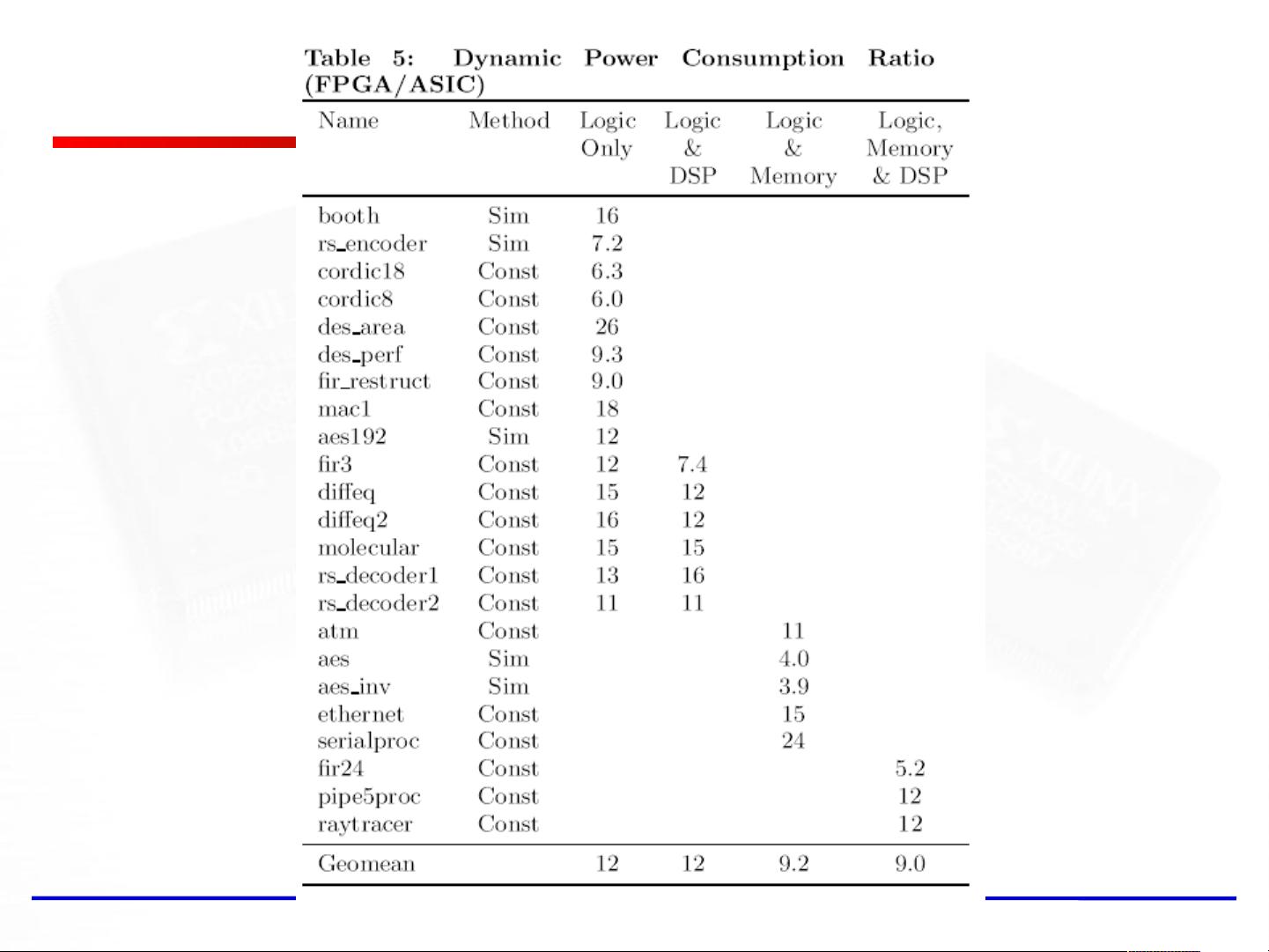

ASIC设计与FPGA的一个显著区别在于定制程度和灵活性。FPGA是可编程的,设计者可以在芯片上市后进行重新配置,这意味着它们在短时间内就能投入市场,且成本较低。然而,这通常伴随着较低的性能和更高的功耗。相比之下,ASIC是在设计阶段就决定了其功能和架构,因此在高性能、低功耗和小型化方面具有优势,但批量生产时的成本效益较高。

另一个比较点是存储器。ASIC设计可能包含本地内存(如片上RAM)和全局内存(如片外RAM),而FPGA则依赖外部存储器接口。在实际例子中,比如51x ASIC与Xilinx Virtex II 6000 FPGA的比较,ASIC由于专为特定功能设计,其面积效率往往更高,尽管FPGA在面积上可能稍大,但提供了更大的可扩展性和灵活性。

ASIC前端设计是ASIC开发的核心环节,它决定了芯片的性能、成本和潜在的商业价值。设计师必须在性能需求、成本考虑和时间压力之间找到平衡,同时熟练掌握像Synopsys这样的工具来管理这个复杂的过程。选择使用ASIC还是FPGA,取决于项目的需求,包括是否需要可重构能力、性能目标和成本效益的考量。