FPGA设计:优化时钟延时与系统稳定性

165 浏览量

更新于2024-09-01

收藏 565KB PDF 举报

"深入探讨FPGA设计中影响时钟的关键因素,包括建立时间、保持时间以及如何减小时钟延时以确保系统稳定性的方法。"

在FPGA(Field-Programmable Gate Array)设计中,时钟是至关重要的,因为它决定了系统内所有逻辑单元的同步和操作顺序。本文主要关注两个关键的时序参数——建立时间和保持时间,并阐述如何在设计中减少时钟延时以提高系统的整体稳定性。

建立时间(Tsu)是指数据需要在时钟边缘到来前稳定的时间,确保在时钟上升沿时数据已经被正确地加载到触发器中。如果数据未能在时钟边缘到来前稳定,就会导致触发器无法正确捕获数据,引发错误。而保持时间(Th)则是指数据在时钟边缘之后需要保持稳定的时间,同样是为了确保触发器在下一个时钟周期中能够正确读取数据。这两者都是确保时序正确性的基础,任何违背这两个时间要求的情况都可能导致时序违例。

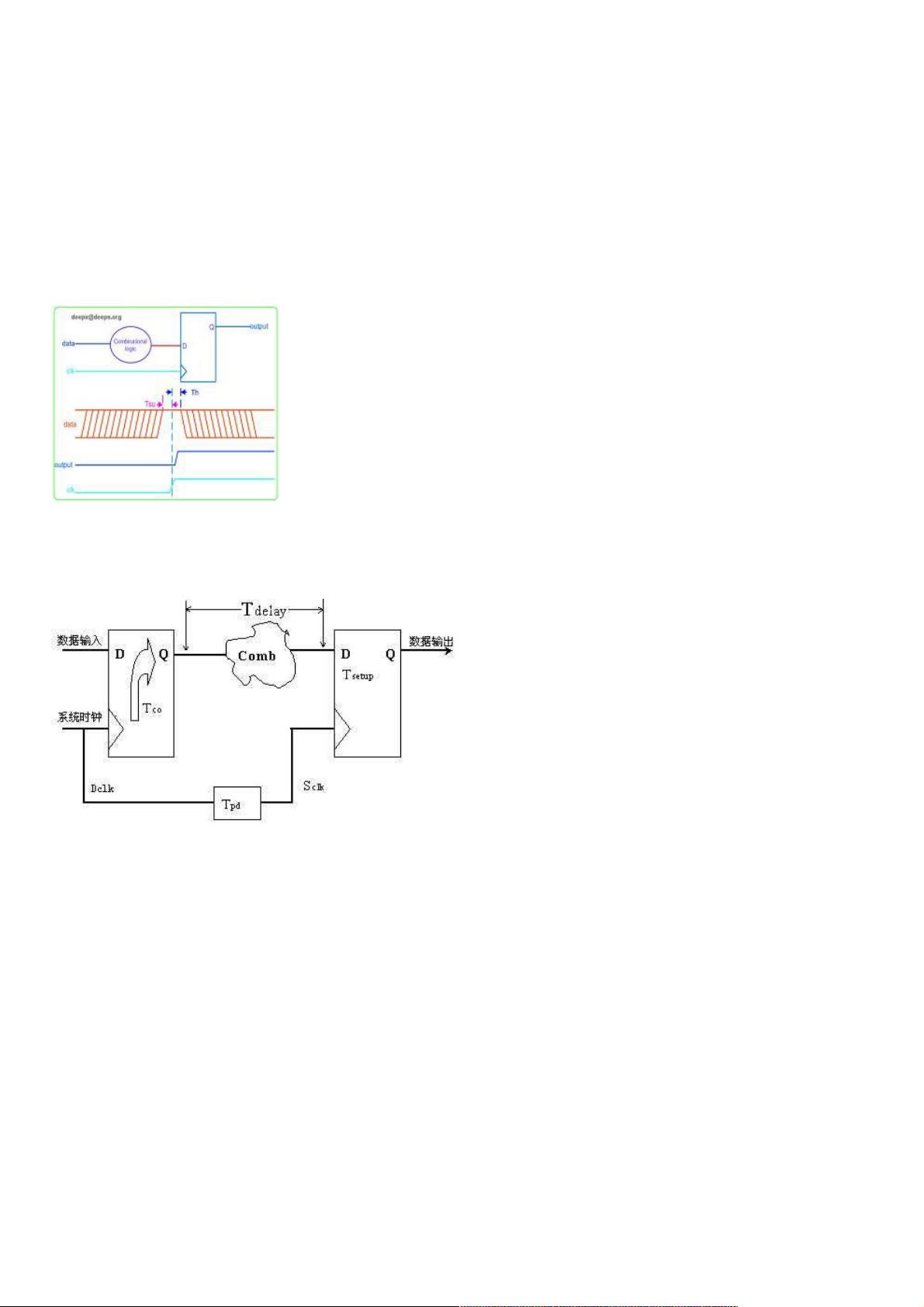

在FPGA设计中,通常会遇到包含组合逻辑和时序逻辑的模块。在这种情况下,理解并控制建立时间和保持时间至关重要。例如,图2所示的同步设计模型中,需要考虑触发器之间的数据传输路径,包括触发器的输出延迟(Tco)、组合逻辑延迟(Tdelay)、触发器的建立时间(Tsetup)以及时钟自身的延迟(Tpd)。为了保证设计的可靠性,必须确保数据在进入触发器前有足够的时间稳定(满足建立时间),并且在时钟边沿之后数据仍然保持稳定(满足保持时间)。

在计算和设计时,我们需要考虑各种延迟的最大值和最小值,例如T1max、T1min、T2max和T2min,以确保即使在最不利的情况下,系统也能正常工作。时钟周期的选择需要足够大,以容纳所有可能的延迟,但同时也要尽可能小以提高系统速度。具体来说,时钟周期Tclk应满足以下条件:

Tclk >= T1max + T2max + Tsetup + Tpd

同时,为了确保保持时间的要求,需要确保:

Tdelay <= T1min + Th - Tpd

通过这样的分析,我们可以确定系统中各个组件的时序约束,并优化设计以减小时钟延迟,从而提高设计的时序裕量和整体稳定性。

在实际的FPGA设计中,由于全局时钟网络的存在,时钟的内部延迟往往可以忽略不计。这意味着在大多数情况下,我们更关注的是数据路径的延迟,而不是时钟本身的延迟。通过合理布局、优化逻辑路径和使用高速时钟管理技术,可以有效地减小时钟的影响,确保设计的可靠性和性能。

理解和控制FPGA设计中的时钟因素,特别是建立时间和保持时间,对于创建高效、可靠的系统至关重要。通过深入分析和优化,我们可以实现更紧凑的时序约束,从而提升系统的运行速度和稳定性。

2012-03-09 上传

2010-10-01 上传

点击了解资源详情

点击了解资源详情

2013-10-07 上传

2010-08-20 上传

2012-02-25 上传

点击了解资源详情

点击了解资源详情

weixin_38569109

- 粉丝: 7

- 资源: 955

最新资源

- MapPlotter:让我们从瑞士创建3D视图

- techBlog:个人博客回购

- C,c语言可以绘制中国地图源码,c语言程序

- bash基础知识:只是一个小项目,它显示了一些基本知识os bash脚本

- 普朗克定律:我们称一个黑体的光子数。-matlab开发

- PHP-CSV-Calculator:示例PHP CLI程序可解析CSV数据并获取指定列的均值,中位数,众数和标准偏差

- openplatform-embedded:嵌入式版本的OpenPlatform

- NejmiYassine-taas-frontend-challenge

- registeringProcess

- main_sleep-timer,c语言有源码为什么编译不过,c语言程序

- Free-Fs 开源文件管理系统

- 小行星:使用html5 canvas和javascript重制经典小行星

- 产品UI设计创意网站模板

- 根据《Shell脚本编程详解》第12章节-Shell脚本编程,自己写的shell脚本。

- LeetCode

- Konntroll.github.io:我的编码项目和经验的简要说明