没有合适的资源?快使用搜索试试~ 我知道了~

首页JetsonXavierNXDataSheet_v1.5.pdf

资源详情

资源评论

资源推荐

JETSON | Xavier NX | DATA SHEET | DA-09366-001 | SUBJECT TO CHANGE | COPYRIGHT © 2014 – 2020 NVIDIA CORPORATION. ALL RIGHTS RESERVED. 1

DATA SHEET

NVIDIA Jetson Xavier NX System-on-Module

Volta GPU + Carmel CPU + 8 GB LPDDR4x + 16 GB eMMC 5.1

AI Performance

Up to 21 TOPS (INT8)

Volta GPU

384 NVIDIA

®

CUDA

®

cores | 48 Tensor cores | End-to-end lossless

compression | Tile Caching | OpenGL

®

4.6 | OpenGL ES 3.2 |

Vulkan™ 1.1

◊

| CUDA 10 | Maximum Operating Frequency: 1100

MHz

Carmel CPU

ARMv8.2 (64-bit) heterogeneous multi-processing (HMP) CPU

architecture | 3x dual-core CPU clusters (six NVIDIA Carmel

processor cores) connected by a high-performance system

coherency interconnect fabric | L3 Cache: 4 MB (shared across all

clusters)

NVIDIA Carmel (Dual-Core) Processor: L1 Cache: 128 KB L1

instruction cache (I-cache) per core; 64 KB L1 data cache (D-

cache) per core | L2 Unified Cache: 2 MB per cluster | Maximum

Operating Frequency: 1900 MHz

Audio

Dedicated programmable audio processor | ARM Cortex A9 with

NEON | PDM in/out | Industry-standard High Definition Audio (HDA)

controller provides a multi-channel audio path to the HDMI

®

interface

Memory

8 GB 128-bit LPDDR4x DRAM | Secure External Memory Access

Using TrustZone

®

Technology | System MMU | Maximum Operating

Frequency: 1600 MHz

Storage

16 GB eMMC 5.1 Flash Storage | Bus Width: 8-bit | Maximum Bus

Frequency: 200 MHz (HS400)

Networking

10/100/1000 Gigabit Ethernet | Media Access Controller (MAC)

Imaging

14 lanes (3 x4 or 6 x2) MIPI CSI-2 | D-PHY 1.2 (2.5 Gb/s per pair,

total up to 30 Gbps)

Display Controller

Two multi-mode (eDP/DP/HDMI) Serial Output Resources (SOR)

eDP 1.4a | DP 1.4 | HDMI 2.0a/b

Maximum Resolution (eDP/DP/HDMI): (up to) 3840x2160 at 60 Hz

(up to 36 bpp)

Multi-Stream HD Video and JPEG

Video Decode:

• Standards supported: H.265 (HEVC), H.264, VP9,

VP8, MPEG-4, MPEG-2, VC-1

o 2x690 MP/sec (HEVC)

o 2x 4K @ 60 (HEVC)

o 4x 4K @ 30 (HEVC)

o 12x 1080p @ 60 (HEVC)

o 32x 1080p @ 30 (HEVC)

o 16x 1080p @ 30 (H.264)

Video Encode:

• Standards supported: H.265 (HEVC), H.264, VP9

o 2x464 MP/sec (HEVC)

o 2x 4K @ 30 (HEVC)

o 6x 1080p @ 60 (HEVC)

o 14x 1080p @ 30 (HEVC)

Peripheral Interfaces

xHCI host controller with integrated PHY (up to) 1x USB 3.1, 3x

USB 2.0 | PCIe 1x1 (GEN3) + 1x4 (GEN4) | SD/MMC controller

(supporting eMMC 5.1, SD 4.0, SDHOST 4.0 and SDIO 3.0) | 3x

UART | 2x SPI | 4x I

2

C | 1x CAN | 2x I

2

S | GPIOs

Mechanical

Module Size: 69.6 mm x 45 mm | 260 pin SO-DIMM Connector

Operating Requirements

Temperature Range (T

J

)*: -25°C – 90°C | Supported Power

Modes: 10W – 15W | Power Input: 5V

Note: Refer to the Software Features section of the latest L4T Development Guide for a list of supported features; all features may not be

available.

◊

Product is based on a published Khronos Specification and is expected to pass the Khronos Conformance Process. Current conformance status

can be found at www.khronos.org/conformance

.

* See the Jetson Xavier NX Thermal Design Guide for details

Jetson Xavier NX System-on-Module

Volta GPU + Carmel CPU + 8GB LPDDR4x + 16GB eMMC 5.1

JETSON | Xavier NX | DATA SHEET | DA-09366-001 | SUBJECT TO CHANGE | COPYRIGHT © 2014 – 2020 NVIDIA CORPORATION. ALL RIGHTS RESERVED. 2

Revision History

Version

Date

Description

V1.0 November 6, 2019 Initial release.

V1.1 February 1, 2020 Updated:

• PCIE0_XXX pins from Ctrl #0 to Ctrl #5 under PCIe Pin description in Table 9: PCIe

Pin Descriptions

• PCIE1_XXX pins from Ctrl #1 to Ctrl #4 under PCIe Pin description in Table 9: PCIe

Pin Descriptions

• Pulse Width Modulator (PWM) to reflect four outputs instead of eight outputs

• SHUTDOWN_REQ* and SYS_RESET* pull up information in Table 21: Power and

System Control Pins

• Table 29: Absolute Maximum Ratings to include the Mounting Force parameter.

• Mechanical Drawing

V1.2 February 24, 2020 Added:

• Tolerance information for Mechanical Drawing

V1.3 April 21, 2020 Added:

• PMIC_BBAT to reflect RTC accuracy

• SoC height for the Mechanical Drawing

• Table 30: Jetson NX Reliability Report table

• Gen4 information to PCI Express (PCIe) section

V1.4 June 25, 2020 Added:

• Programmable Vision Accelerator (PVA) section to Functional Overview

Updated:

• Table 6: Video Decoder Standards table

V1.5 July 06, 2020 Added:

• Overcurrent Throttling section to Power and System Management

Jetson Xavier NX System-on-Module

Volta GPU + Carmel CPU + 8GB LPDDR4x + 16GB eMMC 5.1

JETSON | Xavier NX | DATA SHEET | DA-09366-001 | SUBJECT TO CHANGE | COPYRIGHT © 2014 – 2020 NVIDIA CORPORATION. ALL RIGHTS RESERVED. 3

Table of Contents

1.0 Functional Overview 5

Volta GPU .................................................................................................................................................... 5

Carmel CPU Complex ................................................................................................................................. 6

Memory Subsystem ..................................................................................................................................... 6

Memory ........................................................................................................................................................ 7

Video Input Interfaces .................................................................................................................................. 7

1.5.1 MIPI Camera Serial Interface (CSI) ............................................................................................... 7

1.5.2 Video Input (VI) ............................................................................................................................ 10

1.5.3 Image Signal Processor (ISP) ...................................................................................................... 10

Display Controller ...................................................................................................................................... 10

1.6.1 HDMI and DisplayPort Interfaces ................................................................................................. 12

1.6.2 Embedded DisplayPort (eDP) ...................................................................................................... 13

High-Definition Audio-Video Subsystem ................................................................................................... 14

1.7.1 Multi-Standard Video Decoder ..................................................................................................... 14

1.7.2 Multi-Standard Video Encoder ..................................................................................................... 15

1.7.3 JPEG Processing Block ............................................................................................................... 16

1.7.4 Video Image Compositor (VIC) .................................................................................................... 16

1.7.5 Audio Processing Engine (APE) .................................................................................................. 17

1.7.6 High Definition Audio (HDA) ........................................................................................................ 17

Interface Descriptions ................................................................................................................................ 17

1.8.1 SD/eMMC ..................................................................................................................................... 18

1.8.2 Universal Serial Bus (USB) .......................................................................................................... 18

1.8.3 PCI Express (PCIe) ...................................................................................................................... 19

1.8.4 Serial Peripheral Interface (SPI) .................................................................................................. 21

1.8.5 Universal Asynchronous Receiver/Transmitter (UART) .............................................................. 23

1.8.6 Controller Area Network (CAN) .................................................................................................... 23

1.8.7 Inter-Chip Communication (I

2

C) ................................................................................................... 24

1.8.8 Inter-IC Sound (I

2

S) ...................................................................................................................... 25

1.8.9 Gigabit Ethernet ........................................................................................................................... 26

1.8.10 Fan ............................................................................................................................................. 27

1.8.11 Pulse Width Modulator (PWM) ................................................................................................... 27

Deep Learning Accelerator (DLA) ............................................................................................................. 28

Programmable Vision Accelerator (PVA) ................................................................................................ 29

2.0 Power and System Management 30

Power Rails................................................................................................................................................ 30

Power Domains/Islands ............................................................................................................................. 31

Power Management Controller (PMC) ...................................................................................................... 31

Resets ........................................................................................................................................................ 31

PMIC_BBATT ............................................................................................................................................ 31

Power Sequencing .................................................................................................................................... 31

2.6.1 Power Up ..................................................................................................................................... 32

2.6.2 Power Down ................................................................................................................................. 32

Power States ............................................................................................................................................. 32

2.7.1 ON State ...................................................................................................................................... 33

2.7.2 OFF State ..................................................................................................................................... 33

2.7.3 SLEEP State ................................................................................................................................ 33

Thermal and Power Monitoring ................................................................................................................. 34

Overcurrent Throttling ................................................................................................................................ 34

Jetson Xavier NX System-on-Module

Volta GPU + Carmel CPU + 8GB LPDDR4x + 16GB eMMC 5.1

JETSON | Xavier NX | DATA SHEET | DA-09366-001 | SUBJECT TO CHANGE | COPYRIGHT © 2014 – 2020 NVIDIA CORPORATION. ALL RIGHTS RESERVED. 4

3.0 Pin Definitions 35

Power-on Reset Behavior .......................................................................................................................... 35

Sleep Behavior .......................................................................................................................................... 35

GPIO .......................................................................................................................................................... 36

Pin List ....................................................................................................................................................... 37

4.0 DC Characteristics 38

Operating and Absolute Maximum Ratings ............................................................................................... 38

Digital Logic ............................................................................................................................................... 39

5.0 Package Drawing and Dimensions 41

Jetson Xavier NX System-on-Module

Volta GPU + Carmel CPU + 8GB LPDDR4x + 16GB eMMC 5.1

JETSON | Xavier NX | DATA SHEET | DA-09366-001 | SUBJECT TO CHANGE | COPYRIGHT © 2014 – 2020 NVIDIA CORPORATION. ALL RIGHTS RESERVED. 5

1.0 Functional Overview

NVIDIA® Jetson Xavier™ NX brings AI supercomputer performance to the edge in a compact system-on-module (SOM) that’s

smaller than a credit card. Jetson Xavier NX is built around a low-power version of the NVIDIA Xavier SoC, combining the

NVIDIA Volta™ GPU architecture with 64-bit operating capability, integrated advanced multi-function video and image

processing, and NVIDIA Deep Learning Accelerators.

Compute performance up to 14 TOPS (at 10W) or 21 TOPS (at 15W) enables the Jetson Xavier NX to run multiple neural

networks in parallel and process data from multiple high-resolution sensors simultaneously. It also offers a unique combination

of performance and power advantages with a rich set of I/Os, from high-speed CSI and PCIe to low-speed I

2

Cs and GPIOs,

allowing embedded and edge computing devices that demand increased performance but are constrained by size, weight, and

power budgets.

Volta GPU

The Graphics Processing Cluster (GPC) is a dedicated hardware block for computing, rasterization, shading, and texturing of

most of the GPU’s core graphics functions. The GPC is comprised of Texture Processing Clusters (TPC), with each TPC

containing two Streaming Multiprocessor (SM) units, and a Raster Engine. The SM unit creates, manages, schedules, and

executes instructions from many threads in parallel. Raster operators (ROPs) continue to be aligned with L2 cache slices and

memory controllers. The SM geometry and pixel processing performance make it highly suitable for rendering advanced user

interfaces, while the efficiency of the Volta GPU enables this performance on devices with power-limited environments.

Each SM is partitioned into four separate processing blocks (referred to as SMPs), each SMP contains its own instruction

buffer, scheduler, CUDA cores, and Tensor cores. Inside each SMP, CUDA cores perform pixel/vertex/geometry shading and

physics/compute calculations, and each Tensor core provides a 4x4x4 matrix processing array to perform mixed-precision

fused multiply-add (FMA) mathematical operations. Texture units perform texture filtering and load/store units fetch and save

data to memory. Special Function Units (SFUs) handle transcendental and graphics interpolation instructions. Finally, the

PolyMorph Engine handles vertex fetch, tessellation, viewport transform, attribute setup, and stream output.

Features:

• End-to-end lossless compression

• Tile Caching

• Support for OpenGL 4.6, OpenGL ES 3.2, Vulkan 1.1

• Adaptive Scalable Texture Compression (ASTC) LDR profile supported

• CUDA support

• Iterated blend, ROP OpenGL-ES blend modes

• 2D BLIT from 3D class avoids channel switch

• 2D color compression

• Constant color render SM bypass

• 2x, 4x, 8x MSAA with color and Z compression

• Non-power of 2D and 3D textures, FP16 texture filtering

• FP16 shader support

• Geometry and Vertex attribute instancing

• Parallel pixel processing

• Early-z reject: Fast rejection of occluded pixels acts as multiplier on pixel shader and texture performance while

saving power and bandwidth

• Video protection region

• Power saving: Multiple levels of clock gating for linear scaling of power

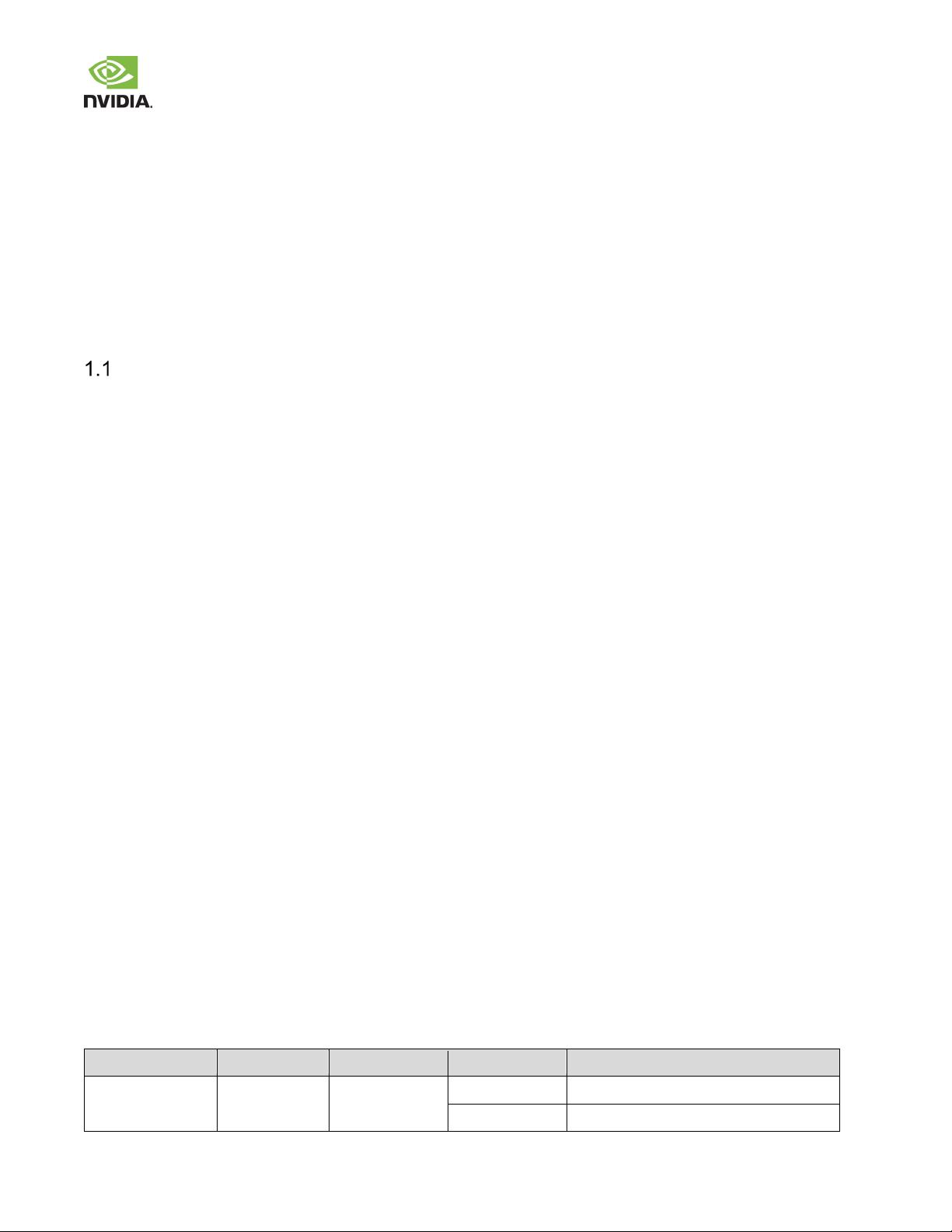

Table 1: GPU Operation

Module

CUDA Cores

Tensor Cores

Power Mode

Operating

Frequency per Core (up to)

Jetson Xavier NX 384 48 10W 800 MHz

15W 1100 MHz

剩余41页未读,继续阅读

chu83866

- 粉丝: 0

- 资源: 25

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0