10G以太网光接口的以太网光接口的FPGA实现实现

该设计能够有效、正确地实现10 Gb/s的高速数据传输,并且传输数据的误码均未超过阈值,进而证明了该设计

系统的可靠性和稳定性。采用FPGA中的RocketIO接口来设计10 Gb/s速率的光纤传输,极大地增强了光纤传输

设计的灵活性,通过修改FPGA代码即可用于高速信号传输的多种情况和场合。

1 概述概述

随着人们对通信信息的充裕性、及时性和便捷性的要求越来越高,能够随时随地、方便而及时地获取所需信息,变得越来

越重要。2002年,IEEE通过了10 Gb/s速率的

2009年1月国内3G牌照正式发放,标志着我国3G时代的到来。为了适应移动通信的发展,各大运营商展开了大规模的3G

移动通信网络建设;而移动通信网络建设的核心是基站建设,其成本也是最高的。此外,基站的性能好坏也是移动通信服务质

量的决定因素。所以,运营商在不断寻求新的方式以提高通信服务质量的同时,也在努力降低通信网络建设的成本。分布式基

站具有成本低、环境适应性强、工程建设方便的优势,从而代表了下一代基站的的基本走向。

分布式基站的核心是把传统的宏基站基带处理单元BBU和射频拉远单元RRU分离,二者通过光纤连接。网络部署

时,BBU集中置放,其容量较大,实现了容量和覆盖之间的转换;RRU置于天面,其环境适应性强,并且多个RRU可以共享

BBU基带资源,节省基带投资。为了实现基站和直放站之间更有效的互通,爱立信、华为、NEC、北电网络及西门子五大集

团合力制定了CPRI接口协议。该接口的标准协议成为了一个公共的可用指标之一。

2 CPRI协议简述协议简述[2]

CPRI(Common Public Radio Interface)协议定义了两个协议层——物理层(L1)和数据链路层(L2)。CPRI接口是

位于REC(Radio Equipment Contorl,无线设备控制)和RE(Radio Equipment,无线设备)之间以及两个RE之间的内部数据化接

口;有3种不同的信息流(用户平台数据流SAPIQ、控制和管理平台数据流SAPCM和同步平台数据流SAPS)经过CPRI接口

传输。

3

3.1 基本方案基本方案

用FPGA实现CPRI协议传输具有以下2种方案。

(1) 方案一

RocketIO

该方案的优点是电路板结构紧凑,有利于PCB板布线,且具有很高的系统抗干扰能力。此外,参数设置方便,有利于系

统调试。每块Virtex5型的FPGA芯片中含有多个GTP收发器,可以通过运用4个GTP来实现10 Gb/s的高速率传输。每一个

GTP核中包含一个接收链路和一个发送链路[45]。

(2) 方案二

利用串并转换的专用芯片,如TI公司生产的TLK2501、美国国家半导体设计的串行/解串器SCAN25100[67]等。其

中,SCAN25100的功能最完善,其具备8b/10b编解码、高速串并转换、锁定检测、CPRI信号和帧丢失检测等功能。该芯片具

有高精度延时校准测量电路、时钟管理以及信号调节功能。

3.2 具体实现具体实现

SCAN25100支持的传输速率为2.4576 Gb/s、1.2288 Gb/s和0.6144 Gb/s;TLK2501支持的传输速率为1.5~2.5 Gb/s。

如果采用专用串并转换芯片,为了实现10 Gb/s的速率,必须采用4块专用芯片,从而加大了PCB板的布线难度和电路板面

积,不利于电路设计。

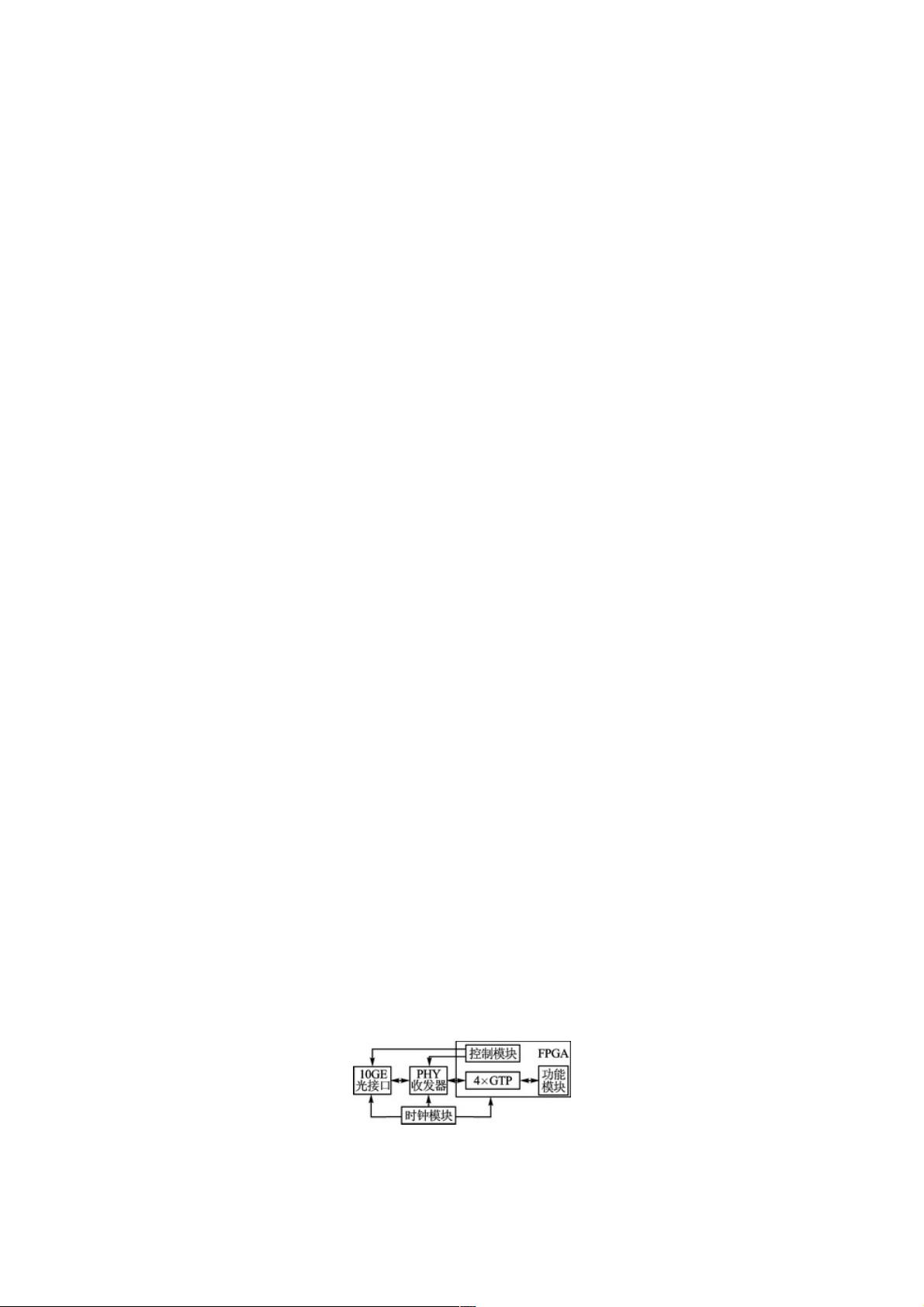

图1 以太网

本文采取第一种设计方案完成10 Gb/s的CPRI高速数据传输设计。如图1所示,以太网光接口包括4部分:10GE光接口、

PHY收发器、时钟模块、FPGA。其中,10GE光接口和PHY收发器是实现该10G以太网光接口的硬件设备;FPGA部分是本

文设计的核心,采用Xilinx公司的 Virtex6芯片。