Aardvark I2C/SPI 主机适配器用户手册:工业级串行通信开发

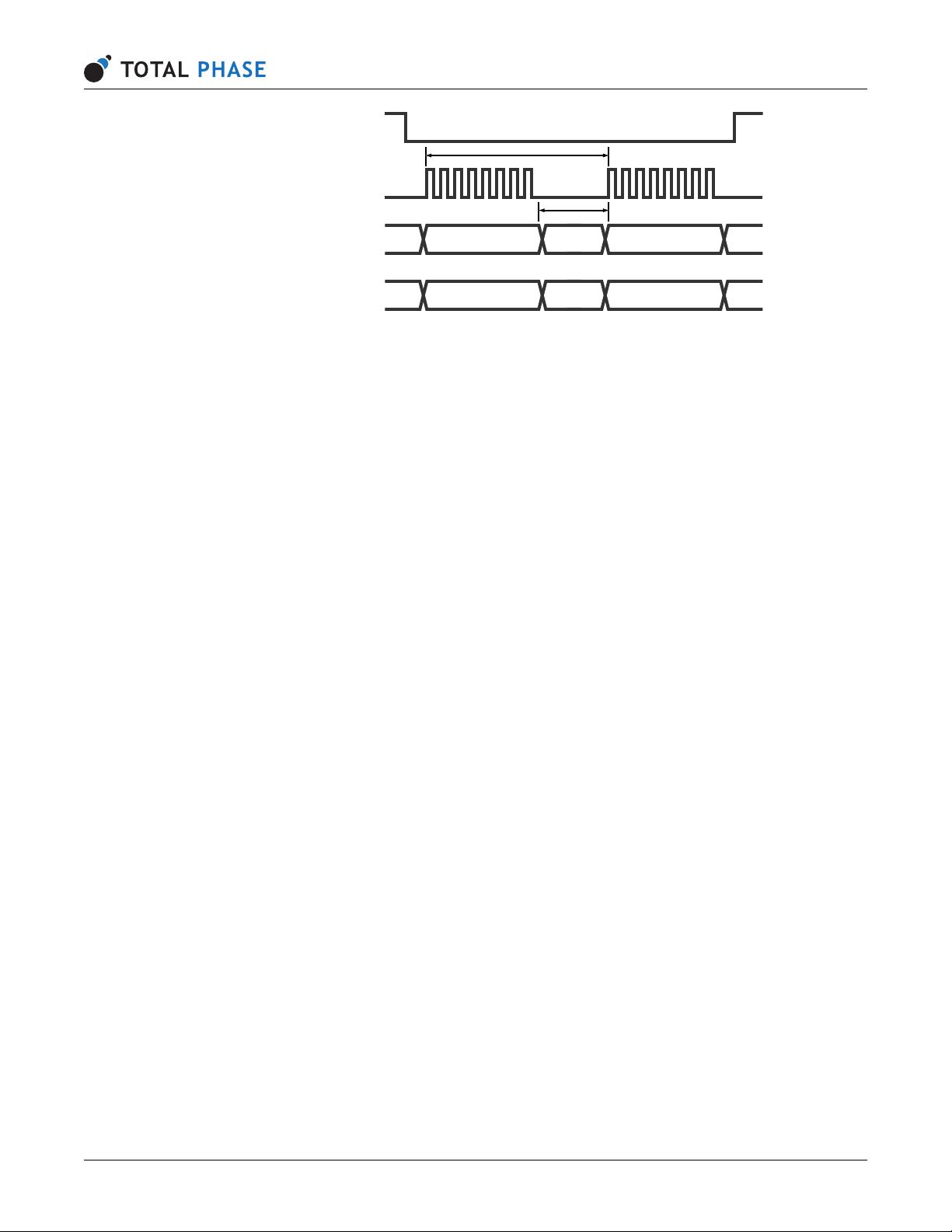

"Aardvark I2C/SPI主机适配器是一款强大的工具,它使得开发者能够在Windows、Linux或Mac OS X系统上与各种嵌入式系统进行交互,支持I2C和SPI通信协议,广泛应用于工业、汽车、消费和医疗电子等领域的开发和芯片编程。" Aardvark I2C/SPI主机适配器是为开发人员设计的一种接口设备,它提供了对I2C和SPI串行通信协议的全面支持。这个设备的主要特点包括: 1. **I2C功能**: - 支持标准模式(100kbps)和快速模式(400kbps)。 - 可变比特率,范围从1kbps到800kbps。 - 传输速率接近理论最大值,确保高效的数据传输。 - 支持主控发送和接收,以及异步从设备发送和接收。 - 包括重复启动、10位地址和组合格式等功能,提高了灵活性。 2. **SPI功能**: - 提供4线SPI串行通信协议,支持高达8Mbps的主设备信号速率和4Mbps的从设备信号速率。 - 全双工主控发送/接收,实现双向通信。 - 异步从设备发送/接收,适应不同设备需求。 - 可配置的从选择极性,适用于主模式下的不同硬件配置。 3. **GPIO(通用输入/输出)功能**: - 在I2C和SPI引脚上提供通用信号,适应多样化的硬件连接需求。 - 内部缓存GPIO配置,确保配置的稳定性和快速响应。 4. **I2C监控**: - 非侵入式地记录I2C总线上的通信流量,便于调试和分析。 - 支持高达125kHz的总线速度,覆盖大部分应用场景。 5. **USB主机通信**: - 通过USB接口实现高达3Mbps的数据传输速率至主机PC。 - 直接由USB供电,省去了额外的电源适配器。 - 报告为全速设备(12Mbps)给USB2.0主机,确保兼容性和性能。 6. **软件API**: - 兼容Linux和Windows操作系统,易于集成到各类应用中。 - 提供简洁的应用程序接口,简化开发过程。 7. **固件升级**: - 通过USB接口进行现场升级,方便设备的更新和优化。 - 错误检查机制防止升级过程中可能出现的问题,保障设备稳定性。 Aardvark I2C/SPI主机适配器的这些特性使其成为嵌入式系统开发者的得力助手,无论是进行原型验证、设备测试还是系统集成,都能提供可靠且灵活的支持。

剩余62页未读,继续阅读

- 粉丝: 4

- 资源: 5

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 谷歌文件系统下的实用网络编码技术在分布式存储中的应用

- 跨国媒体对南亚农村社会的影响:以斯里兰卡案例的社会学分析

- RFM2g接口驱动操作手册:API与命令行指南

- 基于裸手的大数据自然人机交互关键算法研究

- ABAQUS下无人机机翼有限元分析与局部设计研究

- TCL基础教程:语法、变量与操作详解

- FPGA与数字前端面试题集锦:流程、设计与Verilog应用

- 2022全球互联网技术人才前瞻:元宇宙驱动下的创新与挑战

- 碳排放权交易实战手册(第二版):设计与实施指南

- 2022新经济新职业洞察:科技驱动下的百景变革

- 红外与可见光人脸融合识别技术探究

- NXP88W8977:2.4/5 GHz 双频 Wi-Fi4 + Bluetooth 5.2 合体芯片

- NXP88W8987:集成2.4/5GHz Wi-Fi 5与蓝牙5.2的单芯片解决方案

- TPA3116D2DADR: 单声道数字放大器驱动高达50W功率

- TPA3255-Q1:315W车载A/D类音频放大器,高保真、宽频设计

- 42V 输入 5A 降压稳压器 TPS54540B-Q1 的特点和应用

信息提交成功

信息提交成功