UVM验证方法学实战指南

需积分: 23 122 浏览量

更新于2023-05-17

1

收藏 6.26MB PDF 举报

"UVM Cookbook - 完整的验证学院指南"

这份资源是Mentor Graphics验证方法团队编写的在线方法学文档,旨在提供UVM(Universal Verification Methodology)的详细指导。UVM是一种广泛应用于系统级验证的工业标准框架,它基于SystemVerilog语言,用于构建可复用和可扩展的验证环境。

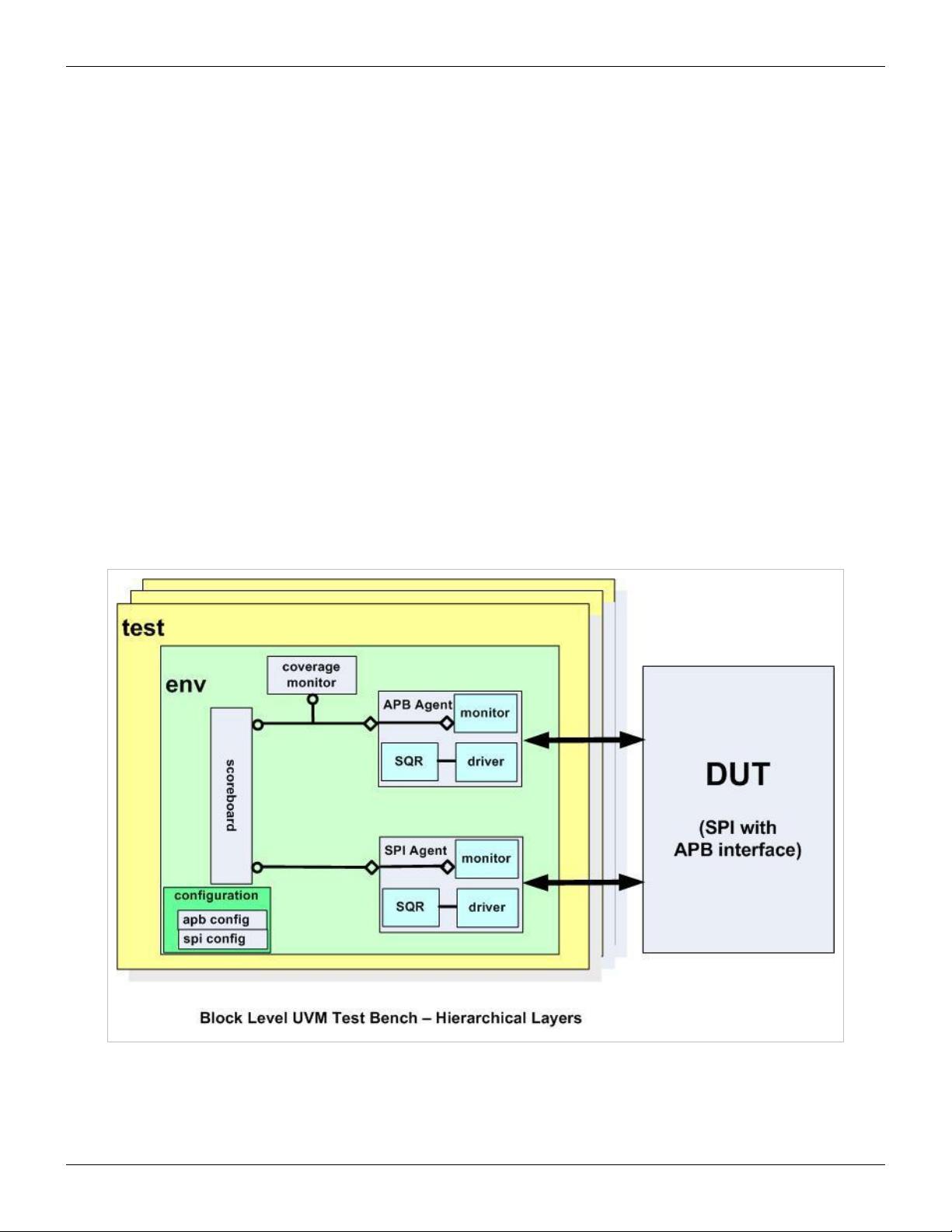

**测试平台架构**

测试平台是验证工作中的核心部分,包括三个主要层次:**块级**、**集成级**和**系统级**。在块级,关注的是设计的基本单元;集成级则处理不同块之间的接口和交互;系统级验证则是将所有块组合在一起,确保它们在整个系统内的协同工作。

**组件和代理**

在UVM中,**组件(Component)**是基本的构建模块,可以是验证环境的一部分,如激励生成器、监视器或断言。**代理(Agent)**则封装了组件,提供了与DUT(Design Under Test)接口的连接,通常包括驱动、监视器和代理控制器。

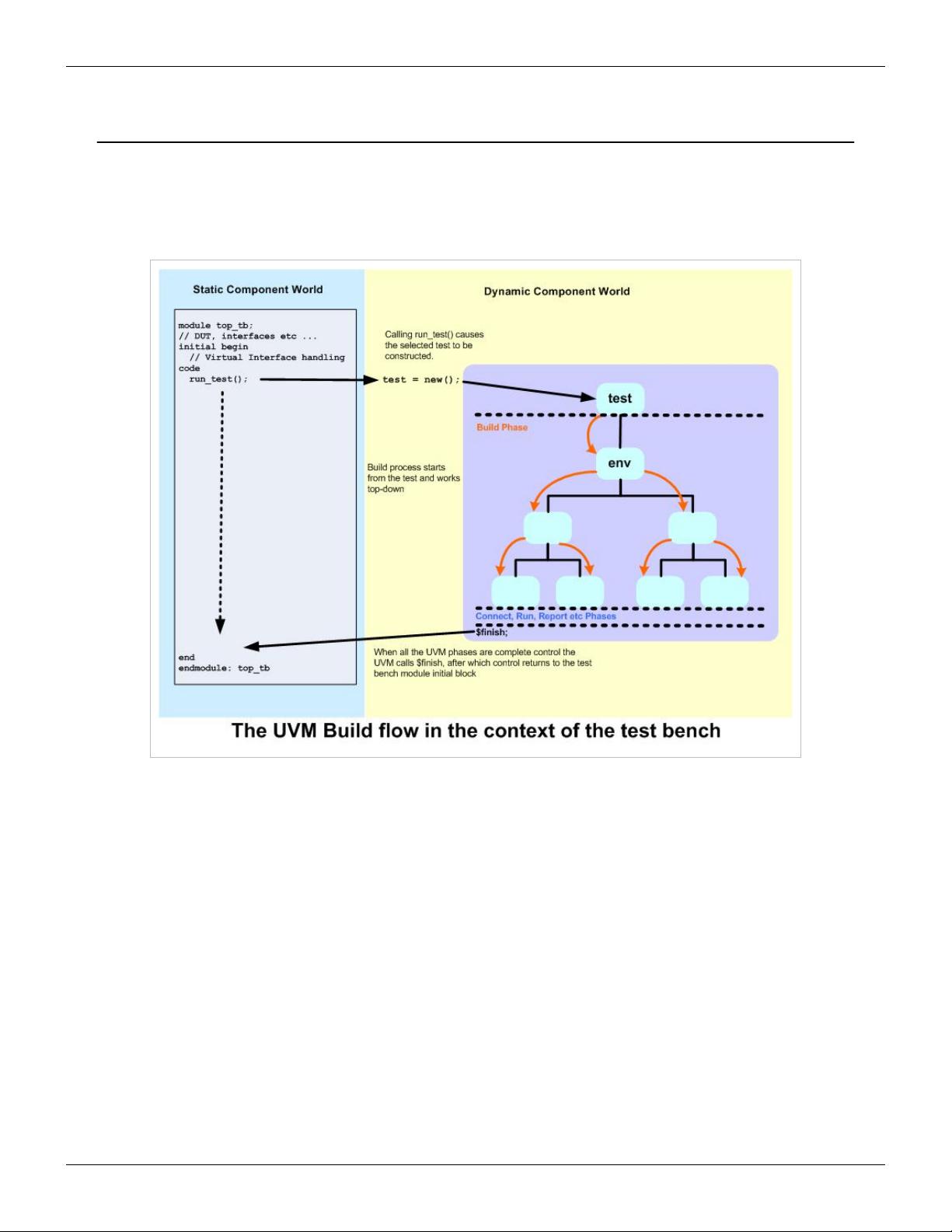

**阶段(Phasing)**

**阶段**是UVM的一个重要特性,它允许测试平台的不同部分在执行过程中按特定顺序进行操作。通过阶段,我们可以控制验证行为,如初始化、运行测试、清理等。

**工厂(Factory)**

UVM的**工厂(Factory)**机制用于动态地创建和配置组件实例。它允许用户通过覆盖默认的行为来定制组件类型,这对于实现可配置的验证环境至关重要。

**SystemVerilog包**

**SystemVerilog包**是用来组织和重用代码的结构,UVM库包含了一系列的预定义包,如uvm_pkg,其中包含了UVM类和函数。用户可以创建自己的包来封装特定的环境或组件。

**与DUT接口的连接**

在连接到DUT接口时,可以采用多种**SystemVerilog技术**,包括虚拟接口、抽象类和具体类的连接。虚拟接口提供了一种在不暴露底层实现细节的情况下定义接口的方法,抽象类则允许定义非完全实现的接口,而具体类是这些接口的具体实现。

**配置**

**配置**是UVM的关键特性之一,允许动态地设置组件属性,如参数、实例化和关联。配置数据库(Config DB)是实现这种动态配置的主要工具,它可以跨组件层次进行设置。

**参数化测试**

**参数化测试**允许根据不同的输入参数运行相同的测试,增强了测试覆盖率和效率。

**双顶结构(DualTop)**

在某些复杂的验证场景中,可能需要使用**双顶结构(DualTop)**,即拥有两个顶层组件,一个用于设计,另一个用于验证,以解决设计和验证之间的依赖问题。

**协议模块**

**协议模块**是对特定通信协议的模型,如AHB、AXI等。它们提供了对协议规则的精确模拟,便于验证设计是否符合协议规范。

这份UVM Cookbook详尽地介绍了如何构建和配置UVM验证环境,涵盖了从基础概念到高级技巧的各个方面,对于任何想要深入理解和应用UVM的人来说都是宝贵的参考资料。

2021-05-19 上传

2023-06-20 上传

2024-04-25 上传

2023-05-14 上传

2023-10-24 上传

steed_sindy

- 粉丝: 0

- 资源: 2

最新资源

- AirKiss技术详解:无线传递信息与智能家居连接

- Hibernate主键生成策略详解

- 操作系统实验:位示图法管理磁盘空闲空间

- JSON详解:数据交换的主流格式

- Win7安装Ubuntu双系统详细指南

- FPGA内部结构与工作原理探索

- 信用评分模型解析:WOE、IV与ROC

- 使用LVS+Keepalived构建高可用负载均衡集群

- 微信小程序驱动餐饮与服装业创新转型:便捷管理与低成本优势

- 机器学习入门指南:从基础到进阶

- 解决Win7 IIS配置错误500.22与0x80070032

- SQL-DFS:优化HDFS小文件存储的解决方案

- Hadoop、Hbase、Spark环境部署与主机配置详解

- Kisso:加密会话Cookie实现的单点登录SSO

- OpenCV读取与拼接多幅图像教程

- QT实战:轻松生成与解析JSON数据