Intel缓存分配技术实验探索

16 浏览量

更新于2024-07-14

收藏 960KB PDF 举报

"这篇资源是Pawel Szostek在2015年HTCCC会议上关于Intel缓存分配技术的一些实验展示。主要内容涉及现代计算机架构中的缓存机制、Intel的Cache Allocation Technology(CAT)以及Cache Monitoring Technology(CMT)的工作原理和应用。"

在现代计算机科学中,缓存是提升内存访问速度的关键技术。缓存存储数据以备后续使用,只有当数据被重复利用时,缓存才能发挥其优势。对于流式应用,如果数据不被重用,缓存则无法提供性能提升。在现代x86架构中,通常有三级缓存——L1数据缓存(L1D)、L1指令缓存(L1I)、L2缓存和L3缓存(也称为Last Level Cache,LLC)。L3缓存是多核处理器中所有核心共享的,而L1和L2缓存则是包含关系,意味着所有更高级别的缓存都包含低级别缓存的所有数据。

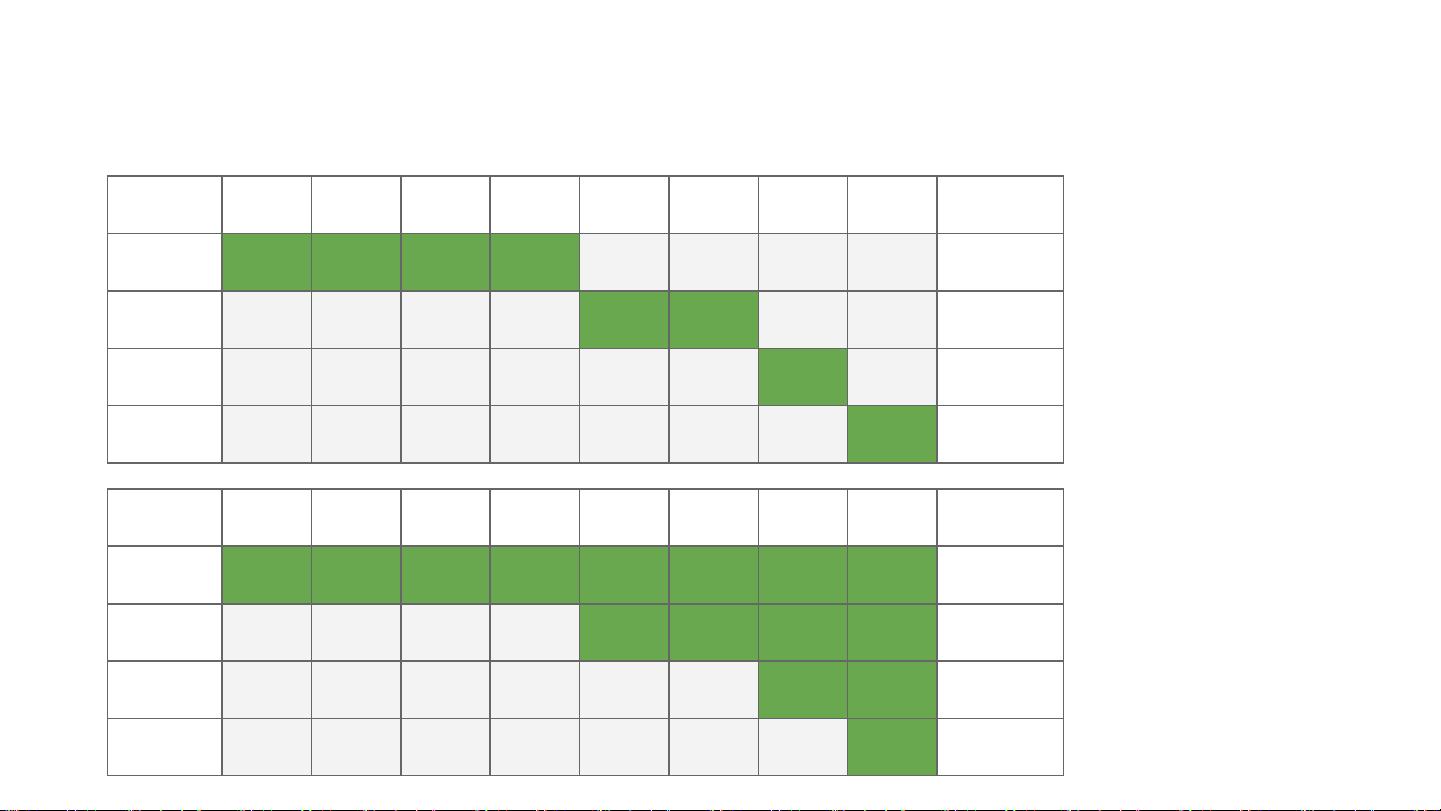

Intel的Cache Allocation Technology(CAT)旨在将L3缓存划分为多个部分,并将这些部分独立开来,允许为每个核心定义不同的分配类别。这样做的好处是可以动态指定哪些缓存区域可以在从主内存引入新缓存行时被替换,同时结合进程固定(pinning)或未来的控制组(cgroups),可以减少缓存污染。这一技术在某些Haswell SKU(如E5-25x8v3)上可用。

与CAT一同提供的还有Cache Monitoring Technology(CMT)。CMT允许对每个核心的L3缓存分配进行监控,这有助于分析和优化系统性能,理解不同核心如何使用L3缓存,以及在运行多线程应用时如何更有效地管理缓存资源。

这些实验和介绍对理解Intel处理器的高级特性,尤其是如何通过调整缓存策略来提升多核系统的性能,具有重要的参考价值。开发者和系统管理员可以通过应用CAT和CMT,更精确地控制和监控缓存行为,从而优化应用程序的运行效率。

2022-09-03 上传

2024-09-25 上传

2023-04-27 上传

2023-05-09 上传

2023-02-13 上传

2023-05-24 上传

2023-06-02 上传

2023-05-11 上传

2023-05-20 上传

2023-02-13 上传

weixin_38665411

- 粉丝: 8

- 资源: 936

最新资源

- 新型智能电加热器:触摸感应与自动温控技术

- 社区物流信息管理系统的毕业设计实现

- VB门诊管理系统设计与实现(附论文与源代码)

- 剪叉式高空作业平台稳定性研究与创新设计

- DAMA CDGA考试必备:真题模拟及章节重点解析

- TaskExplorer:全新升级的系统监控与任务管理工具

- 新型碎纸机进纸间隙调整技术解析

- 有腿移动机器人动作教学与技术存储介质的研究

- 基于遗传算法优化的RBF神经网络分析工具

- Visual Basic入门教程完整版PDF下载

- 海洋岸滩保洁与垃圾清运服务招标文件公示

- 触摸屏测量仪器与粘度测定方法

- PSO多目标优化问题求解代码详解

- 有机硅组合物及差异剥离纸或膜技术分析

- Win10快速关机技巧:去除关机阻止功能

- 创新打印机设计:速释打印头与压纸辊安装拆卸便捷性