UVM方法学实战指南:官方资料解析

"uvm_cookbook2019 mentor 官方资料,涵盖了UVM的基础知识、组件、工厂、时相、驱动、监控器、代理、序列、配置数据库、包的使用、测试平台架构等内容,深入浅出地指导了如何构建和配置UVM验证环境。"

《UVM Cookbook》是Mentor Graphics官方发布的一份详细指南,主要针对Universal Verification Methodology(UVM)这一广泛使用的系统Verilog验证方法学。这份文档旨在帮助工程师理解和应用UVM进行集成电路验证。

1. **UVMBasics**:这部分介绍了UVM的基本概念,包括测试平台的基本结构,强调了UVM作为可复用和可配置的验证组件库的重要性。它还涵盖了如何利用UVM来建立高效的验证环境。

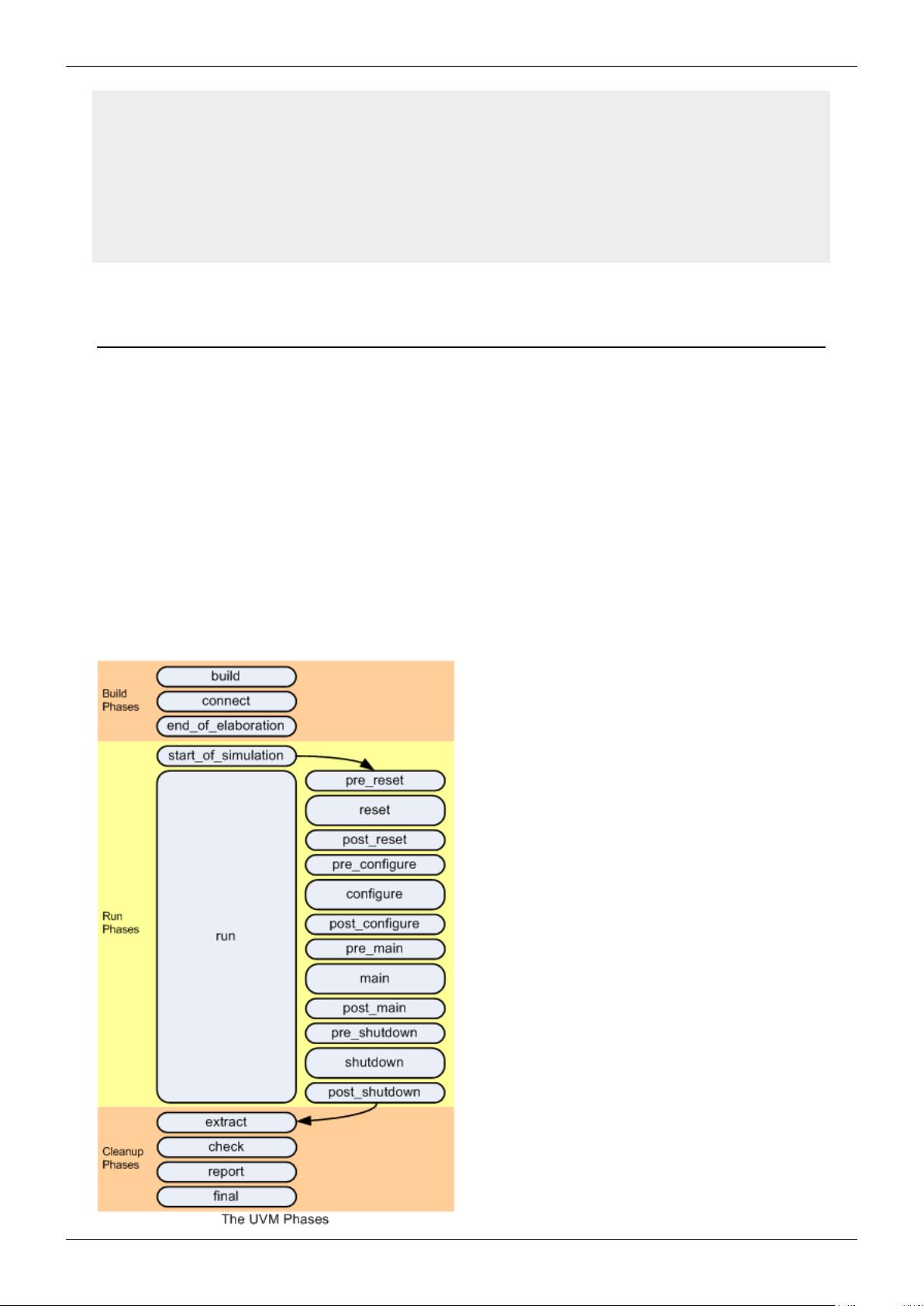

2. **UVMComponents**:UVM组件是构成UVM测试平台的核心元素,包括Factory(工厂)、Phasing(时相)、Driver(驱动)、Monitor(监控器)、Agent(代理)等。Factory用于动态创建和实例化组件;Phasing允许在不同阶段执行组件的不同任务;Driver负责与DUT(设计单元)交互;Monitor则监控DUT的行为;Agent是Driver和Monitor的组合,提供了一个完整的数据通路。

3. **UVMSequences & SequenceItems**:UVMSequences用于生成激励并驱动测试,而SequenceItems则是这些激励的基本单元。它们可以被用来创建复杂和随机化的测试序列。

4. **UVMConfigurationDatabase(uvm_config_db)**:配置数据库允许在运行时传递参数和对象到任何层次的UVM组件,增强了可配置性和灵活性。

5. **UsingPackages**:UVM基于包的组织结构,了解如何正确使用和组织包对于有效管理UVM组件至关重要。

6. **TestbenchArchitecture**:这部分详细讲解了如何构建UVM测试平台的架构,包括Block-Level和Integration-Level的测试平台,以及Dual Top Architecture的设计。

7. **DUT-TestbenchConnections**:连接DUT和测试平台是验证的关键步骤,涉及接口和虚拟接口的使用,以及如何通过虚拟接口行为模型(BFMs)进行通信。

8. **HandlingParameterization**:参数化在UVM中用于根据不同的设计需求定制组件,抽象-具体类的连接和参数化测试是实现这一目标的手段。

9. **ConfiguringaTestEnvironment**:配置测试环境包括设置测试平台的配置参数,以及如何配置Sequences以适应特定的验证场景。

10. **TestbenchConfiguration & ConfiguringSequences**:这部分详细说明了如何通过UVM配置数据库来配置测试平台和序列,以实现更高效和精确的验证流程。

《UVM Cookbook 2019》是一份全面的参考资料,不仅适合初学者学习UVM的基础知识,也对有经验的验证工程师具有很高的参考价值,帮助他们更有效地构建和管理复杂的SoC验证环境。

2019-08-24 上传

点击了解资源详情

2023-06-20 上传

2024-04-25 上传

2023-05-14 上传

2023-04-27 上传

2023-10-24 上传

斐非韭

- 粉丝: 5993

- 资源: 2

最新资源

- AirKiss技术详解:无线传递信息与智能家居连接

- Hibernate主键生成策略详解

- 操作系统实验:位示图法管理磁盘空闲空间

- JSON详解:数据交换的主流格式

- Win7安装Ubuntu双系统详细指南

- FPGA内部结构与工作原理探索

- 信用评分模型解析:WOE、IV与ROC

- 使用LVS+Keepalived构建高可用负载均衡集群

- 微信小程序驱动餐饮与服装业创新转型:便捷管理与低成本优势

- 机器学习入门指南:从基础到进阶

- 解决Win7 IIS配置错误500.22与0x80070032

- SQL-DFS:优化HDFS小文件存储的解决方案

- Hadoop、Hbase、Spark环境部署与主机配置详解

- Kisso:加密会话Cookie实现的单点登录SSO

- OpenCV读取与拼接多幅图像教程

- QT实战:轻松生成与解析JSON数据