ASIC可测性设计详解:AdHoc与结构化技术与ATPG扫描

需积分: 25 163 浏览量

更新于2024-07-19

1

收藏 930KB PDF 举报

ASIC可测性设计技术是专用于提高专用集成电路(ASIC)可靠性的关键设计策略。本文详细探讨了这一领域的核心技术,主要包括以下几个部分:

1. **引言**:文章首先阐述了在现代集成电路设计中,确保芯片在制造过程中的可测试性的重要性,尤其是在ASIC领域,由于定制化程度高,故障诊断和修复难度增大,因此可测性设计显得尤为重要。

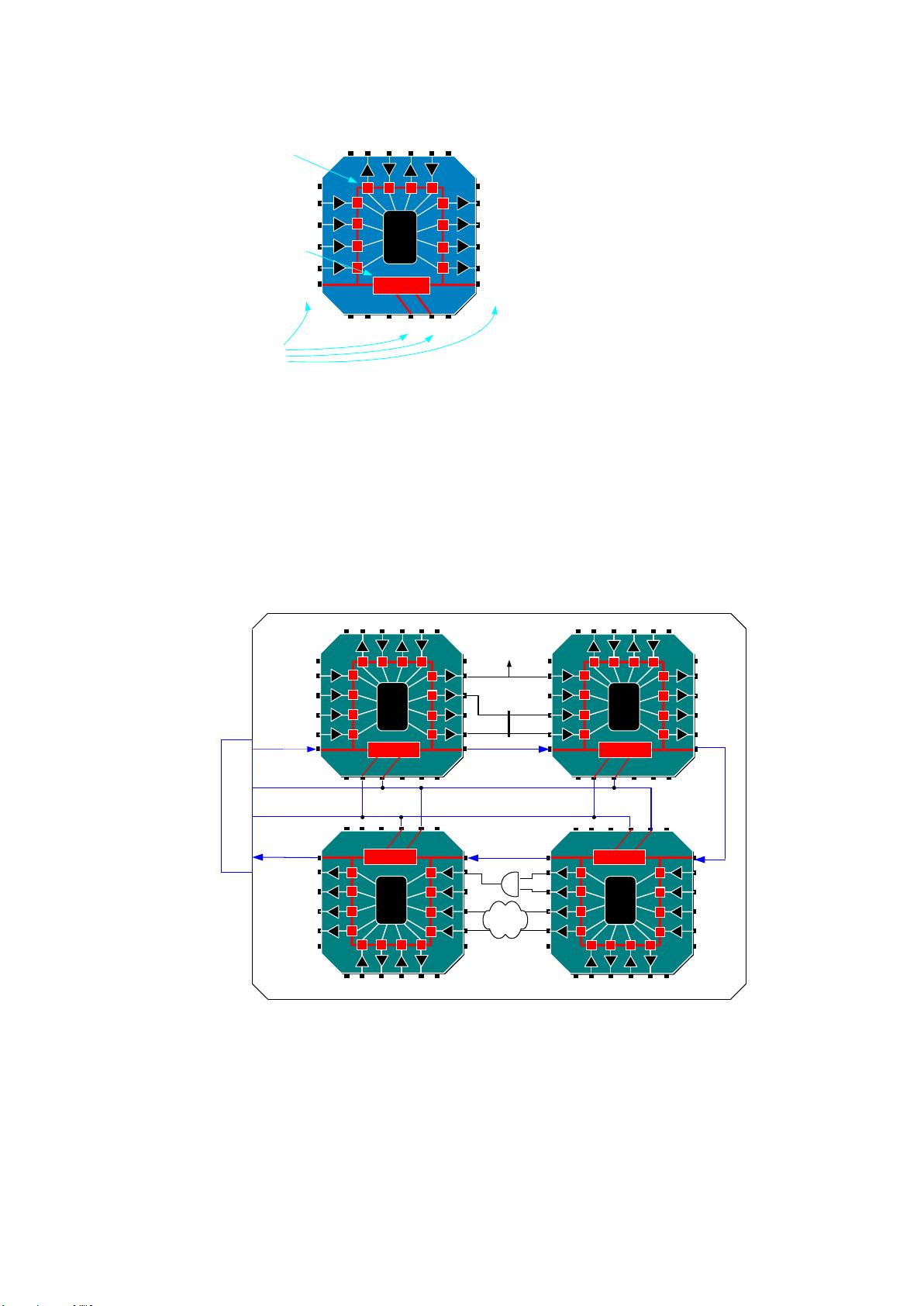

2. **DFT基本概念**:设计者通常采用两种主要的可测性技术——AdHoc技术和结构化设计。AdHoc技术是一种灵活但可能效率较低的方法,通过在设计中插入测试门实现;结构化设计如扫描技术和内建自测试(BIST)则更为系统化,能够自动化检测和修复错误。扫描技术包括JTAG(Joint Test Action Group)协议,它提供了硬件级的可编程测试路径,而BIST则在设计内部集成测试逻辑,节省了外部测试资源。

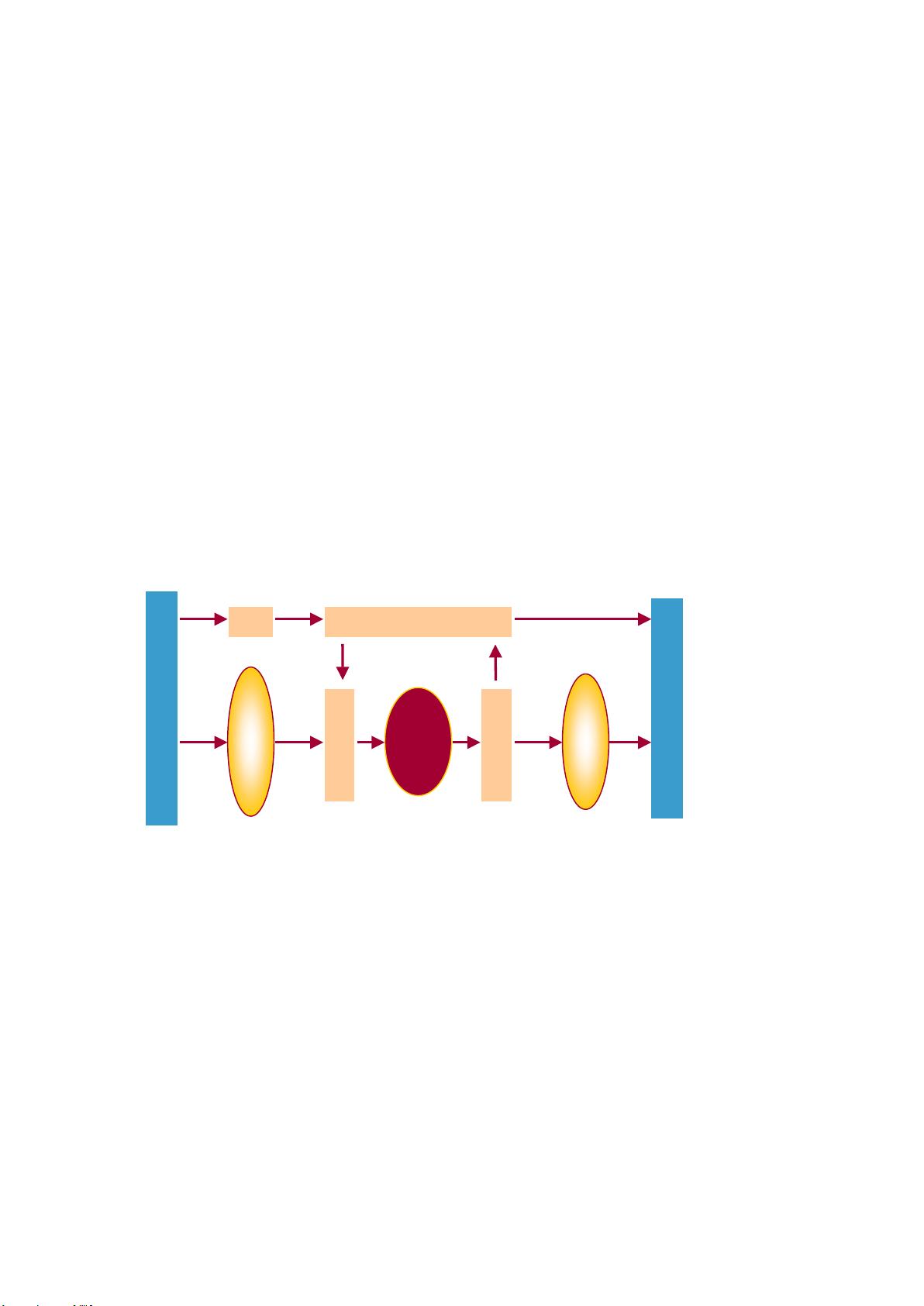

3. **基于ATPG的扫描测试**:文章深入解析了扫描测试的工作原理,包括测试序列的生成、测试阶段划分、基本时序控制,以及在实际设计中应注意的要点。ATPG(Automatic Test Pattern Generator)用于生成针对特定测试目标的测试模式,确保覆盖所有功能单元。

4. **DCXP使用方法**:Design Compiler ExpertPlus(DCXP)是一款广泛使用的工具,文章详细讲解了如何利用它进行DFT设计,包括建立设计环境、处理未映射和已映射设计的DFT流程,以及实际操作中的步骤和案例。

5. **常见问题与解决方案**:针对设计过程中可能出现的问题,如冗余逻辑、门控时钟、异步复位处理等,文章提供了相应的解决策略。高级问题如移位寄存器、总线冲突、反馈环和特殊单元如RAM或未知细胞的处理也得到了关注。

6. **边界扫描电路设计**:这是一种直接对电路边缘进行测试的技术,包括硬件描述、TAP(Test Access Port)控制器、以及使用BSD(Boundary Scan Description Language)进行配置和编程的过程。

7. **DCXP与MentorFastScan结合**:文章还介绍了如何将这两种工具结合使用,以优化ASIC的可测性设计流程,例如Mentor FastScan的简要介绍以及与DCXP集成的具体步骤。

ASIC可测性设计技术是一套复杂的体系,涵盖了从基础的测试原理到高级的工具应用,旨在确保ASIC产品的高质量和可靠性。掌握这些技术对于集成电路设计工程师来说至关重要,有助于减少设计缺陷,缩短产品上市时间,并降低维修成本。

2019-07-23 上传

2011-03-07 上传

2023-03-28 上传

2022-09-23 上传

点击了解资源详情

2024-11-05 上传

2024-11-05 上传

2024-11-06 上传

点击了解资源详情

qq_17616613

- 粉丝: 0

- 资源: 2

最新资源

- 情感分类器

- MemoryTest.rar_数值算法/人工智能_Visual_C++_

- sketch-data-super-heroes::male_sign::male_sign:此存储库包含适用于Sketch设计师的超级数据集

- 人工智能五子棋.zip

- HotApplet-开源

- matlab心线代码-ECG-electrocardiogram:这是使用PIC18F4550微处理器创建的ECG

- Codeflix

- tv-shows-nextjs:电视节目与Next.js一起使用

- 小白简约浏览器界面.zip

- led-matrix-art:PIXEL控制台应用程序的更好的Web界面

- ADEL-WEB

- TicketKit是一个可以轻松创建票证或优惠券的框架-Swift开发

- 人工智能社会保险反欺诈分析-rank26.zip

- center.rar_教育系统应用_Visual_C++_

- Elenco-crx插件

- admissionClassification