优化刻蚀技术:提升垂直氮化镓功率电子器件性能

需积分: 5 177 浏览量

更新于2024-08-11

收藏 456KB DOCX 举报

"优化刻蚀以改善垂直型氮化镓功率电子器件的选区掺杂"

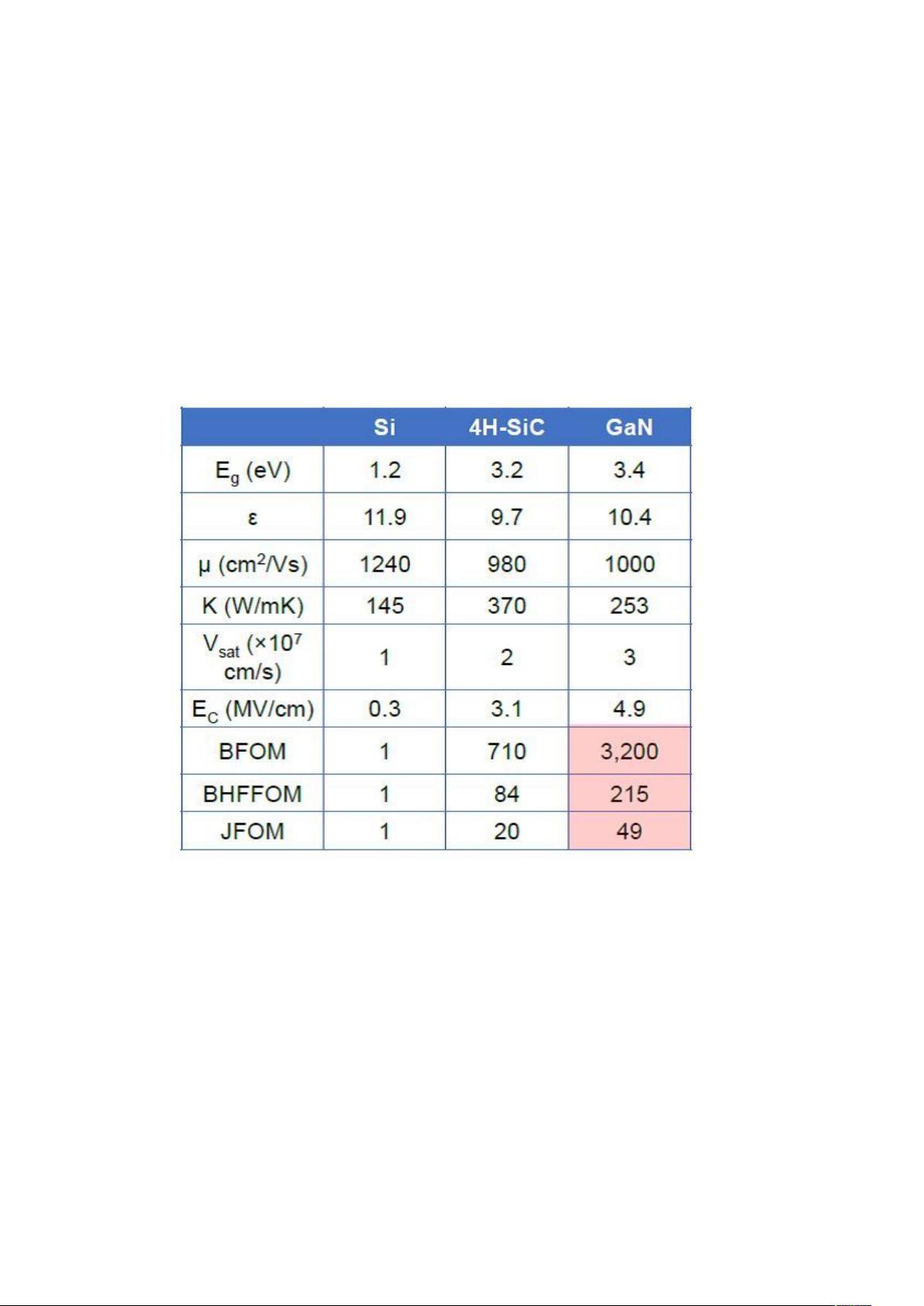

在功率电子领域,氮化镓(GaN)由于其独特的材料特性,如宽禁带(带隙Eg大)、高临界电场(EC强)、高电子迁移率(µ高)和出色的热导率(K高),已成为制造高性能器件的理想选择。相比硅(Si),氮化镓器件能在相同厚度下承受更高的击穿电压,同时具备更低的导通电阻和更快的开关速度,这体现在多个优值指标上,如Baliga优值(BFOM)、Baliga高频优值(BHFFOM)和约翰逊优值(JFOM)。

传统的氮化镓功率电子器件多采用水平型结构,如高电子迁移率晶体管(HEMT),其电流沿横向流动。但这类器件存在若干挑战,如表面态导致性能退化、热量集中引起的温度升高,以及为了提高击穿电压而需扩大芯片面积,影响了器件的可扩展性和可靠性。因此,垂直型氮化镓功率电子器件的开发显得尤为重要。

垂直型器件在同质衬底上生长,能有效减少材料缺陷密度,提升器件性能,同时其结构使得击穿电压和正向工作电流得以提高,而无需增加芯片面积。这样的设计还有助于改善散热和器件扩展性,因为它不受表面状态的影响。尽管氮化镓衬底成本相对较高,但随着技术进步和市场需求的增长,其价格有望逐渐降低。

垂直型氮化镓功率电子器件的结构主要包括四个关键部分:缓冲层、漂移层、沟道层和边缘终端区。每层都有其特定功能和优化要求:

1. 缓冲层:作为衬底与器件结构之间的过渡层,它的主要任务是减少衬底与外延层之间的应力,降低位错密度,以提高器件的整体稳定性。

2. 漂移层:这一层决定了器件的击穿电压,通常采用多量子阱或高阻材料来实现较高的电压承受能力,同时保持较低的漏电流。

3. 沟道层:控制电流的传导路径,其厚度和掺杂浓度直接影响器件的导通电阻和开关性能。优化沟道层的工艺,如选区掺杂,是提升器件性能的关键步骤。

4. 边缘终端区:用于抑制电场尖峰,防止电荷积累,减少寄生效应,以确保器件的稳定运行。

在优化刻蚀过程中,需要精细控制刻蚀速率、深度和均匀性,以减少刻蚀损伤并确保掺杂剂的精确分布。刻蚀工艺的选择(如干法刻蚀、湿法刻蚀或等离子体增强化学气相沉积PECVD)和参数设置都会对器件性能产生深远影响。通过优化这些步骤,可以实现更好的掺杂控制,从而提高垂直型氮化镓功率电子器件的效率和可靠性。

优化刻蚀工艺对于改善垂直型氮化镓功率电子器件的选区掺杂至关重要,这不仅能充分利用氮化镓的优良材料特性,还能克服水平型器件的局限性,推动功率电子技术在新能源、数据中心、电动汽车等多个领域的广泛应用。

2021-05-15 上传

2021-05-14 上传

2022-12-01 上传

2023-07-28 上传

2023-05-29 上传

2023-08-25 上传

2023-05-29 上传

2023-05-25 上传

2023-07-28 上传

weixin_38745233

- 粉丝: 10

- 资源: 906

最新资源

- C++多态实现机制详解:虚函数与早期绑定

- Java多线程与异常处理详解

- 校园导游系统:无向图实现最短路径探索

- SQL2005彻底删除指南:避免重装失败

- GTD时间管理法:提升效率与组织生活的关键

- Python进制转换全攻略:从10进制到16进制

- 商丘物流业区位优势探究:发展战略与机遇

- C语言实训:简单计算器程序设计

- Oracle SQL命令大全:用户管理、权限操作与查询

- Struts2配置详解与示例

- C#编程规范与最佳实践

- C语言面试常见问题解析

- 超声波测距技术详解:电路与程序设计

- 反激开关电源设计:UC3844与TL431优化稳压

- Cisco路由器配置全攻略

- SQLServer 2005 CTE递归教程:创建员工层级结构