优化集成电路压降:填充金属策略与应用

72 浏览量

更新于2024-08-29

收藏 222KB PDF 举报

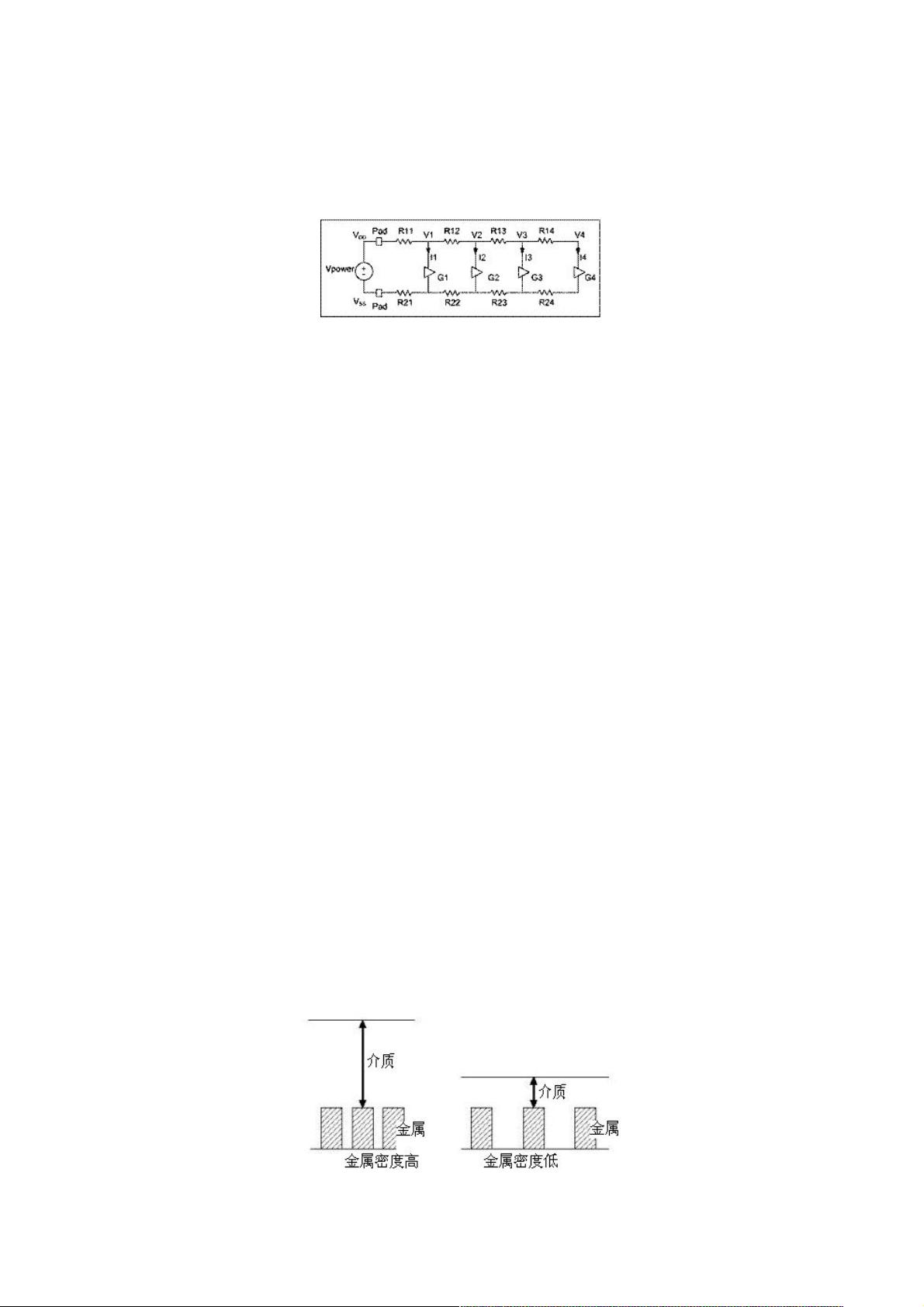

集成电路设计中的压降优化是一个关键问题,特别是在深亚微米设计中,由于线路电阻增加,电源分配网络的效率会显著降低。为了减少压降并保持电路的正常工作,填充金属被广泛应用在优化过程中。

1. 引言:

压降的产生源于集成电路中电源网格与各个逻辑单元之间的电阻交互作用。随着芯片尺寸减小和功能集成度提高,连线变得更长,电阻增大,导致电压损失(Vdrop)。压降不仅影响单个逻辑单元的性能,而且随着多个单元同时工作,压降的累积效应更为明显。因此,减小等效电阻成为优化压降的关键策略,特别是对于远离电源引脚的高密度逻辑单元区域。

2. 填充金属及其应用:

填充金属是一种有效的解决方案,它通过增加导线的横截面积,从而降低单位长度的电阻。填充金属通常采用物理/化学气相沉积法(Physical Vapor Deposition, PVD)或光刻技术结合腐蚀步骤在芯片制造流程中实施。首先,wafer表面需要经过平整化处理,如化学机械抛光(CMP),以确保均匀的介质层厚度。在金属层薄且导电性能不足的地方,填充金属会被注入,提高该区域的导电性,进而减小电阻。

2.1 实现填充金属的方法:

- 物理气相沉积:通过加热或电子轰击的方式将金属粒子蒸发,然后在基底上冷却凝固形成导线,这可以精确控制金属层的厚度和分布。

- 光刻技术:通过精密的光刻图案化过程,在选定区域添加金属层,确保填充金属仅覆盖需要增强导电性的部分。

- 腐蚀过程:在填充金属沉积之后,可能需要进行腐蚀步骤,以去除多余的金属,只留下预期的填充结构。

通过这些方法,填充金属可以在不影响整体电路布局的前提下,有针对性地降低局部的电阻,从而显著降低压降。在设计阶段,工程师需要综合考虑填充金属的位置、形状和厚度,以实现最优的压降控制,同时不影响其他电路性能。

总结来说,集成电路设计中利用填充金属优化压降是一个多学科交叉的技术,涉及材料科学、光刻技术、集成电路制造工艺等多个领域。通过精确的控制和合理的填充策略,可以显著提升电路的能效和可靠性。

2021-09-22 上传

2021-09-21 上传

2021-09-15 上传

2020-10-19 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38665193

- 粉丝: 6

- 资源: 988

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录