Nordic nRF52810:2.4GHz低功耗蓝牙芯片详解

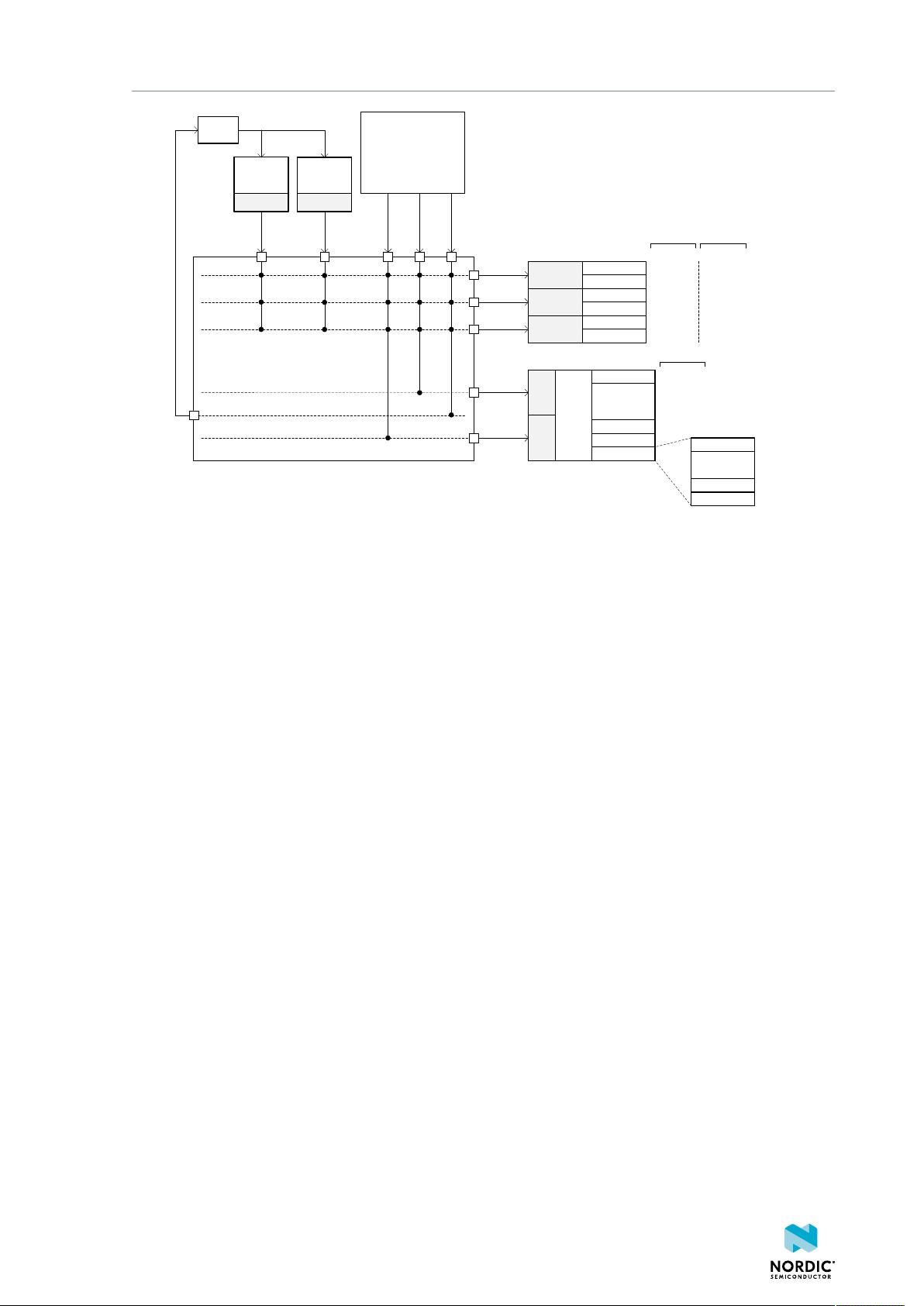

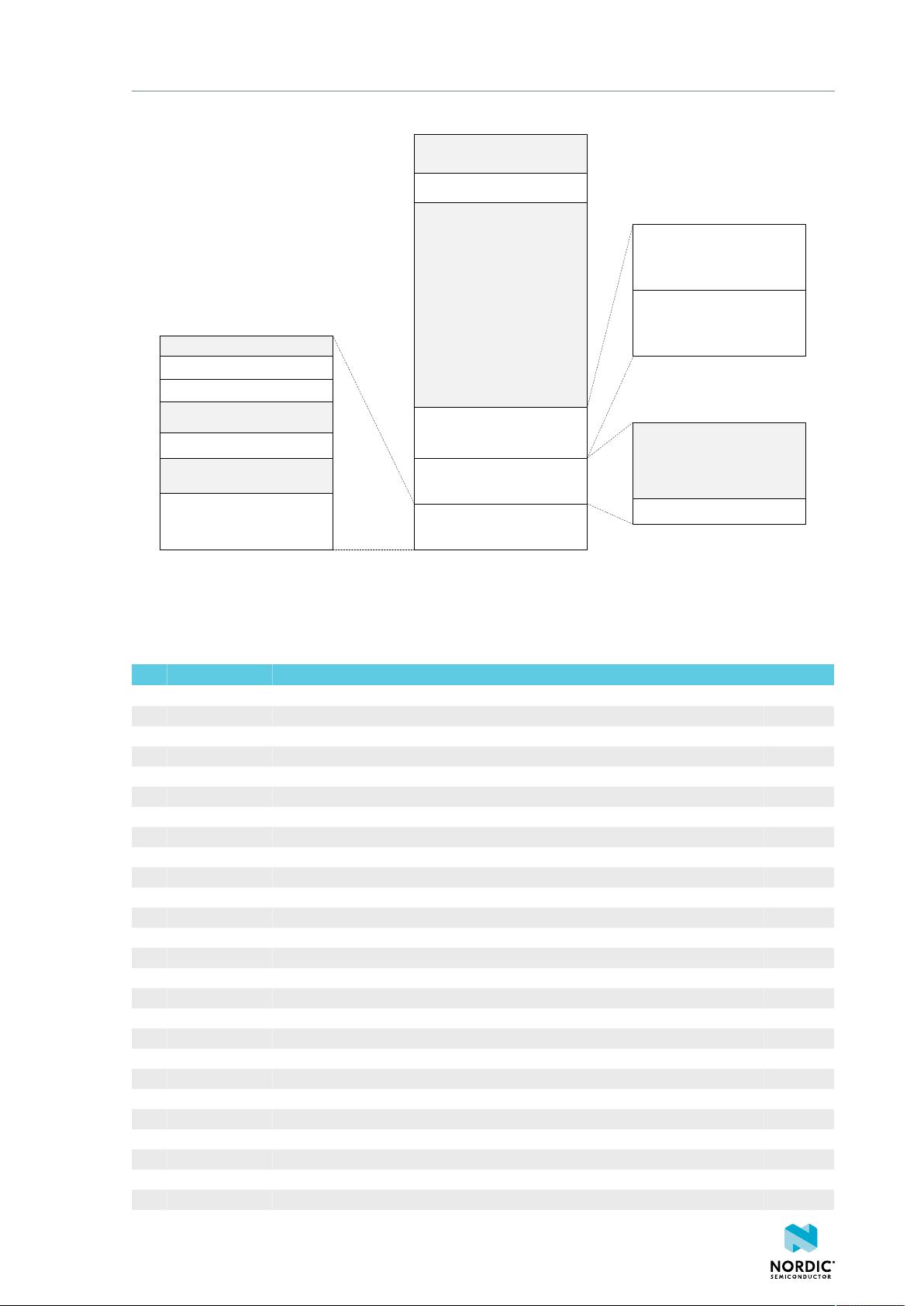

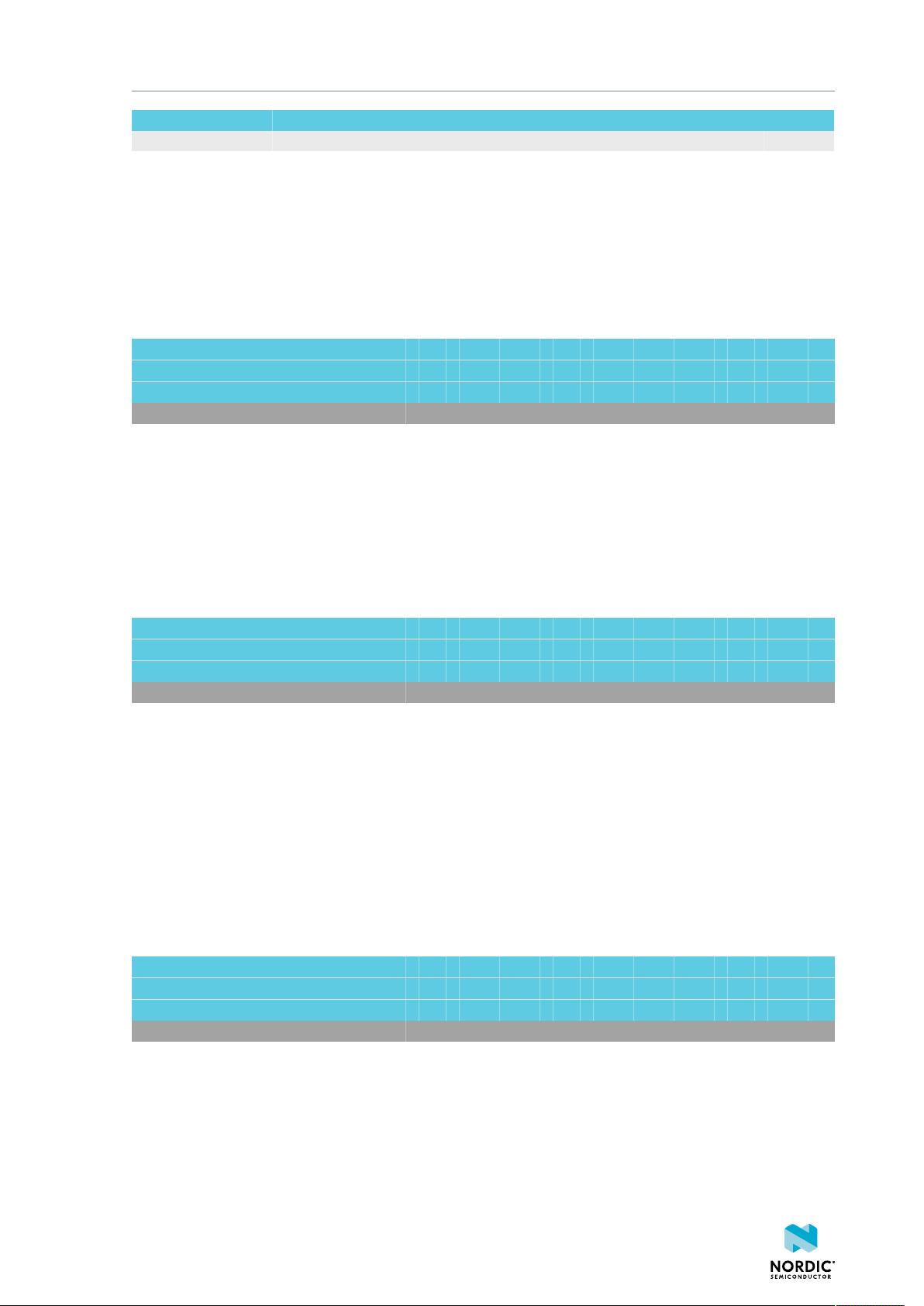

nRF52810是一款高性能、低功耗的系统单片机(SoC),专为物联网(IoT)和蓝牙低功耗应用设计。其详细规格表涵盖了丰富的功能集,使得它在无线通信、电源管理、处理能力和存储方面表现出色。 首先,nRF52810的核心是基于ARM Cortex-M43的24位处理器,运行速度高达64MHz,具有出色的计算性能,支持144 EEMBC CoreMark得分,表明它能够高效地执行多任务和复杂的算法。这款芯片还内置了192 kB的闪存和24 kB的RAM,确保了足够的存储空间用于程序代码和数据存储。 在无线通信方面,nRF52810配备了一个2.4GHz的收发器,支持蓝牙低功耗(BLE)模式,具有-96 dBm的灵敏度,可以在远距离下实现稳定的数据传输。数据速率可配置为1 Mbps和2 Mbps,适合不同应用场景下的连接需求。此外,它支持单端式射频平衡(On-chip balun),提供灵活的射频信号处理能力,峰值电流在发射(TX)和接收(RX)模式下分别为4.6 mA和4.6 mA。 电源管理是该芯片的一大亮点,提供了多种工作模式,包括快速唤醒功能,可以利用64 MHz内部振荡器实现快速启动。在系统处于关机状态时,最低功耗可达0.3 µA,如果需要保持RAM数据,功耗会略微增加到0.5 µA。而在系统正常运行时,功耗为1.5 µA,如果启用RTC唤醒,还会降低到1.4 µA。这些特性对于电池供电设备来说至关重要,延长了设备的电池寿命。 nRF52810还内置一个12位、200 kS/s的模拟数字转换器(ADC),支持8个可配置通道,带有可编程增益,这使得它能够精确测量传感器输入并进行高精度的数据采集,适合于工业级传感器和智能家居等应用。 此外,nRF52810支持多协议并发,便于同时处理蓝牙和其他通信协议,提高了系统的兼容性和灵活性。集成的SWD(串行 Wire Debug)接口方便开发过程中的调试和固件更新,而Nordic SoftDevice的预装则简化了蓝牙连接的设置和维护。 nRF52810作为一款功能强大且低功耗的芯片,集成了强大的处理能力、高效的无线通信和精密的模拟前端,适用于各种需要高效能和低功耗的物联网设备,如可穿戴设备、智能家居控制器和无线传感器网络。

剩余489页未读,继续阅读

- 粉丝: 199

- 资源: 9

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 李兴华Java基础教程:从入门到精通

- U盘与硬盘启动安装教程:从菜鸟到专家

- C++面试宝典:动态内存管理与继承解析

- C++ STL源码深度解析:专家级剖析与关键技术

- C/C++调用DOS命令实战指南

- 神经网络补偿的多传感器航迹融合技术

- GIS中的大地坐标系与椭球体解析

- 海思Hi3515 H.264编解码处理器用户手册

- Oracle基础练习题与解答

- 谷歌地球3D建筑筛选新流程详解

- CFO与CIO携手:数据管理与企业增值的战略

- Eclipse IDE基础教程:从入门到精通

- Shell脚本专家宝典:全面学习与资源指南

- Tomcat安装指南:附带JDK配置步骤

- NA3003A电子水准仪数据格式解析与转换研究

- 自动化专业英语词汇精华:必备术语集锦

信息提交成功

信息提交成功