FXOS8700CQ

Sensors

20 Freescale Semiconductor, Inc.

6.1.1 General I

2

C operation

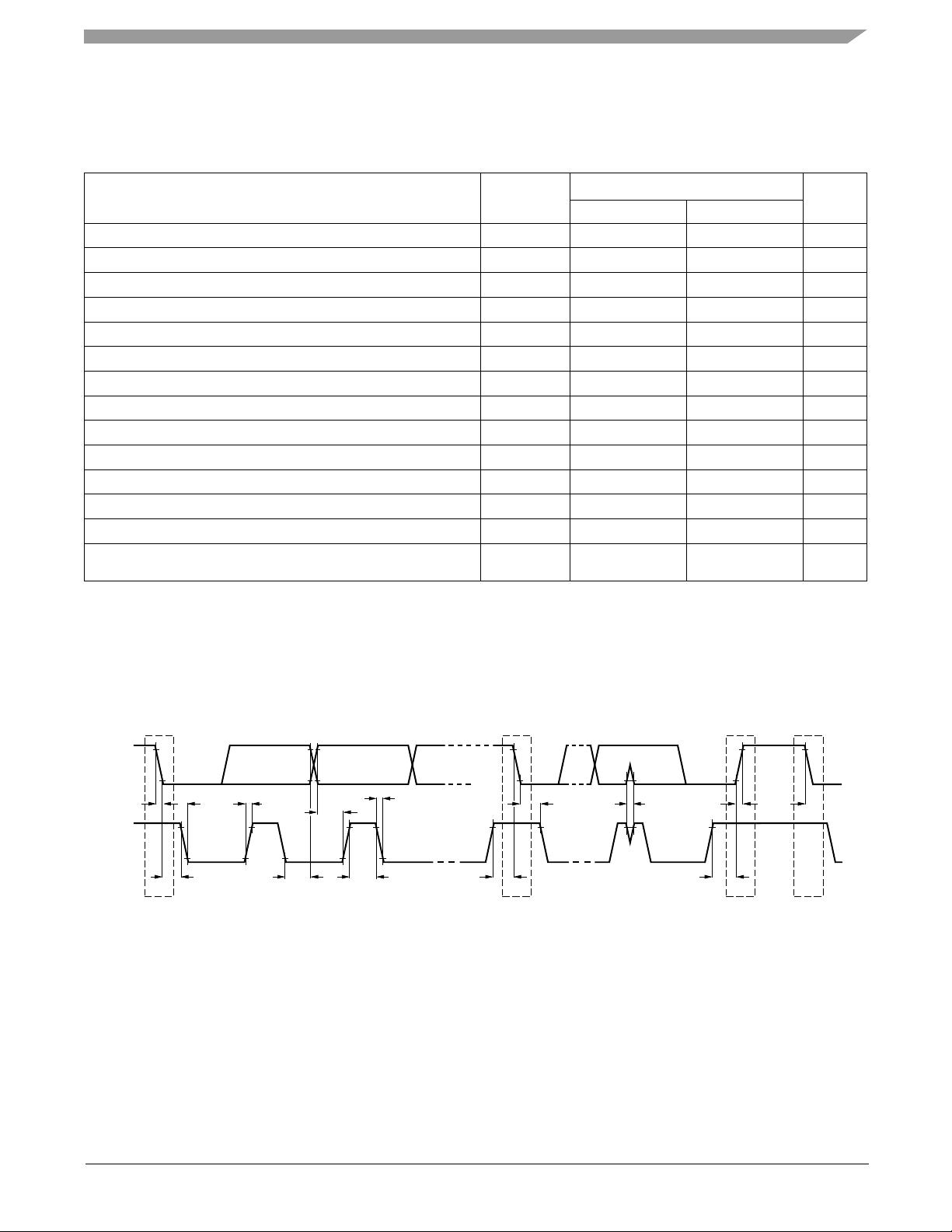

There are two signals associated with the I

2

C bus: the Serial Clock Line (SCL) and the Serial Data line (SDA). The latter is a

bidirectional line used for sending and receiving the data to/from the interface. External pullup resistors connected to VDDIO are

required for SDA and SCL. When the bus is free both the lines are high. The I

2

C interface is compliant with fast mode (400 kHz),

and normal mode (100 kHz) I

2

C standards. Operation at frequencies higher than 400 kHz is possible, but depends on several

factors including the pullup resistor values, and total bus capacitance (trace + device capacitance). See Table 10 for more

information.

A transaction on the bus is started through a start condition (ST) signal, which is defined as a HIGH-to-LOW transition on the

data line while the SCL line is held HIGH. After the ST signal has been transmitted by the master, the bus is considered busy.

The next byte of data transmitted contains the slave address in the first seven bits, and the eighth bit, the read/write bit, indicates

whether the master is receiving data from the slave or transmitting data to the slave. When an address is sent, each device in

the system compares the first seven bits after the ST condition with its own address. If they match, the device considers itself

addressed by the master. The 9th clock pulse, following the slave address byte (and each subsequent byte) is the acknowledge

(ACK). The transmitter must release the SDA line during the ACK period. The receiver must then pull the data line low so that it

remains stable low during the high period of the acknowledge clock period.

The number of bytes per transfer is unlimited. If a receiver can't receive another complete byte of data until it has performed some

other function, it can hold the clock line, SCL low to force the transmitter into a wait state. Data transfer only continues when the

receiver is ready for another byte and releases the data line. This delay action is called clock stretching. Not all receiver devices

support clock stretching. Not all master devices recognize clock stretching. This part does not use clock stretching.

A low to high transition on the SDA line while the SCL line is high is defined as a stop condition (SP) signal. A write or burst write

is always terminated by the master issuing the SP signal. A master should properly terminate a read by not acknowledging a byte

at the appropriate time in the protocol. A master may also issue a repeated start signal (SR) during a transfer

The slave addresses that may be assigned to the FXOS8700CQ part are 0x1C, 0x1D, 0x1E, or 0x1F. The selection is made

through the logic level of the SA1 and SA0 inputs.

6.1.2 I

2

C Read/Write operations

Single-byte read

The master (or MCU) transmits a start condition (ST) to the FXOS8700CQ, followed by the slave address, with the R/W bit set

to “0” for a write, and the FXOS8700CQ sends an acknowledgement. Then the master (or MCU) transmits the address of the

register to read and the FXOS8700CQ sends an acknowledgement. The master (or MCU) transmits a repeated start condition

(SR), followed by the slave address with the R/W bit set to “1” for a read from the previously selected register. The FXOS8700CQ

then acknowledges and transmits the data from the requested register. The master does not acknowledge (NAK) the transmitted

data, but transmits a stop condition to end the data transfer.

Multiple-byte read

When performing a multi-byte or “burst” read, the FXOS8700CQ automatically increments the register address read pointer after

a read command is received. Therefore, after following the steps of a single-byte read, multiple bytes of data can be read from

sequential registers after each FXOS8700CQ acknowledgment (AK) is received until a no acknowledge (NAK) occurs from the

master followed by a stop condition (SP) signaling an end of transmission.

Single-byte write

To start a write command, the master transmits a start condition (ST) to the FXOS8700CQ, followed by the slave address with the

R/W bit set to “0” for a write, and the FXOS8700CQ sends an acknowledgement. Then the master (or MCU) transmits the address

of the register to write to, and the FXOS8700CQ sends an acknowledgement. Then the master (or MCU) transmits the 8-bit data

to write to the designated register and the FXOS8700CQ sends an acknowledgement that it has received the data. Since this

transmission is complete, the master transmits a stop condition (SP) to end the data transfer. The data sent to the FXOS8700CQ

is now stored in the appropriate register.

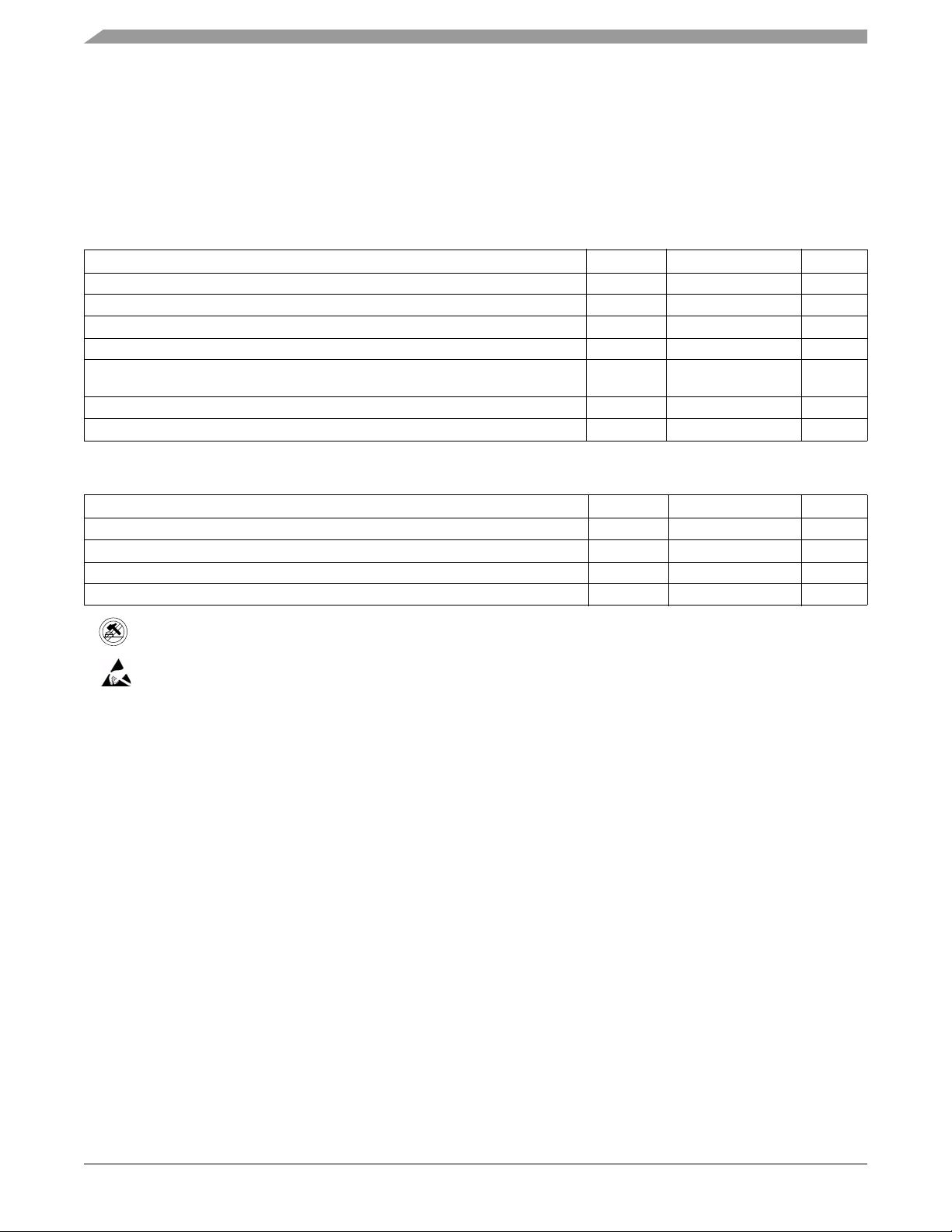

Table 10. I

2

C slave address

SA1 SA0 Slave address

0 0 0x1E

010x1D

100x1C

1 1 0x1F