Chipscope 使用教程:CoreGenerator 方法

需积分: 10 60 浏览量

更新于2024-07-29

收藏 437KB PDF 举报

"Chipscope 简明教程——介绍如何使用Xilinx ISE Chipscope逻辑分析仪,包括CoreGenerator和CoreInserter两种方法,并提供一个简单的RTL设计及仿真实例。"

在数字系统设计中,特别是在FPGA(Field Programmable Gate Array)开发中,逻辑分析仪是一个至关重要的工具,它能帮助我们理解和调试复杂的硬件设计。Xilinx的Chipscope是一款集成在ISE(Integrated Software Environment)中的逻辑分析仪,用于在FPGA内部进行实时信号观测。本教程将简要介绍如何利用Chipscope进行设计验证。

首先,操作环境的设定是成功使用Chipscope的前提。教程中提到的环境包括Modelsim作为仿真工具,Synplifypro用于综合,ISE6.2进行布局布线,以及Chipscope6.2作为逻辑分析工具。确保这些软件的正确安装和配置是开始使用Chipscope的第一步。

接着,教程提供了一个简单的RTL(Register Transfer Level)设计示例,包含lfsr.v(寄存器移位寄存器)的源代码和lfsr_tb.v(测试平台)。通过仿真,我们可以得到预期的波形结果,这为后续的逻辑分析提供了基础。

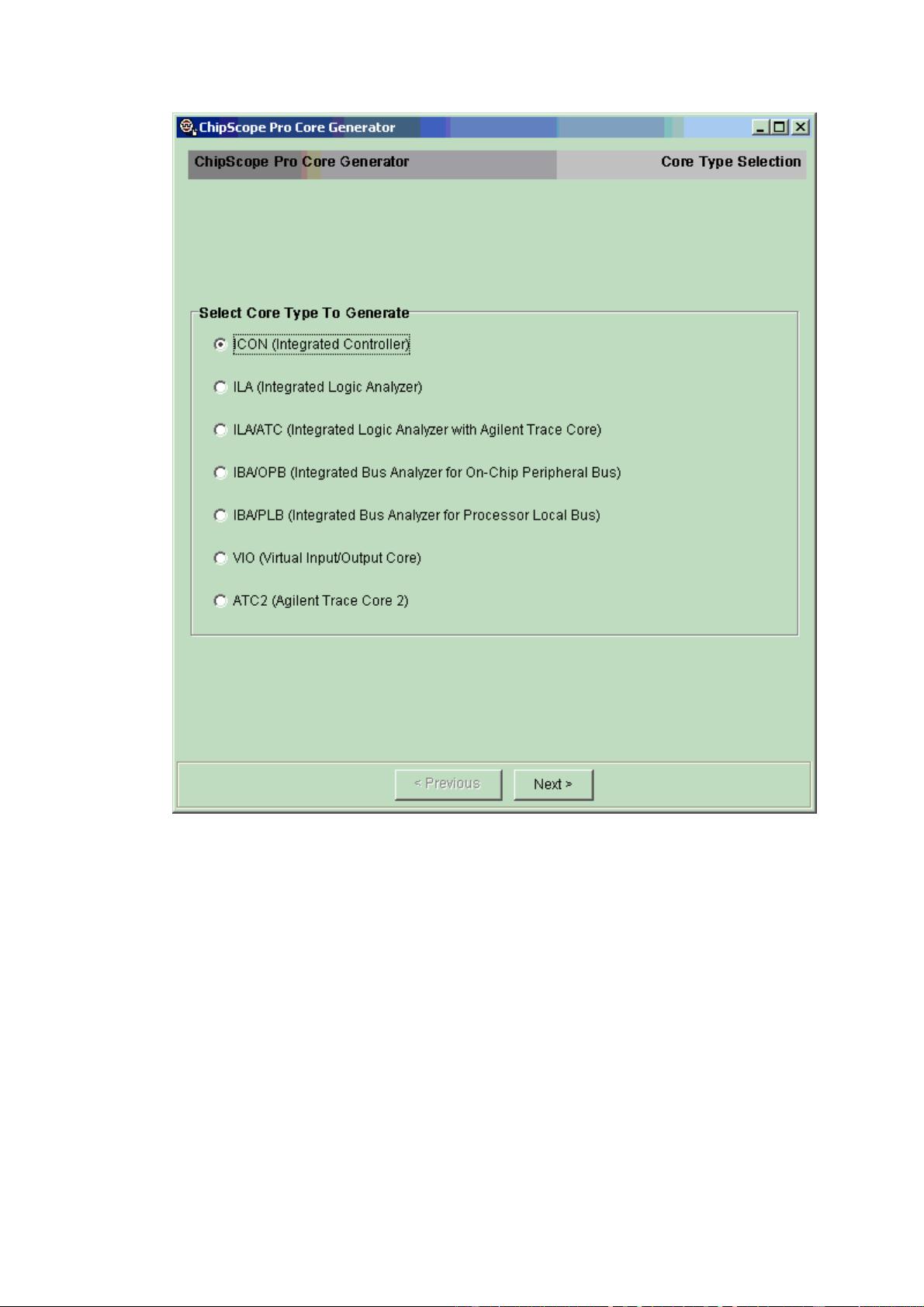

Chipscope的逻辑分析仪可以由两种方式生成:CoreGenerator和CoreInserter。CoreInserter直接在网表中插入逻辑分析仪,适合已综合的电路,但每次修改设计后需要重新插入。相比之下,CoreGenerator允许在RTL级别插入,修改设计后只需重新综合,更加灵活。教程中选择了CoreGenerator方法进行讲解。

使用CoreGenerator的步骤如下:

1. 通过“开始”->“程序”->“ChipScopePro6.2”启动CoreGenerator。

2. 选择图标(ICON),即集成控制器。

3. 设定输出目录和目标设备家族。

4. 选择语言(Verilog或VHDL)和综合工具(如Synplifypro)。

5. 生成集成控制器的Core。

6. 回到主菜单,选择ILA(Integrated Logic Analyzer)。

7. 设置输出目录、设备家族和采样时钟边沿。

8. 设置触发宽度(TriggerWidth)和数据深度(DataDepth)。

9. 选择“DataSameAsTrigger”,使数据端口与触发端口相同。

10. 检查所需的BlockRAM数量,确保不超过FPGA的限制。

11. 生成ILA的Core。

完成以上步骤后,将生成的Core插入到RTL设计中,再经过综合、布局布线,最后生成可下载的bit文件,就可以在实际FPGA硬件上运行并使用Chipscope进行调试了。

Chipscope是FPGA开发中不可或缺的调试工具,通过它,设计师可以深入了解设计内部的工作情况,找出潜在问题,从而提高设计的可靠性和效率。本教程提供的步骤和实例,为初学者提供了清晰的使用指南。

2009-08-19 上传

2009-09-01 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-11-11 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

liballfang

- 粉丝: 0

- 资源: 12