CUDA存储优化:数据传输策略与性能提升

需积分: 19 51 浏览量

更新于2024-07-16

收藏 1.47MB PPTX 举报

CUDA优化是提高GPU性能的关键技术之一,特别是在处理大量并行计算任务时。本文主要关注存储优化,特别是如何最小化CPU和GPU之间的数据传输,以减少性能瓶颈。由于CPU-GPU之间的数据传输带宽通常远低于GPU内部的全局内存带宽(如8GB/s的PCIe x16 Gen2与C2050的156GB/s和515GB/s的实例带宽),减少不必要的数据移动对于提升效率至关重要。

首先,优化存储策略包括避免不必要的Host<->device数据传输。通常,主机到设备的数据传输速度慢于GPU内存之间的通信,所以尽可能减少中间数据的传输并在GPU上直接分配、操作和释放内存,可以显著提高性能。例如,将重复计算任务安排在GPU上执行,而不是频繁地往返于CPU和GPU之间,可以减少10微秒延迟造成的性能损失,特别当数据量小于80KB时,这种影响更为明显。

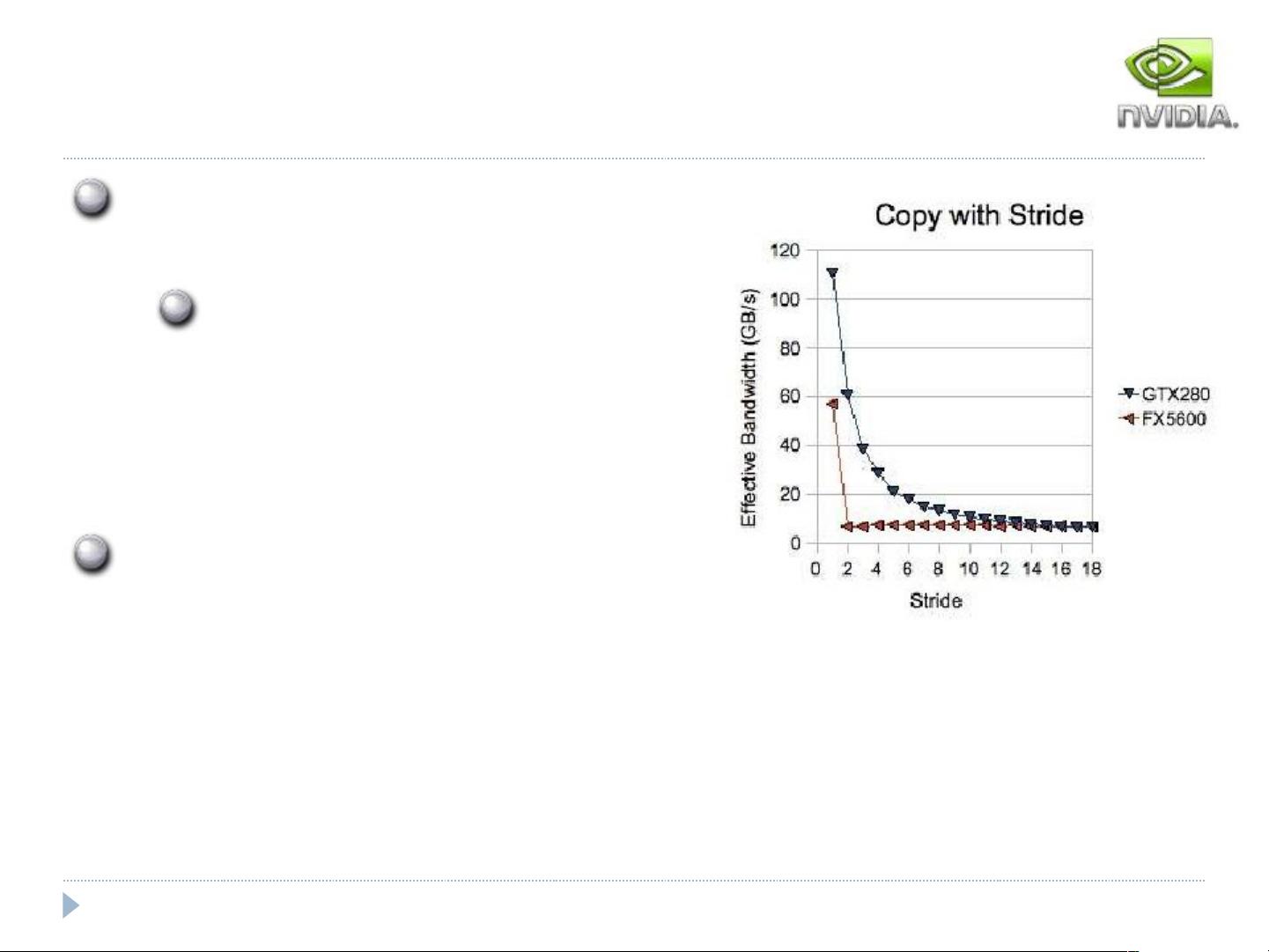

其次,内存传输和计算应该被设计成能有效地利用GPU的缓存机制。Fermi架构下的全局内存默认被缓存在一级缓存L1中,但通过nvcc编译器参数`-Xptxas –dlcm=cg`可以绕过L1缓存,将其仅缓存在二级缓存L2中。这有助于减少内存访问的延迟,因为L1缓存线粒度的请求只需要一次传输。然而,如果没有缓存,必须遵循一些合并原则,比如将内存访问合并到32字节的块(Coalescing)以减少传输次数。例如,如果矩阵按照行优先方式存储,适合每个线程访问连续的内存区域,这样可以确保访问的连续性,从而只进行1或2次传输。

对于不同的计算能力(如Compute Capability 1.0和1.1),对内存访问的要求更严格,例如对于单精度浮点数,内存访问必须是32字节、64字节或128字节的段对齐,才能实现有效的合并。不满足这些条件会导致额外的内存访问次数,降低性能。

此外,还涉及到内存访问的顺序性和对齐性问题。不按顺序的内存访问(Out-of-sequence transactions)和非对齐的访问(Misaligned accesses)都会破坏缓存的效益,导致额外的内存访问和潜在的性能下降。因此,在CUDA编程中,合理地组织内存访问模式和数据布局是至关重要的。

CUDA优化涉及存储策略、缓存利用、内存访问模式以及计算能力的适配,所有这些元素综合起来可以显著提升CUDA程序的性能,尤其是在大规模并行计算场景中。通过减少数据传输、优化缓存策略和遵循内存访问的最佳实践,开发人员能够更好地发挥GPU的潜力,加速计算密集型任务的处理。

2019-03-08 上传

2024-05-25 上传

2020-09-14 上传

2023-02-26 上传

2023-05-26 上传

2023-05-26 上传

2023-03-21 上传

2024-10-30 上传

2023-03-30 上传

2023-04-19 上传

hopkinsyang

- 粉丝: 10

- 资源: 5

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南