Spartan-6 FPGA可配置逻辑块用户指南

113 浏览量

更新于2024-06-19

收藏 4.27MB PDF 举报

"Spartan-6 FPGA Configurable Logic Block User Guide.pdf 是Xilinx公司发布的一份关于Spartan-6 FPGA配置逻辑块的用户指南,版本为UG384(v1.1),发布日期为2010年2月23日。该文档旨在帮助用户了解和使用Spartan-6 FPGA中的可配置逻辑块(CLB)进行设计开发。文档内容可能包括CLB的结构、功能、配置方法以及设计考虑等。"

正文:

Spartan-6 FPGA是Xilinx公司推出的一款广泛应用于各种嵌入式系统和数字信号处理应用的现场可编程门阵列(FPGA)。其中,Configurable Logic Block (CLB)是Spartan-6 FPGA的核心组成部分,它提供了高度灵活的逻辑单元,可以被配置成用户所需的各种逻辑功能。

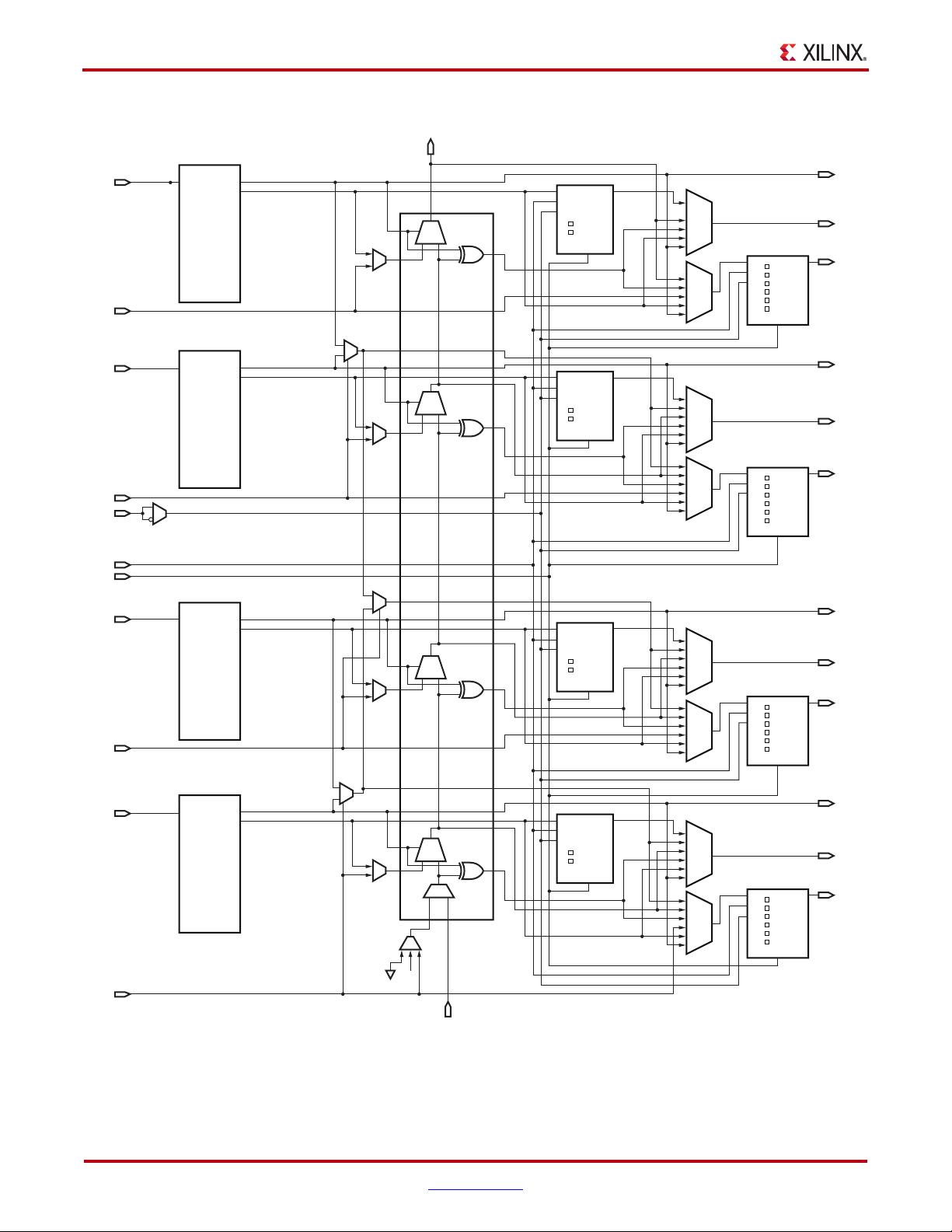

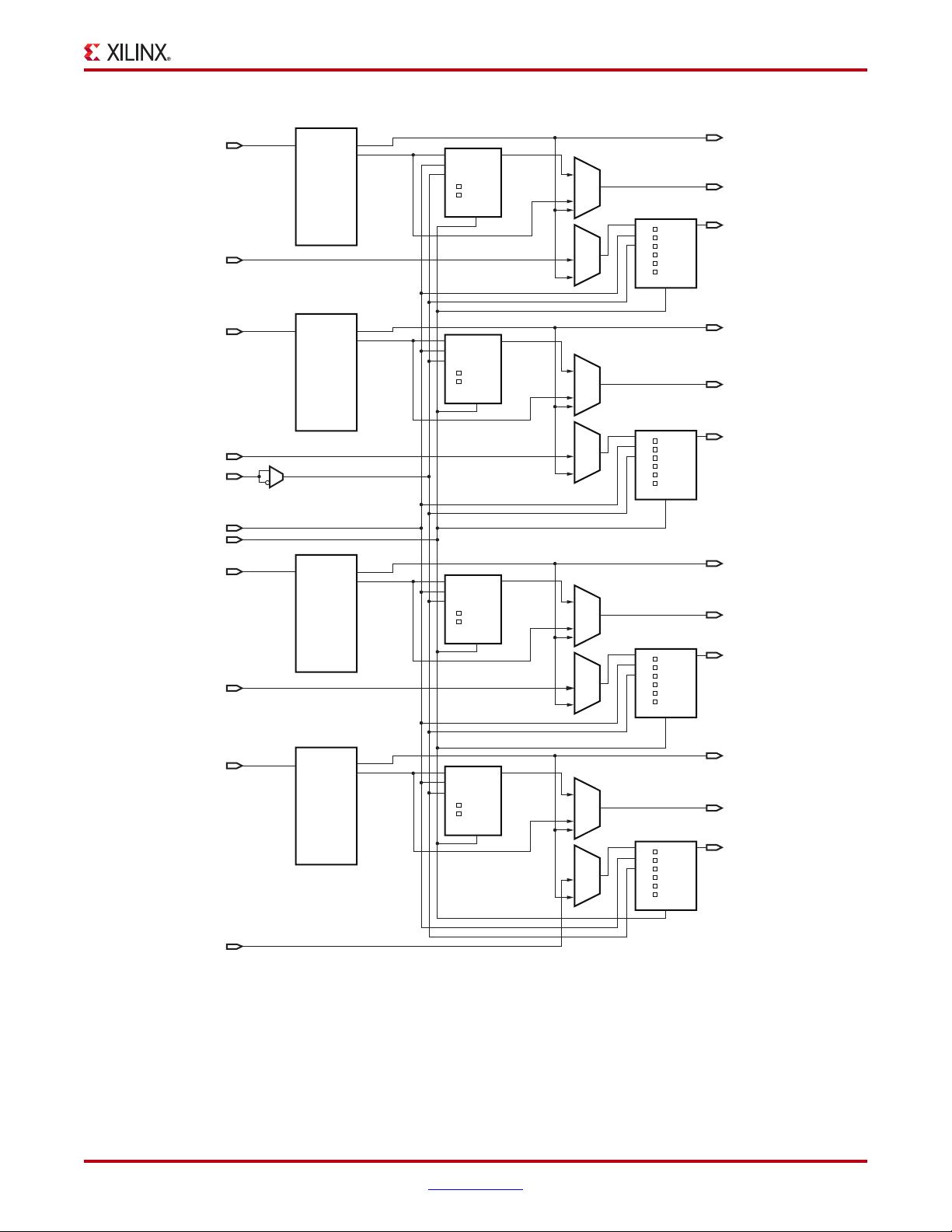

CLB由多个基本的逻辑单元(Slice)组成,每个Slice包含两个4输入查找表(LUT)和一个Flip-Flop(FF)。这些LUTs能够实现复杂的布尔函数,而FF则用于存储逻辑状态。通过组合LUT和FF,用户可以在Spartan-6 FPGA中构建任何二进制逻辑电路。LUT的设计使得逻辑优化更为高效,因为它们支持乘积项的并行计算。

在Spartan-6 FPGA中,CLB还包含了额外的硬件资源,如乘法器、分布式RAM和I/O功能。乘法器可以加速乘法操作,这对于数字信号处理(DSP)应用尤其重要。分布式RAM允许在CLB内部存储数据,减少了数据传输延迟,提高了系统性能。I/O功能则确保了CLB与外部世界的通信,包括各种接口标准的支持。

这份用户指南将详细介绍如何使用Xilinx的开发工具(如Vivado或ISE)来设计和实现基于CLB的逻辑电路。它可能涵盖了以下关键主题:

1. **CLB架构**:CLB的物理结构和内部组织,包括Slice、LUT、FF和其他附加资源。

2. **逻辑配置**:如何利用LUT进行逻辑函数配置,包括单输入、多输入逻辑表达式的实现。

3. **时序分析**:理解时序参数,如最大频率、延迟和时钟路径,以及如何优化它们。

4. **I/O管理**:如何配置I/O引脚,以满足不同的电气标准和速度要求。

5. **分布式RAM使用**:如何在CLB内创建和使用分布式RAM块。

6. **DSP功能**:介绍Spartan-6 FPGA的乘法器及其在DSP应用中的使用。

7. **功耗和电源管理**:理解功耗特性,以及如何降低静态和动态功耗。

8. **设计流程**:从设计输入到综合、布局布线,再到配置文件生成的整个流程。

由于版权和使用许可限制,文档本身可能不提供下载,但Xilinx官方网站通常会提供最新的版本和技术支持。开发者应遵循Xilinx的条款和条件,合法使用这份文档进行设计开发,并注意Xilinx可能会随时更新文档内容,以适应产品改进和技术进步。

"Spartan-6 FPGA Configurable Logic Block User Guide" 是一个宝贵的资源,对理解和充分利用Spartan-6 FPGA的CLB功能至关重要,对于任何想要在Xilinx平台上进行FPGA设计的人来说都是必不可少的参考材料。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2015-08-19 上传

2019-08-27 上传

2023-11-24 上传

2023-11-24 上传

2023-11-24 上传

2019-08-14 上传

探索者我有我路向

- 粉丝: 332

- 资源: 2100

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率