没有合适的资源?快使用搜索试试~ 我知道了~

首页基于单片机的脉搏计设计与研究.doc

《基于单片机的脉搏计》 引言 本文旨在研究基于单片机的脉搏计,通过对单片机系统的设计和实现,实现对人体脉搏的精确测量和监测。本文的目的是为了提高医疗领域对脉搏监测设备的需求,解决传统脉搏计在测量精确性和实时监测方面存在的问题。 研究概况及发展趋势综述 随着医疗技术的不断发展,人们对脉搏监测设备的需求越来越迫切。传统的脉搏计多为机械式脉搏计,测量精度有限且无法实时监测。而基于单片机的脉搏计则可以通过数字传感器实现对脉搏的高精度测量,并可以实时监测脉搏变化,因此在医疗领域具有广阔的应用前景。 本系统主要研究内容 本文主要研究基于单片机的脉搏计的总体方案设计、脉搏信号的获取与处理、显示模块的设计和实现等内容,旨在实现对脉搏的精确测量和实时监测。 总体方案论证与设计 在总体方案的设计中,我们选择了适用于单片机系统的合适的主控模块、显示模块和传感器,通过对这些模块的论证和选型,实现了基于单片机的脉搏计系统的设计和搭建。 总结 在本论文中,我们研究了基于单片机的脉搏计系统的设计和实现。通过对主控模块、显示模块和传感器的选型和论证,实现了对脉搏的精确测量和实时监测。基于单片机的脉搏计系统具有应用前景广阔,可以广泛应用于医疗领域,为人们的健康提供更好的监测手段。

资源详情

资源推荐

8

位定时器/计数器。

6. 五个中断源的中断控制系统。现在新推出的单片机都不只 5 个中断源,例

如 SST89E58RD 就有 9 个中断源。

7. 一个全双工 UART(通用异步接收发送器)的串行 I/O 口,用于实现单片

机之间或单机与微机之间的串行通信。

8. 片内振荡器和时钟产生电路,但石英晶体和微调电容需要外接。最高允许

振荡频率为 12MHz。SST89V58RD 最高允许振荡频率达 40MHz,因而大大的提

高了指令的执行速度。

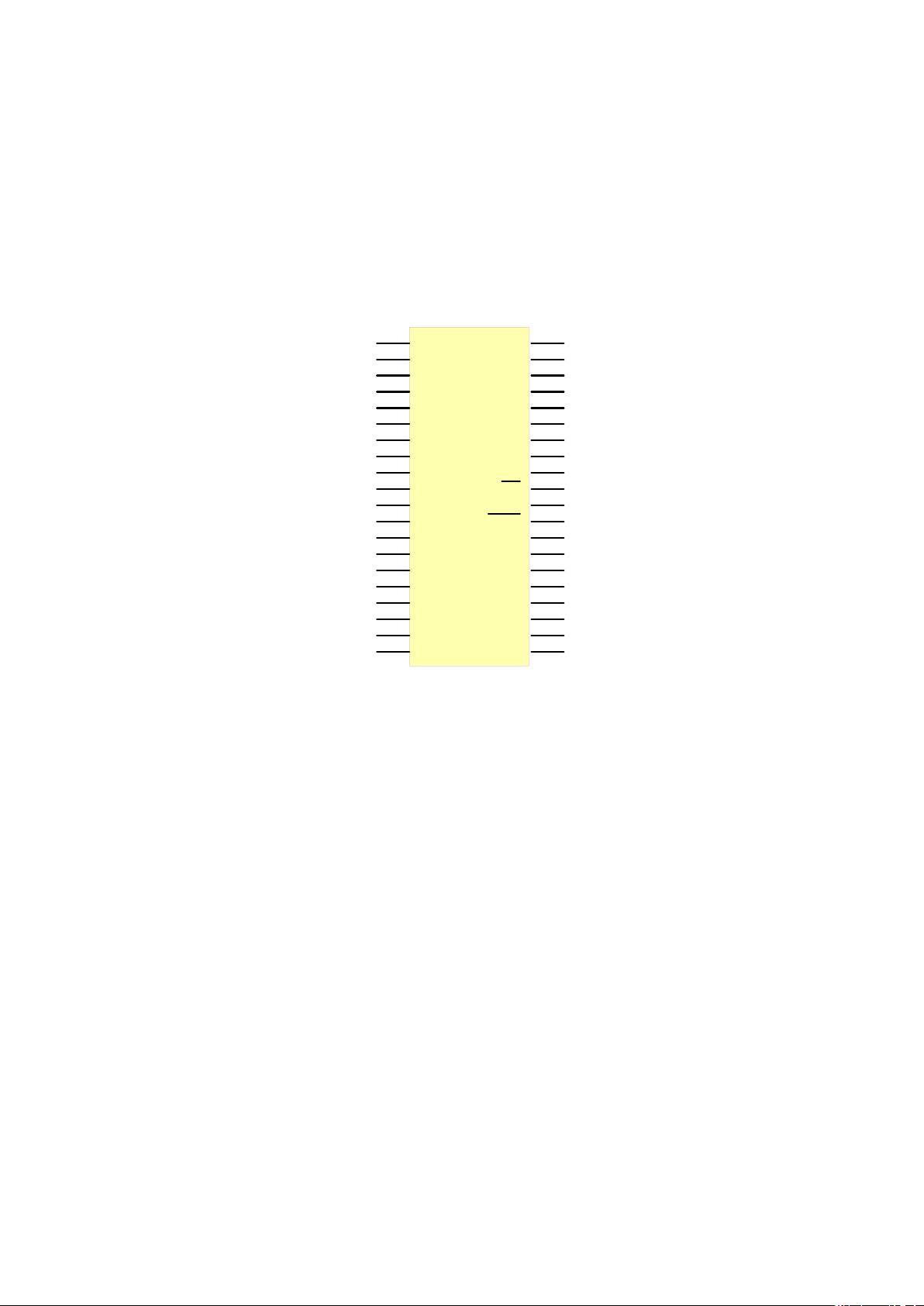

图 3-2 STC89C52 单片机管脚图

部分引脚说明:

1.时钟电路引脚 XTAL1 和 XTAL2:

XTAL2(18 脚):接外部晶体和微调电容的一端;片内它是振荡电路反相放大

器的输出端,振荡电路的频率就是晶体固有频率。若需采用外部时钟电路时,该

引脚输入外部时钟脉冲。

要检查振荡电路是否正常工作,可用示波器查看 XTAL2 端是否有脉冲信号

输出。

XTAL1(19 脚):接外部晶体和微调电容的另一端;在片内它是振荡电路反相

放大器的输入端。在采用外部时钟时,该引脚必须接地。

2.控制信号引脚 RST,ALE,PSEN 和 EA:

RST/VPD(9 脚):RST 是复位信号输入端,高电平有效。当此输入端保持备

用电源的输入端。当主电源 Vcc 发生故障,降低到低电平规定值时,将+5V 电

源自动两个机器周期(24 个时钟振荡周期)的高电平时,就可以完成复位操作。RST

引脚的第二功能是 VPD,即接入 RST 端,为 RAM 提供备用电源,以保证存储在

RAM 中的信息不丢失,从而合复位后能继续正常运行。

ALE/PROG(30 脚):地址锁存允许信号端。当 8051 上电正常工作后,ALE

引脚不断向外输出正脉冲信号,此频率为振荡器频率 fOSC 的 1/6。CPU 访问片

外存储器时,ALE 输出信号作为锁存低 8 位地址的控制信号。

P1.0

1

P1.1

2

P1.2

3

P1.3

4

P1.4

5

P1.5/MOSI

6

P1.6/MISO

7

P1.7/SCK

8

RESET

9

P3.0

10

P3.1

11

P3.2

12

P3.3

13

P3.4

14

P3.5

15

P3.6

16

P3.7

17

XTAL2

18

XTAL1

19

VSS

20

P2.0

21

P2.1

22

P2.2

23

P2.3

24

P2.4

25

P2.5

26

P2.6

27

P2.7

28

PSEN

29

ALE

30

EA

31

P0.7

32

P0.6

33

P0.5

34

P0.4

35

P0.3

36

P0.2

37

P0.1

38

P0.0

39

VCC

40

U5

单片机

9

平时不访问片外存储器时,ALE 端也以振荡频率的 1/6 固定输出正脉冲,因

而 ALE 信号可以用作对外输出时钟或定时信号。如果想确定 8051/8031 芯片的

好坏,可用示波器查看 ALE 端是否有脉冲信号输出。如有脉冲信号输出,则

8051/8031 基本上是好的。

ALE 端的负载驱动能力为 8 个 LS 型 TTL(低功耗甚高速 TTL)负载。

此引脚的第二功能 PROG 在对片内带有 4KB EPROM 的 8751 编程写入(固

化程序)时,作为编程脉冲输入端。

PSEN(29 脚):程序存储允许输出信号端。在访问片外程序存储器时,此端定

时输出负脉冲作为读片外存储器的选通信号。此引肢接 EPROM 的 OE 端(见后面

几章任何一个小系统硬件图)。PSEN 端有效,即允许读出 EPROM/ROM 中的

指令码。PSEN 端同样可驱动 8 个 LS 型 TTL 负载。要检查一个 8051/8031 小

系统上电后 CPU 能否正常到 EPROM/ROM 中读取指令码,也可用示波器看

PSEN 端有无脉冲输出。如有则说明基本上工作正常。

EA/Vpp(31 脚):外部程序存储器地址允许输入端/固化编程电压输入端。当

EA 引脚接高电平时,CPU 只访问片内 EPROM/ROM 并执行内部程序存储器中的

指令,但当 PC(程序计数器)的值超过 0FFFH(对 8751/8051 为 4K)时,将自动转去

执行片外程序存储器内的程序。当输入信号 EA 引脚接低电平(接地)时,CPU 只

访问外部 EPROM/ROM 并执行外部程序存储器中的指令,而不管是否有片内程

序存储器。对于无片内 ROM 的 8031 或 8032,需外扩 EPROM,此时必须将 EA

引脚接地。此引脚的第二功能是 Vpp 是对 8751 片内 EPROM 固化编程时,作为

施加较高编程电压(一般 12V~21V)的输入端。

3.输入/输出端口 P0/P1/P2/P3:

P0 口(P0.0~P0.7,39~32 脚):P0 口是一个漏极开路的 8 位准双向 I/O 口。

作为漏极开路的输出端口,每位能驱动 8 个 LS 型 TTL 负载。当 P0 口作为输入

口使用时,应先向口锁存器(地址 80H)写入全 1,此时 P0 口的全部引脚浮空,可作

为高阻抗输入。作输入口使用时要先写 1,这就是准双向口的含义。在 CPU 访问

片外存储器时,P0 口分时提供低 8 位地址和 8 位数据的复用总线。在此期间,P0

口内部上拉电阻有效。

P1 口(P1.0~P1.7,1~8 脚):P1 口是一个带内部上拉电阻的 8 位准双向 I/O

口。P1 口每位能驱动 4 个 LS 型 TTL 负载。在 P1 口作为输入口使用时,应先向

P1 口锁存地址(90H)写入全 1,此时 P1 口引脚由内部上拉电阻拉成高电平。

P2 口(P2.0~P2.7,21~28 脚):P2 口是一个带内部上拉电阻的 8 位准双向 I/O

口。P 口每位能驱动 4 个 LS 型 TTL 负载。在访问片外 EPROM/RAM 时,它输

出高 8 位地址。

P3 口(P3.0~P3.7,10~17 脚):P3 口是一个带内部上拉电阻的 8 位准双向 I/O

口。P3 口每位能驱动 4 个 LS 型 TTL 负载。P3 口与其它 I/O 端口有很大的区别,

它的每个引脚都有第二功能,如下:

P3.0:(RXD)串行数据接收。

P3.1:(RXD)串行数据发送。

P3.2:(INT0#)外部中断 0 输入。

P3.3:(INT1#)外部中断 1 输入。

P3.4:(T0)定时/计数器 0 的外部计数输入。

P3.5:(T1)定时/计数器 1 的外部计数输入。

P3.6:(WR#)外部数据存储器写选通。

剩余41页未读,继续阅读

yyyyyyhhh222

- 粉丝: 442

- 资源: 6万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C++多态实现机制详解:虚函数与早期绑定

- Java多线程与异常处理详解

- 校园导游系统:无向图实现最短路径探索

- SQL2005彻底删除指南:避免重装失败

- GTD时间管理法:提升效率与组织生活的关键

- Python进制转换全攻略:从10进制到16进制

- 商丘物流业区位优势探究:发展战略与机遇

- C语言实训:简单计算器程序设计

- Oracle SQL命令大全:用户管理、权限操作与查询

- Struts2配置详解与示例

- C#编程规范与最佳实践

- C语言面试常见问题解析

- 超声波测距技术详解:电路与程序设计

- 反激开关电源设计:UC3844与TL431优化稳压

- Cisco路由器配置全攻略

- SQLServer 2005 CTE递归教程:创建员工层级结构

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功