SYNOPSYS 基于 SystemVerilog 语言的验证方法学

- 5 -

生并调试一个测试,一个有十验证工程师的团队(也是一个乐观估计)将花费超过一年完

成所有测试。因此提升验证产量的唯一方法是减少产生测试所消耗时间。

SysemVerilog 具有丰富语言能力,能描述复杂验证环境,包括带约束随机激励产生,

面向对象编程,功能覆盖统计。这些特点使用户开发出能自动产生大量验证情节的测试平

台。

《

VMM for SystemVerilog

》

展示了如何用 SysemVerilog 语言功能构建一个自动化验证

平台。建立一个验证环境时,采用正确策略,充分利用自动化特点,产生一个新测试所消

耗时间将显著减少。应用带约束随机激励产生方法,在可控制规则,或用户自定义约束下

以自动方式产生测试情节。验证中很重要一点在于测试平台质量,这样附加的测试可在对

一系列基本测试用例基础上进行简单调整测试参数或加入定义好的约束而产生。通过这种

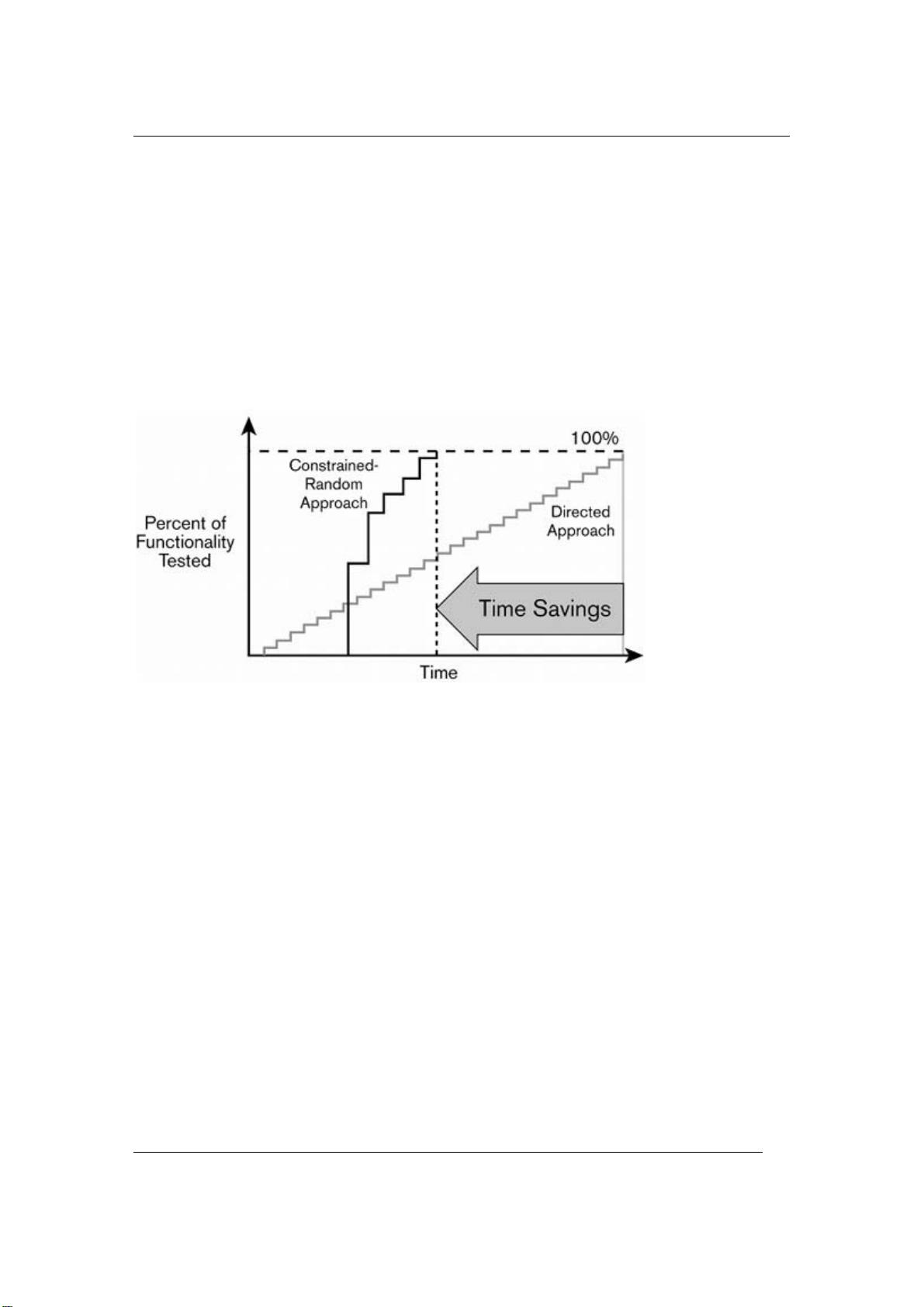

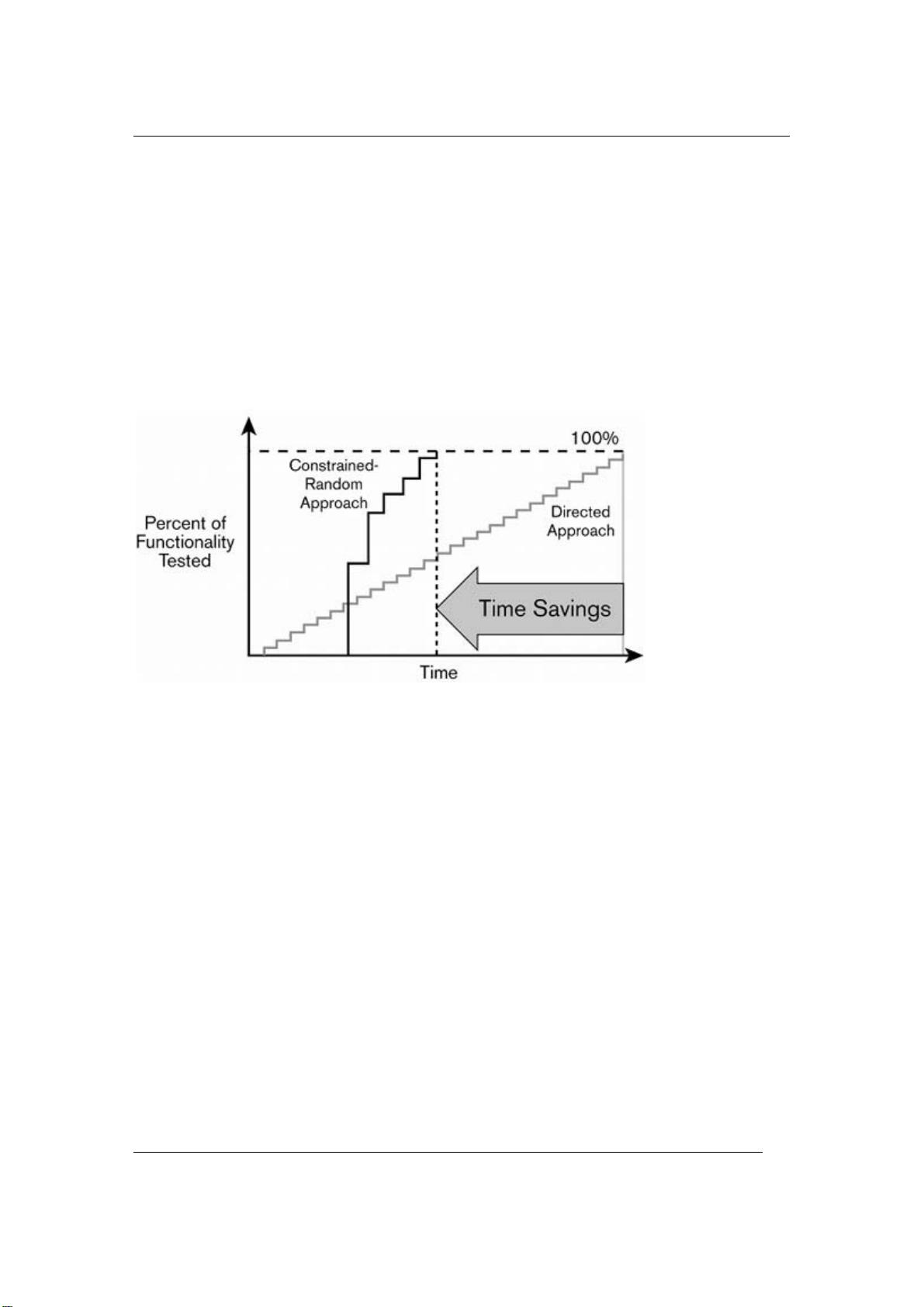

方法获得好处在图 1 中说明。

Figure 1 自动测试相对于直接测试有更高效率

用直接测试方法,产生一个新测试所需要时间相对固定,因此功能验证质量提高与时

间基本成线型关系。而一个带约束随机验证环境,在第一次能正常测试之前有一个前期投

入消耗。此投入用于建立验证环境中参数化配置能力,以及约束测试中相关部分,使得之

后测试更容易基于约束驱动。

测试情节类型中建立随机化,不仅仅是产生新数据值,更增加了测试击中边界条件

(corner case)可能性,从而发现更多设计缺陷。下一部分还将讨论,这样的测试用例也

能击中更多覆盖点,加速验证收敛。

SystemVerilog 提供了带约束随机激励测试所需要的所有验证语言结构。

《

VMM for

SystemVerilog

》

提供了如何建立一个带约束随机环境,如何运用面向对象编程技术编写可

重用验证单元,如何在整个项目验证,或跨项目之间重用验证单元的整套方法。

1.4 覆盖率驱动验证

贯穿验证过程中的覆盖率测量数据有两方面重要作用。一方面能明确指出设计中还没

有被充分验证到的部分,确定验证过程中空洞。通过回答下一步如何去做这样的关键问

题,有助于指引验证需要努力的方向。比如,需要补充编写哪些直接测试用例,如何改变

参数用于带约束的随机测试。

另一方面,覆盖率测量是验证已经足够充分,可进行流片的指示器。覆盖率不仅仅简

单提供是或否这样结果。覆盖率增量提升,用于评估验证进度,增加开发团队进行流片时