异构多核运动控制器:高速接口与固件设计

172 浏览量

更新于2024-09-01

收藏 355KB PDF 举报

"基于异构多核运动控制器的高速接口设计"

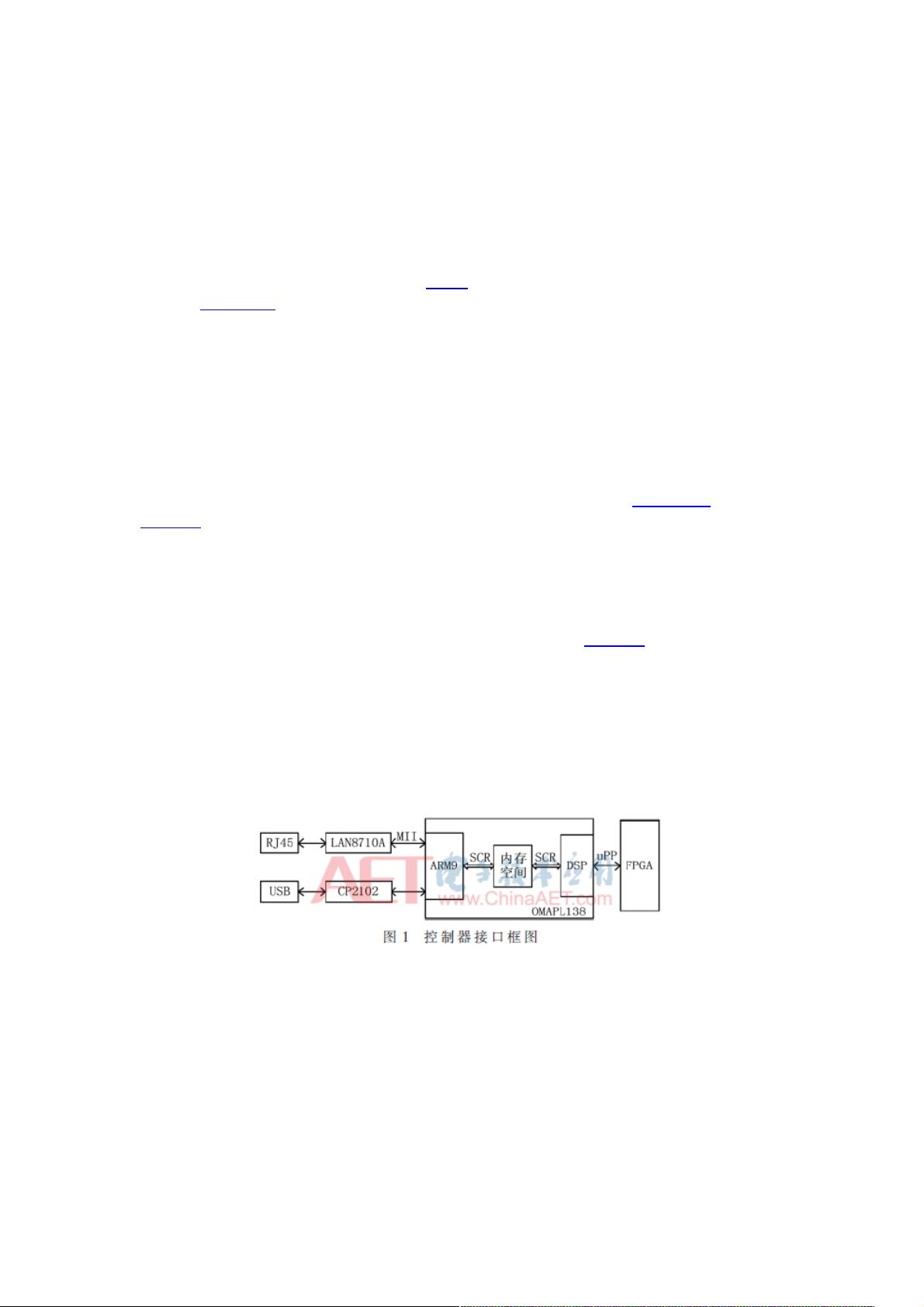

在嵌入式运动控制领域,异构多核架构已经成为提升系统性能的关键技术。本文针对现有的控制器在数据通信接口方面的不足,提出了一种基于OMAPL138+FPGA的异构多核运动控制器设计方案,该控制器核心由集成ARM9和DSP C6748的OMAPL138处理器构成。ARM9处理器负责运行Linux操作系统,以实现多任务的高效协调,而无操作系统的DSP则确保了实时计算性能。

高速接口设计是本文的重点,主要包括ARM与DSP之间的通信、DSP与FPGA的连接以及控制器与个人计算机(PC)的交互。ARM与DSP的通信通常涉及复杂的同步和数据交换机制,为了优化这一过程,可以采用特定的协议和硬件支持,如共享内存、DMA(直接存储器访问)等,以减少CPU干预,提高数据传输速率。另一方面,DSP与FPGA之间的接口设计可能涉及到FPGA的逻辑配置,例如通过配置FPGA中的双端FIFO(先进先出缓冲区)来实现高效的数据流控制。

FPGA在运动控制中的作用主要是实现高速IO扩展和定制逻辑,它可以快速响应并处理实时控制信号。对于控制器与PC的通信,传统的低速串行接口如RS232已经无法满足高速数据传输的需求,因此,通常会采用USB、以太网或更高速的串行总线如PCIe,以实现大吞吐量的通信。

文中提到的TI OMAPL138处理器,结合了ARM和DSP的优势,是多核协同处理的理想选择。SysLink组件的使用使得双核间的通信更为简洁,降低了软件设计的复杂度。然而,引入操作系统可能会影响DSP的实时性能,因此在设计时需要权衡实时性和多任务处理能力。

本文提出的异构多核运动控制器通过优化通信接口,提高了数据交换速率和系统的稳定性,为其他类似设计提供了有价值的参考。未来的研究可能涉及更复杂的多核架构、更高的通信带宽以及更优化的固件设计,以适应更加复杂和多样化的需求。这样的设计趋势将推动嵌入式运动控制系统的性能边界,满足智能制造领域日益增长的高性能要求。

2020-08-26 上传

2023-05-10 上传

2023-04-23 上传

2023-05-11 上传

2023-08-23 上传

2023-04-01 上传

2023-06-11 上传

2023-05-22 上传

2023-09-12 上传

weixin_38689922

- 粉丝: 6

- 资源: 915

最新资源

- C++标准程序库:权威指南

- Java解惑:奇数判断误区与改进方法

- C++编程必读:20种设计模式详解与实战

- LM3S8962微控制器数据手册

- 51单片机C语言实战教程:从入门到精通

- Spring3.0权威指南:JavaEE6实战

- Win32多线程程序设计详解

- Lucene2.9.1开发全攻略:从环境配置到索引创建

- 内存虚拟硬盘技术:提升电脑速度的秘密武器

- Java操作数据库:保存与显示图片到数据库及页面

- ISO14001:2004环境管理体系要求详解

- ShopExV4.8二次开发详解

- 企业形象与产品推广一站式网站建设技术方案揭秘

- Shopex二次开发:触发器与控制器重定向技术详解

- FPGA开发实战指南:创新设计与进阶技巧

- ShopExV4.8二次开发入门:解决升级问题与功能扩展