微处理器系统中的74LS90应用:接口与控制逻辑详解

发布时间: 2024-11-29 19:47:47 阅读量: 48 订阅数: 30

基于STM8单片机的CAT24WCxx存储器实验(I2C模拟方式).zip

参考资源链接:[74LS90引脚功能及真值表](https://wenku.csdn.net/doc/64706418d12cbe7ec3fa9083?spm=1055.2635.3001.10343)

# 1. 微处理器系统接口基础

在微处理器系统中,微处理器与外设之间的通信至关重要。这一章节我们将介绍微处理器系统接口的基础知识,为理解后续的集成电路与微处理器系统之间的交互打下坚实的基础。

## 接口的作用与要求

微处理器系统接口是微处理器与外部设备之间信息交换的通道,它决定了系统数据传输的速率、稳定性和兼容性。为了确保这些特性,接口设计需要满足以下几个基本要求:

- **同步机制**:保证数据在微处理器和外设之间以相同的时钟速率准确传输。

- **数据宽度**:决定一次可以传输的数据量,通常与数据总线宽度相对应。

- **电气特性**:必须符合微处理器和外设的电气标准,以防止损坏。

## 接口的类型

接口类型通常分为两种:并行接口和串行接口。并行接口允许同时传输多位数据,而串行接口一次只传输一位。虽然并行接口速度快,但串行接口因硬件简化和成本低而越来越受到青睐。

为了进一步理解这些概念,我们会通过后续章节详细探讨74LS90集成电路的应用及其在微处理器系统中的关键角色。

# 2. ```

# 第二章:74LS90集成电路概述

## 2.1 74LS90的功能与特点

### 2.1.1 74LS90的工作原理

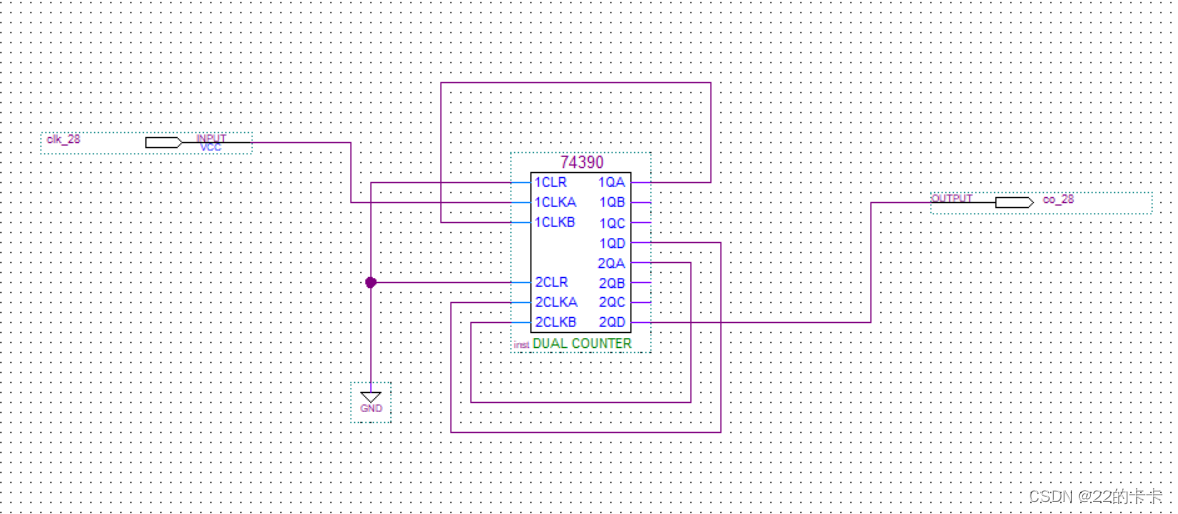

74LS90是一种双十进制计数器,包含两个独立的可重置的4位计数器。在内部,它由两个5级的二进制计数器组成,具有与输入脉冲同步的输出。这两个计数器可分别设置为二进制计数(模 2)或十进制计数(模 10),还可以级联以形成模 20 的计数器。

74LS90工作时,当计数器的计数达到预设值时,它会在输出端产生一个高电平信号。这个特性让它在数字逻辑电路中作为频率分频器或定时器。它常用于产生精确的时序控制信号,因为它的输出可直接用于触发其他逻辑电路的切换。

此外,74LS90有两个可预置的输入端,允许计数器在计数前被设置到一个特定的值。这种预置功能在需要精确的初始化状态时特别有用,比如在复杂的计时或排序操作中。

### 2.1.2 74LS90的封装与引脚配置

74LS90采用标准的14脚双列直插封装(DIP)。其引脚配置如下:

- 第1脚到第4脚和第7脚到第10脚:两个计数器的计数输入端。

- 第5脚和第12脚:这两个引脚是两个独立计数器的复位端,可用于将计数器的计数值重置为零。

- 第6脚:时钟输入端,用于接收外部时钟信号。

- 第11脚和第13脚:这两个引脚用于输出,可以提供计数器的当前状态。

- 第14脚:Vcc,正电源电压。

- 第7脚:GND,接地端。

了解引脚配置是正确使用74LS90的前提。正确连接这些引脚可确保电路板上其他组件能够正确地与计数器进行信号交互。

## 2.2 74LS90与其他逻辑电路的连接

### 2.2.1 与数字逻辑电路的接口设计

连接74LS90到数字逻辑电路时,通常需要考虑以下几点:

- 信号同步:确保时钟信号和复位信号能够与系统时钟同步,防止时序混乱。

- 负载能力:74LS90输出端的负载能力可能不足以驱动后续的逻辑门,可能需要使用缓冲器或驱动器。

- 电源滤波:为了确保电源稳定,避免干扰,需要在电源线和地线之间使用合适的去耦电容。

```mermaid

flowchart LR

A[时钟信号源] -->|同步| B(74LS90时钟输入)

B -->|计数| C[计数器输出]

D[复位信号源] -->|复位| B

C -->|驱动| E[后续逻辑电路]

B -.-> F[去耦电容]

F -->|稳压| G[Vcc]

G -.-> H[地线]

```

### 2.2.2 74LS90在多级计数器中的应用

在设计多级计数器时,74LS90可级联使用,以实现更高位数的计数。例如,两个74LS90可以组成一个模20的计数器。连接时,前级的计数器的进位输出连接到下一级的时钟输入,从而同步两个计数器。

```mermaid

flowchart LR

A[74LS90级联输入] -->|时钟信号| B[初级74LS90计数器]

B -->|进位输出| C[次级74LS90计数器]

B -->|计数输出| D[控制逻辑]

C -->|计数输出| D

```

在连接时,还需注意:

- 时钟信号应该有良好的边缘,以确保计数器能够正确地对每个脉冲响应。

- 考虑到信号完整性,为了避免反射和串扰,应当尽量减少信号路径长度。

- 同时,还应确保所有的电源和地线连接良好,以提供稳定的供电。

通过以上步骤,可以保证74LS90在复杂系统中的正确应用,并且实现稳定可靠的计数功能。

```

请注意,由于Markdown内容长度的限制,在实际应用中,以上内容应根据实际需要进行扩展,以满足章节长度要求。

# 3. 74LS90在微处理器系统中的应用

在现代微处理器系统设计中,集成电路的正确应用是保证系统功能完整性和性能表现的关键因素之一。74LS90作为一个广泛使用的十进制计数器,它在微处理器系统中的集成不仅仅局限于数字计数功能。本章将深入探讨74LS90在微处理器系统中的接口技术,以及在控制逻辑中的关键作用,从而了解其在系统设计中的多维应用。

## 3.1 74LS90与微处理器的接口技术

### 3.1.1 地址解码与控制信号生成

在微处理器系统中,74LS90通常用于扩展地址空间,以及生成特定的控制信号。通过地址解码,微处理器可以识别并选择特定的外设或内存区域。为此,74LS90可以配置为分频器,为地址解码逻辑提供不同的时钟信号。以下是实现地址解码的基本逻辑:

```verilog

module address_decoder(

input wire [15:0] address, // 16-bit address bus

output reg chip_select // active-low chip select signal

);

always @(address) begin

// Example: Select a specific address range

if(address >= 16'h8000 && address <= 16'h8FFF)

chip_select = 0; // Active-low signal asserted

else

chip_select = 1; // Deasserted for other addresses

end

endmodule

```

在上述Verilog代码中,通过监测地址总线,特定地址范围内的设备被选择。74LS90可以进一步细分成子地址,以识别和选择子设备。

### 3.1.2 数据总线与控制总线的集成

除了地址总线,数据总线和控制总线也是微处理器系统的关键部分。74LS90可以在数据传输中提供同步机制,确保数据在正确的时间被读取或写入。控制总线涉及到系统中各种控制信号的生成,例如读写使能信号。以下是一个使用74LS90生成控制信号的示例:

```verilog

module control_signal_generator(

input wire clk

```

0

0