教育领域的74LS90示范应用:教学与实验的创新方法

发布时间: 2024-11-29 20:10:02 阅读量: 27 订阅数: 31

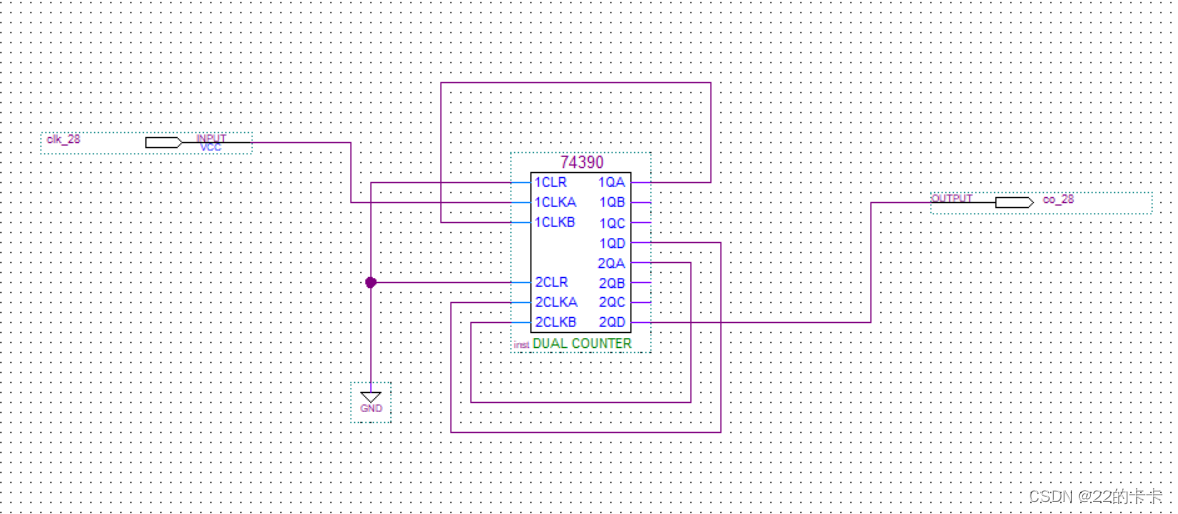

基于Multisim的74LS90数字钟带整点报时

参考资源链接:[74LS90引脚功能及真值表](https://wenku.csdn.net/doc/64706418d12cbe7ec3fa9083?spm=1055.2635.3001.10343)

# 1. 74LS90在教育领域的应用概述

## 1.1 教育领域的数字化转型

随着技术的不断进步,教育领域也迎来了数字化转型的新浪潮。在这一背景下,集成电路在教育实验设备中的应用变得尤为重要。74LS90作为一种经典的中规模集成电路(MSI),在教育实验中具有不可替代的作用,其不仅为学生提供了实践数字逻辑设计的机会,而且通过实际操作帮助他们理解数字电路的基本原理。

## 1.2 74LS90的教育价值

74LS90以其简单易懂、功能丰富等特性,成为教育领域中数字电路和微处理器课程的理想教学工具。在教学中应用74LS90可以帮助学生构建扎实的理论基础,并通过实验将理论知识与实践相结合,从而提高他们的动手能力和创新思维。

## 1.3 应用场景和实际效益

在教学实践中,74LS90被广泛应用于构建计数器、分频器、定时器等基础电路。这些实践不仅为学生提供了一个探究电子元件及其相互作用的平台,还能激发他们对于电子工程和技术科学的兴趣,为未来的学术研究或职业发展打下坚实的基础。

# 2. 74LS90基础理论与特性

## 2.1 74LS90的内部结构

### 2.1.1 引脚布局和功能描述

74LS90是一种广泛应用于数字电子学领域的双十进制计数器,具有两位二进制计数器的功能。其封装形式多为14脚双列直插封装(DIP),为便于理解和应用,以下是74LS90的主要引脚布局和功能描述:

- **Vcc** (Pin 14):正电源端,连接到+5V供电。

- **GND** (Pin 7):接地端。

- **CLK** (Pin 1):时钟输入端,用于接收外部时钟信号来驱动计数器。

- **R0, R1** (Pin 2, 15):异步复位输入端,当这两个端子同时接地时,计数器将被重置。

- **Q0, Q1, Q2, Q3** (Pin 3, 4, 12, 13):输出端,Q0和Q1为低位输出,Q2和Q3为高位输出。

- **MR** (Pin 10):主复位端,通常连接到高电平,以保持计数器正常工作。

- **Enable P, Enable T** (Pin 11, 9):分别为P和T型计数器的使能端。

在设计电路时,正确连接这些引脚至关重要,特别是在引脚2和15连接至接地以保证计数器的正确复位。

### 2.1.2 74LS90的工作原理

74LS90通过其内部的触发器来实现计数逻辑。该芯片可以配置为模10(十进制)计数器或模2计数器,具体取决于引脚的连接方式。二进制计数器的工作模式基于触发器的翻转动作,每个触发器代表一个二进制位,每当一个脉冲信号到来时,最低位的触发器就会改变状态,从而实现计数。

当P和T使能端(Enable P 和 Enable T)同时接收到高电平时,计数器开始计数;若任一使能端接收到低电平,计数器停止计数。异步复位端(R0和R1)的作用是将计数器重置为初始状态,一般情况下都接地。

在理解了74LS90的基本工作原理之后,就能够更好地把握其在不同应用中的配置方式和工作模式,进而实现更复杂的功能。

## 2.2 74LS90的逻辑功能

### 2.2.1 二进制计数器的工作模式

74LS90的二进制计数器模式可以通过其引脚的不同连接方式来实现。当使能端(Enable P 和 Enable T)都为高电平时,每接收到一个时钟脉冲,输出端Q0到Q3就会变化一次,这样就可以在Q0到Q3上得到一个二进制数的序列,即二进制计数。

该计数器是可逆的,也就是说,它能够通过调整内部的逻辑电路,实现正向计数或反向计数。通过设置不同的输入,可以得到不同的计数序列和计数方向。例如,将时钟输入信号分为两路,一路正向输入,一路反向输入,即可实现正反计数。

### 2.2.2 分频功能的实现原理

74LS90的分频功能是通过其输出端口与外部电路的连接来实现的。具体来说,分频功能通常在某个计数器达到一定计数值之后,由输出端口的信号触发外部电路动作,从而实现信号频率的降低。

例如,若将74LS90配置为模10计数器,那么每经过10个时钟脉冲,输出端口就会产生一个周期性的信号。通过适当的逻辑电路设计,可以使得每当输出端口的特定位从高电平变为低电平(或反之)时,产生一个脉冲信号,该信号的频率是原时钟信号频率的1/10。

分频功能在数字电路设计中十分关键,特别是在需要降低信号频率的场合,能够有效地提升数字系统的性能和稳定性。

## 2.3 74LS90的应用优势

### 2.3.1 与其他集成电路的对比分析

在众多的计数器集成电路中,74LS90凭借其简单的设计、易操作性以及低成本优势脱颖而出。相较于其他集成电路,如74HC595(移位寄存器)等,74LS90在功能和应用上具有明显的特点。

74LS90以其能够提供分频和计数两种基本功能,成为许多简单计数和分频任务的理想选择。它的设计简单,使用起来较为直观,用户容易上手,因此非常适合作为教育工具。

### 2.3.2 教育实验中的适用性探讨

在教育实验中,74LS90的适用性体现在其能够帮助学生直观地理解数字逻辑电路的工作原理。74LS90的引脚数量适中,并且功能模块划分明确,这使得学生能够在实验中逐一探究每个引脚的作用以及它们之间的逻辑关系。

同时,74LS90易于接入常见的面包板和焊接板,这对于学生进行项目式学习和实验探究尤为有利。学生通过操作74LS90,能够更加深刻地体会到数字逻辑在实际应用中的重要性,这无疑有助于提高他们对电子工程学科的兴趣和掌握程度。

### 表格:74LS90与其他集成电路的比较

| 特性 | 74LS90 | 74HC595 | 其他IC |

|-------------------|------------|------------|------------|

| 供电电压 | +5V | 2V to 6V | 变化 |

| 静态电流 | 10mA | 80uA | 变化 |

| 计数模式 | 可配置 | 固定 | 变化 |

| 复位方式 | 异步复位 | 同步复位 | 变化 |

| 频率范围 | 32MHz | 30MHz | 变化 |

| 封装形式 | DIP14 | SOIC16 | 多样 |

通过上述表格的对比分析,我们可以发现74LS90在某些方面具有较为明显的优势,尤其适合在成本敏感或对设计简便性有特殊要求的教育实验中使用。

### 代码块:74LS90基本计数功能的模拟

```verilog

module counter_74LS90(

input clk, // 时钟信号

input reset_n, // 异步复位信号,低电平有效

output reg [3:0] out // 四位输出

);

always @(posedge clk or negedge reset_n) begin

if (!reset_n)

out <= 4'b0000; // 异步复位输出为0

else

out <= out + 1'b1; // 正向计数

end

endmodule

```

在这个Verilog代码示例中,我们模拟了74LS90的基本计数功能。这是一个非常简单的模块,用于演示如何通过代码实现计数器的行为。每一帧时钟信号上升沿触发时,输出值`out`都会增加1。若检测到复位信号`reset_n`为低电平,则计数器会被异步复位到0。

### 逻辑分析:

- *

0

0