74LS90引脚功能扩展:多用途设计思路与应用技巧

发布时间: 2024-11-29 19:52:03 阅读量: 73 订阅数: 30

74ls283引脚图及功能_极限值及应用电路

参考资源链接:[74LS90引脚功能及真值表](https://wenku.csdn.net/doc/64706418d12cbe7ec3fa9083?spm=1055.2635.3001.10343)

# 1. 74LS90概述与引脚功能解析

数字电路世界中,74LS90是一个经典的中规模集成电路(MSI),它由两个独立的可预置的四位二进制计数器组成,广泛用于数字系统的设计。本章将介绍74LS90的基本概念和引脚功能,为深入理解后续内容打下坚实基础。

## 1.1 74LS90的基本介绍

74LS90是一个双4位二进制计数器,它以十进制计数为特点,每个计数器都能独立工作。这种双计数器结构使得它非常适合于多种计数、分频和定时应用。

## 1.2 引脚功能详解

74LS90拥有14个引脚,各个引脚的功能如下:

- **Vcc (14脚) 和 GND (7脚)**:分别为正电源和接地端。

- **计数器输入端 (1, 10脚)**:提供时钟信号输入到两个独立计数器。

- **输出端 (2-6, 9脚)**:连接到两个计数器的四个输出位。

- **清零端 (13脚)**:同时清除两个计数器的计数,使输出回到初始状态。

- **置位端 (11, 12脚)**:用于设置计数器的计数值。

- **进位输出 (7脚)**:一个计数器的进位输出可作为另一个计数器的时钟输入,实现级联。

- **二进制与十进制模式切换端 (8, 15脚)**:通过选择不同的连接方式,可以实现二进制或十进制的计数模式。

通过对这些引脚的了解,我们可以开始探讨74LS90的更多高级功能和应用。下一章将深入分析74LS90的基本工作原理。

# 2. 74LS90的基本工作原理

### 2.1 74LS90的内部结构

在深入探讨74LS90的工作原理之前,我们先要了解其内部结构。74LS90是一款二进制计数器,它有两个独立的计数单元,可以配置为同步二进制计数器或者十进制计数器。

#### 计数器的基本构成

74LS90的内部由两个独立的四位二进制计数器构成,计数器的位数可通过外部接线方式来配置。每个计数器模块都包含触发器和门电路等基本逻辑组件。触发器负责存储当前的计数值,而门电路则负责根据输入信号更新触发器的状态。

### 2.2 74LS90的工作模式

74LS90可作为二进制计数器或者十进制计数器使用,并能通过接线轻松切换工作模式。此外,通过将多个74LS90连接在一起,可以实现多位计数的需求。

#### 二进制与十进制模式的切换

74LS90支持两种计数模式:二进制模式和十进制模式。在二进制模式下,计数器按照2的幂次方递增计数。而在十进制模式下,计数器的计数范围从0到9循环。通过不同引脚的逻辑电平配置,用户可实现模式的切换,具体配置可参考数据手册。

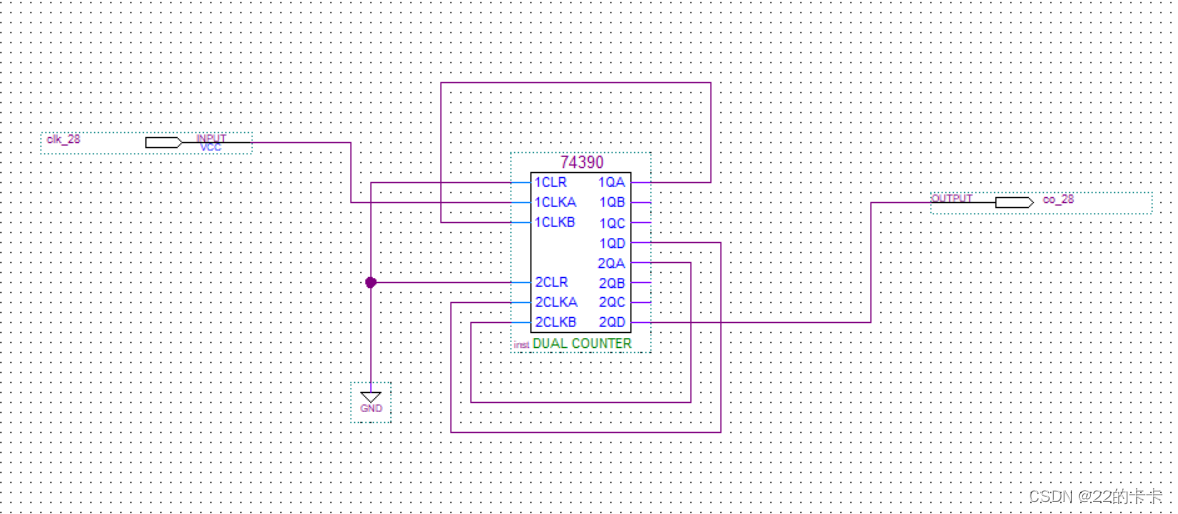

#### 连接多个74LS90实现多位计数

若要实现超过四位的计数,可以将多个74LS90计数器级联。例如,通过将一个74LS90的输出连接到另一个74LS90的计数输入端,就可以创建一个八位计数器。为了同步计数,需要正确配置时钟信号和清零信号。

### 2.3 74LS90的时钟和控制信号

时钟信号是计数器的核心,而控制信号用于重置或设置计数器的初始状态。

#### 时钟信号的输入与输出

时钟信号是通过计数器的时钟输入端(通常标记为CLK)接收。每到来一个有效的时钟脉冲,计数器的内部计数状态就会更新一次。某些74LS90版本可能具有输出端,用于输出经过计数器的时钟信号,以便于级联多个计数器。

#### 清零和置位功能的实现

清零(CLR)和置位(PRE)功能用于初始化计数器的状态。通常情况下,清零功能将计数器复位为0,而置位功能可以将计数器预设为特定值,比如二进制计数器中预设为1。这些功能通过外部控制信号实现,并常用于同步或复位计数器状态。

接下来章节的内容将会继续探讨74LS90的应用和设计思路,提供丰富的案例分析与技巧说明,敬请期待。

# 3. 74LS90多用途设计思路

## 3.1 定制计数器设计

### 3.1.1 设计不同范围的计数器

设计不同范围的计数器是数字电路中的基础应用之一。通过使用74LS90,我们可以创建出满足特定需求的计数器。例如,可以设计一个从0计数到99的双位十进制计数器。这个设计需要两个74LS90 ICs,每个IC设置为一个4位的二进制计数器,并将它们级联起来形成一个十进制计数器。

```mermaid

flowchart LR

A[输入时钟信号] --> B[十位74LS90]

B --> C[个位74LS90]

C --> D[输出]

```

**代码逻辑分析与参数说明:**

```verilog

// Verilog代码示例,描述了如何控制74LS90的计数模式。

module counter_74LS90(

input wire clk, // 输入时钟信号

output reg [7:0] count // 8位输出计数

);

// 内部计数器变量

reg [3:0] counter十位 = 4'b0000;

reg [3:0] counter个位 = 4'b0000;

// 时钟边沿触发

always @(posedge clk) begin

if (counter个位 == 9) begin

counter个位 <= 0;

if (counter十位 == 9) begin

counter十位 <= 0;

end else begin

counter十位 <= counter十位 + 1;

end

end else begin

counter个位 <= counter个位 + 1;

end

end

// 将内部计数器值组合成输出

always @(*) begin

count = {counter十位, counter个位};

end

endmodule

```

### 3.1.2 设计模数可调的计数器

模数可调的计数器提供了一种灵活的计数解决方案。通过一些外部开关或逻辑电路,我们可以控制计数器在特定的数字停止计数。例如,设计一个模3、模5、模7计数器,需要外部逻辑电路来决定计数器达到哪个特定值后复位。这可以通过将74LS90的输出连接到逻辑门并返回到其复位输入来实现。

```mermaid

flowchart LR

A[输入时钟信号] -->|计数| B[74LS90计数器]

B --> C{复位条件检查}

C -->|达到设定值| D[复位信号]

C -->|未达到设定值| B

D --> E[复位74LS90]

```

**代码逻辑分析与参数说明:**

```verilog

// Verilog代码示例,描述了如何实现一个可调节模数的计数器。

module adjustable

```

0

0