【UVM序列器设计模式】:面向对象设计在序列器中的应用实例

发布时间: 2024-12-27 00:04:40 阅读量: 5 订阅数: 11

# 摘要

本文全面探讨了UVM序列器设计模式及其在面向对象设计中的应用。首先概述了UVM序列器设计模式的基本概念和面向对象设计理论基础,随后深入分析了工厂模式、单例模式和命令模式等在序列器中的具体应用。进一步,本文进阶探讨了模板方法模式、观察者模式和策略模式在序列器设计中的优化实现,并提出了一系列测试与验证策略来确保设计模式的正确性和应用效果。最后,文章展望了面向对象设计在序列器开发中的新趋势和教育意义,指出了设计模式的动态演变与融合,以及在教育和培训中的重要性。通过本文的研究,读者能够深入理解UVM序列器设计模式,并在实际项目中加以有效应用。

# 关键字

UVM序列器;面向对象设计;设计模式;工厂模式;单例模式;策略模式

参考资源链接:[UVMHarness:接口连接的便利工具](https://wenku.csdn.net/doc/6412b622be7fbd1778d45a15?spm=1055.2635.3001.10343)

# 1. UVM序列器设计模式概述

## 1.1 UVM序列器的作用与重要性

UVM(Universal Verification Methodology)是目前广泛使用的一种验证方法学,它提供了一套丰富的类库和组件,以实现可重用且高度模块化的验证环境。在UVM中,序列器(Sequencer)扮演着分发事务(Transactions)至驱动器(Drivers)的关键角色。序列器通过与序列(Sequences)协作来生成随机或预定的事务序列,这些事务最终会驱动被测设备(DUT)的行为。UVM序列器设计模式不仅仅是实现事务分发的手段,它们还是组织和优化验证环境复杂性的关键所在。

## 1.2 设计模式的定义与目的

设计模式是指在软件工程中,为了解决在特定上下文中反复出现的问题而总结出来的一套解决方案的模板。在UVM序列器的设计中,应用设计模式可以提高代码的可重用性,增强系统的灵活性和可维护性。此外,这些模式还能够简化复杂系统的理解,为验证工程师提供一种共同的术语和方法,以便在团队协作中有效地沟通和解决问题。

## 1.3 UVM序列器设计模式的分类与应用

UVM序列器设计模式可以大致分为创建型、结构型和行为型三类。例如,工厂模式用于创建序列的实例,单例模式确保序列器有一个全局可访问的唯一实例,而命令模式则用于封装请求并提供一种将请求排队或记录请求日志的方法。这些模式在UVM序列器设计中具有具体的应用场景,通过熟练掌握并恰当应用这些模式,可以显著提高UVM验证环境的构建效率和验证质量。在后续章节中,我们将深入探讨这些设计模式的具体应用实例和实现细节。

# 2. 面向对象设计理论基础

面向对象设计(Object-Oriented Design,OOD)是软件开发领域中的一个重要概念。它的核心是通过对象来设计软件系统,从而达到提高系统可复用性、可维护性和灵活性的目的。本章节将深入探讨面向对象设计的核心概念和设计模式在面向对象设计中的角色。

## 2.1 面向对象设计的核心概念

### 2.1.1 封装、继承与多态

封装(Encapsulation)、继承(Inheritance)和多态(Polymorphism)是面向对象设计的三大基本特征,它们共同构成面向对象技术的基础。

**封装**是指将对象的状态(属性)和行为(方法)包装在一起,构成一个独立的单元,并对外隐藏实现细节。封装保证了对象内部数据的安全性和稳定性,用户只能通过预定义的接口来访问这些数据。

**继承**是一种在类之间建立关系的机制,它允许一个类(子类)继承另一个类(父类)的属性和方法。通过继承,子类可以重用父类的代码,同时还可以扩展新的功能。

**多态**指的是同一个行为具有多个不同表现形式或形态的能力。在面向对象的程序设计中,多态允许我们使用相同的接口调用不同类型的对象,从而让程序更加灵活。

### 2.1.2 面向对象设计的原则

面向对象设计原则提供了构建软件系统时的最佳实践,主要包括以下几个方面:

- **单一职责原则(SRP)**:一个类应该只有一个引起它变化的原因。

- **开闭原则(OCP)**:软件实体应当对扩展开放,对修改关闭。

- **里氏替换原则(LSP)**:所有引用基类(父类)的地方能够透明地使用其子类的对象。

- **依赖倒置原则(DIP)**:高层模块不应该依赖低层模块,两者都应该依赖其抽象。

- **接口隔离原则(ISP)**:不应该强迫客户依赖于它们不用的方法。

- **合成复用原则**:尽量使用对象组合,而不是继承来达到复用的目的。

## 2.2 设计模式在面向对象设计中的角色

### 2.2.1 为何需要设计模式

设计模式是面向对象设计领域的一套被广泛认可的解决方案。它们提供了一种在特定上下文中解决常见设计问题的方法。设计模式并非完成的代码,而是一套如何用面向对象语言来解决某些设计问题的模板。

设计模式的出现主要是为了解决以下问题:

- 代码复用

- 降低系统复杂性

- 增加系统可维护性

- 促进团队协作

### 2.2.2 设计模式的分类及其重要性

根据它们的用途和目的,设计模式可以分为三大类:创建型模式、结构型模式和行为型模式。

- **创建型模式**关注对象创建的流程,包括单例、工厂方法、抽象工厂、建造者、原型模式等。

- **结构型模式**关注如何将对象和类组合成更大的结构,包括适配器、桥接、组合、装饰、外观、享元、代理模式等。

- **行为型模式**关注对象间的通信,包括责任链、命令、解释器、迭代器、中介者、备忘录、观察者、状态、策略、模板方法、访问者模式等。

设计模式的重要性在于:

- 为软件设计提供了经过验证的、通用的解决方案。

- 增强代码的可读性和系统的可维护性。

- 促进开发者之间的沟通和团队协作。

## 2.3 UVM序列器的面向对象特性

### 2.3.1 UVM序列器与面向对象设计

UVM(Universal Verification Methodology)是一种基于SystemVerilog语言的面向对象的验证方法学,它广泛应用于硬件功能验证领域。UVM序列器是UVM验证框架中用于生成和驱动测试事务的核心组件,它体现了面向对象设计的许多特性。

UVM序列器的面向对象特性包括:

- 使用类和对象来定义和管理事务序列。

- 利用继承机制来扩展序列器的功能。

- 使用接口和多态来实现不同的序列行为。

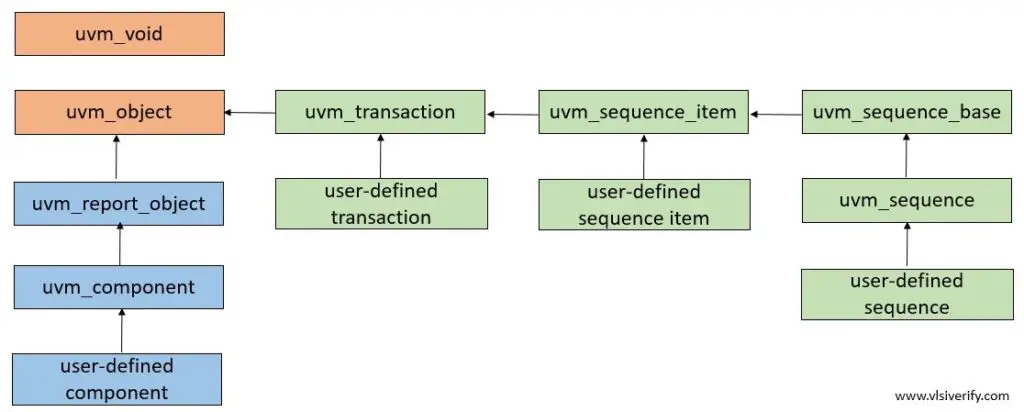

### 2.3.2 UVM序列器中的类与对象

在UVM中,序列器的类结构是层次化的,通常包含以下几种:

- **uvm_sequence**:基本序列类,用于产生事务序列。

- **uvm_sequence_item**:定义序列中事务的类型。

- **uvm_driver**:驱动事务,与DUT(Device Under Test)交互。

- **uvm_sequencer**:配合驱动,提供事务队列和事务分发。

这些类之间通过继承关系相互关联,构成UVM验证框架的骨架。对象实例化则是从这些类派生出具体事务序列的实例,并根据测试的需求来执行。

例如,创建一个基本的序列对象可以使用如下代码:

```systemverilog

class basic_sequence extends uvm_sequence #(my_transaction);

`uvm_object_utils(basic_sequence)

function new(string name = "basic_sequence");

super.new(name);

endfunction

virtual task body();

// 在这里实现事务序列的生成逻辑

endtask

endclass

```

在上述代码中,`basic_sequence`类继承自`uvm_sequence #(my_transaction)`,表示它是一个序列,且其管理的事务类型为`my_transaction`。在`body`任务中,我们可以定义如何生成事务序列。

通过UVM序列器的面向对象特性,验证工程师可以构建出结构清晰、易于维护和扩展的验证环境。

# 3. UVM序列器设计模式应用实践

## 3.1 工厂模式在序列器中的应用

### 3.1.1 工厂模式的原理

工厂模式是一种创建型设计模式,它提供了一种创建对象的最佳方式。工厂模式用于创建对象而不必指定将要创建的对象的具体类。工厂模式解决的主要问题是对象的创建和使用分离,使得对象的创建过程对用户透明。

在UVM序列器设计中,工厂模式可以用来创建序列或事务对象,这样用户就不需要知道对象是如何创建的,也不需要直接实例化具体的序列或事务类。工厂模式的具体实现通常包括一个工厂类,该类包含一个静态方法用于返回新创建的对象实例。

### 3.1.2 实例分析:UVM序列工厂的实现

在UVM中,序列器工厂通常与`uvm_factory`接口一起使用。这个接口允许通过`uvm_component_utils`宏注册类,并通过工厂方法来获取类的实例。下面是一个简单示例来展示如何在UVM序列器中应用工厂模式:

```verilog

class my_sequence extends uvm_sequence;

// ...

endclass

`uvm_object_utils(my_sequence)

class my_driver extends uvm_driver;

// ...

endclass

`uvm_component_utils_begin(my_driver)

`uvm_field_string(name, UVM_DEFAULT)

`uvm_field_enum(transaction_type, trans_type, UVM_DEFAULT)

`uvm_component_utils_end

// 在test或sequence item中使用工厂来创建序列

function void build_phase(uvm_phase phase);

my_sequence seq;

if (!uvm_factory::get().create_object_by_name("my_sequence", this, seq)) begin

`uvm_fatal("SEQCREATE", "Failed to create sequence my_sequence")

end

endfunction

```

0

0