【UVM高级编程技术】:OOP在UVM中的巧妙运用

发布时间: 2024-12-26 22:43:49 阅读量: 6 订阅数: 10

# 摘要

本文详细介绍了UVM(Universal Verification Methodology)高级编程技术,涵盖了面向对象编程(OOP)在UVM中的应用、UVM的高级编程技巧与实践、测试环境的构建与优化,以及高级编程案例分析。文中阐述了OOP核心概念在UVM中的实现,比如类、对象、继承与多态,以及封装和抽象。进一步探讨了UVM的高级组件如寄存器模型、通信代理、预测器等的设计与应用,以及测试平台架构、覆盖率驱动开发(CDV)和性能分析等的优化策略。通过案例分析,本文还提供了UVM在复杂硬件验证中的具体实现和脚本化自动化测试的策略。本文旨在为UVM用户提供深入理解和应用UVM高级技术的参考。

# 关键字

UVM高级编程;面向对象编程;寄存器模型;通信代理;预测器;性能优化;覆盖率驱动开发;自动化测试

参考资源链接:[UVMHarness:接口连接的便利工具](https://wenku.csdn.net/doc/6412b622be7fbd1778d45a15?spm=1055.2635.3001.10343)

# 1. UVM高级编程技术概述

## 1.1 UVM的起源和重要性

UVM(Universal Verification Methodology)是一种用于集成电路设计验证的开放标准,由Accellera组织推动。它融合了面向对象的编程方法和系统级验证需求,提供了丰富的库和预定义的组件,极大地提高了验证效率。UVM以IEEE1800.1-2012标准为蓝本,是验证工程师首选的验证平台。

## 1.2 高级编程技术在UVM中的作用

在UVM环境中,高级编程技术是构建灵活、可重用、高效的验证环境的关键。这些技术包括面向对象编程(OOP)、模板编程、测试计划和策略设计等。掌握这些技术能够帮助设计和实现复杂的硬件验证环境,同时提高代码的可维护性和测试的深度与广度。

## 1.3 UVM的学习路径和资源

对于初学者而言,学习UVM通常从基础的OOP概念开始,逐步深入到UVM的组件、序列、配置管理等。实践是最好的学习方式,建议通过真实的项目案例或者模拟设计来巩固理论知识。相关书籍、官方文档以及各种在线课程资源,都是提升UVM技能的有力工具。此外,参与开源项目或社区讨论也可以加速学习过程。

# 2. 面向对象编程(OOP)在UVM中的应用基础

## 2.1 面向对象编程(OOP)核心概念

### 2.1.1 类、对象、继承与多态

在面向对象编程(OOP)中,类(Class)是定义对象(Object)属性和行为的蓝图或模板。对象是类的实例化,而继承(Inheritance)是类与类之间的层次关系,它允许一个类继承另一个类的属性和方法,从而可以重用代码和扩展新的功能。多态(Polymorphism)则是指相同的行为或方法,可以适用于不同的对象,使得代码具有更好的灵活性和扩展性。

在UVM(Universal Verification Methodology)中,OOP的概念被广泛应用于其结构和组件中。例如,UVM中的`uvm_driver`是一个类,而`my_driver`是这个类的实例(对象)。`uvm_driver`可能继承自`uvm_component`,从而获得所有组件通用的功能,如报告、时间跟踪等。通过多态,可以在不同的`uvm_driver`子类中用相同的方法名来实现不同的行为。

### 2.1.2 封装和抽象在UVM中的实现

封装是OOP的一个基本原则,它隐藏了对象的内部细节,只通过公共接口与外界通信。这为UVM组件提供了模块化和信息隐藏的特性。例如,`uvm_transaction`封装了数据传输的细节,只有通过特定的接口(如`do_copy`、`do_compare`)才能操作这些数据。

抽象允许我们创建一个通用的类来代表一类对象,而不必立即指定具体对象的全部细节。在UVM中,`uvm_sequence_item`就是这样一个抽象类的例子。它定义了所有序列项的基本属性和方法,使得可以创建更具体的数据包类型,同时仍然保持统一的接口。

## 2.2 UVM中的OOP机制

### 2.2.1 UVM中的组件与工厂模式

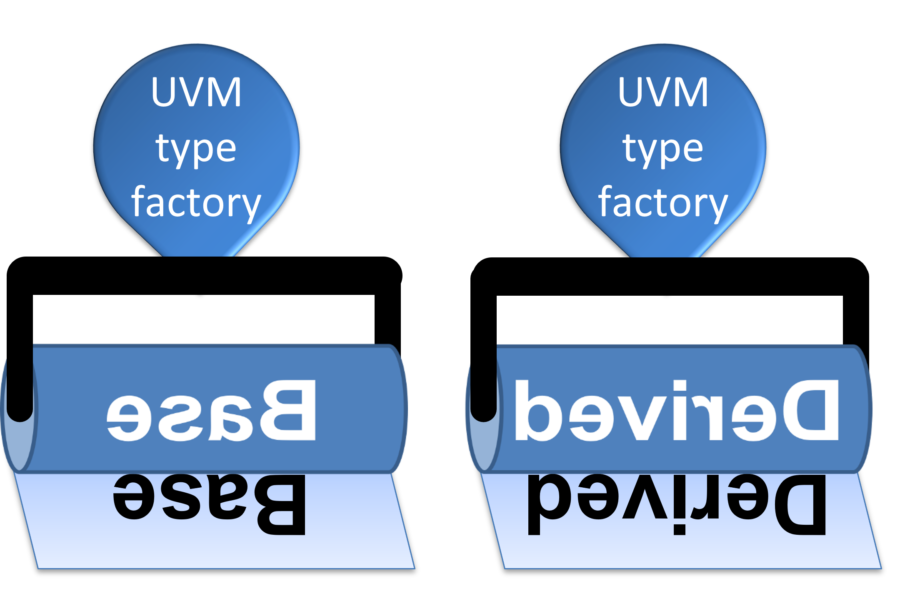

UVM利用组件(Components)来构建复杂的测试平台。在UVM中,组件是通过工厂模式(Factory Pattern)来创建的,这允许在运行时动态创建和配置对象。工厂模式通过一个全局的工厂(`uvm_factory`)来注册类和生成对象实例。

```verilog

class my_uvm_driver extends uvm_driver #(my TRANSACTION);

// ...

endclass

// 在工厂中注册

initial begin

uvm_factory factory = uvm_factory::get();

factory.set_type_override_by_type(uvm_driver::get_type(), my_uvm_driver::get_type());

end

```

这段代码展示了如何在UVM中通过工厂模式注册和创建一个自定义的驱动器类。通过调用`set_type_override_by_type`方法,我们告诉UVM工厂在需要`uvm_driver`实例时,实际上是需要`my_uvm_driver`的实例。

### 2.2.2 UVM中事务和序列的类层次

事务(Transactions)和序列(Sequences)是UVM中用于测试的基本元素。事务是通过接口发送或接收的最小数据单位,而序列是一系列事务的集合。

UVM的事务和序列类继承自`uvm_transaction`,它为所有事务定义了共同的接口和属性。序列则进一步继承自`uvm_sequence`,它提供了生成和启动事务的方法。使用继承机制,UVM允许用户创建更复杂的序列,例如嵌套序列或并行序列,来满足高级测试的需求。

## 2.3 OOP在UVM配置管理中的应用

### 2.3.1 UVM配置数据库的使用

UVM配置数据库(Configuration Database)是管理配置参数的中心化存储。它是通过OOP技术中的单例模式实现的,确保全局只有一个数据库实例。通过配置数据库,可以方便地在UVM测试环境中设置和检索参数。

```verilog

uvm_config_db #(int)::set(this, "my_driver", "num_transactions", 10);

```

以上代码展示了如何使用`uvm_config_db`来为一个名为`my_driver`的对象设置`num_transactions`参数。

### 2.3.2 UVM资源池与共享

UVM资源池提供了一种机制,以管理和共享测试中的资源。资源池可以看作是对象的集合,UVM组件可以从中获取和释放资源。资源池允许组件以一种控制的方式共享资源,这在多驱动器或多监视器环境中尤其有用。

```verilog

class resource_pool extends uvm_resource_pool;

// ...

endclass

uvm_resource_pool::get().set_depth("my_resource", 5);

```

这里,我们创建了一个自定义的资源池,并设置了一个名为`my_resource`的资源,最大深度为5。这样,资源池管理器就可以跟踪和控制对这种资源的访问。

以上内容展示了OOP核心概念在UVM应用基础中的关键作用,以及如何利用这些概念构建健壮的、可扩展的UVM测试环境。在后续章节中,我们将深入探讨UVM的高级编程技巧与实践。

# 3. ```markdown

# 第三章:UVM高级编程技巧与实践

## 3.1 UVM中的寄存器模型

在UVM中,寄存器模型是验证环境中不可或缺的一部分,它用于模拟并测试设计中寄存器的功能和行为。寄存器模型不仅简化了寄存器配置和读写的复杂性,而且能够与事务层和驱动层进行交互,实现自动化测试。

### 3.1.1 寄存器模型的构建与操作

构建UVM寄存器模型首先需要定义寄存器的层次结构和每个寄存器的属性。这可以通过创建UVM的`uvm_reg`类的实例来完成。每个实例代表了一个寄存器,并且可以包含多个字段(`uvm_reg_field`)。通过这种方式,可以描述寄存器的位宽、初始值、访问权限等信息。

下面是一个简单的UVM寄存器模型构建的代码示例:

```verilog

class my_reg_block extends uvm_reg_block;

rand uvm_reg reg_a;

rand uvm_reg reg_b;

function new(string name = "my_reg_block");

super.new(name);

endfunction

virtual function void build();

reg_a = uvm_reg::type_id::create("reg_a", , get_full_name());

reg_a.configure(this, null, "寄存器A");

reg_a.add_field(...);

reg_b = uvm_reg::type_id::create("reg_b", , get_full_name());

reg_b.configure(this, null, "寄存器B");

reg_b.add_field(...);

this.default_map = create_map("default_map", 'h0, 4, UVM_LITTLE_ENDIAN, 1);

this.default_map.add_reg(reg_a, 'h0, "RO");

this.default_map.add_reg(reg_b, 'h4, "RW");

this.lock_model();

endfunction

endclass

```

在此代码中,我们首先创建了一个寄存器块`my_reg_block`,然后在其中定义了两个寄存器`reg_a`和`reg_b`。之后,我们为这些寄存器添加字段,并将它们映射到内存地址上。注意,我们使用了`create_map`来创建一个地址映射表,并且使用`add_reg`方法将寄存器与特定的内存地址关联起来。

### 3.1.2 寄存器与事务的交互机制

寄存器模型与事务层的交互通常通过寄存器模型提供的API来实现。`uvm_reg`类提供了如`read`和`write`等方法,允许测试程序读写寄存器的值。而事务层发送的事务可以通过`uvm_reg_bus_op`结构体表示,以模拟硬件总线上的操作。

```verilog

class reg umi

0

0