【UVM验证环境搭建实战】:一步步教你如何配置

发布时间: 2024-12-26 22:20:45 阅读量: 11 订阅数: 14

# 摘要

UVM(Universal Verification Methodology)是电子系统设计验证领域广泛采用的一种验证方法学。本文首先介绍了UVM验证环境的基础知识和理论框架,包括其基本概念、组成、测试平台架构和配置管理。随后,通过实战搭建部分,详细描述了UVM环境搭建、组件编写集成以及运行调试的过程。文章还探讨了UVM的高级特性,例如覆盖策略、事务级建模(TLM)以及多核并行验证。最后,本文通过案例分析,展示了UVM在实际项目中的应用,分享了验证过程中的教训和最佳实践,以期提高验证效率和覆盖率。整篇论文旨在为读者提供一个全面的UVM验证环境理解和应用指南。

# 关键字

UVM验证环境;理论框架;实战搭建;高级特性;案例分析;验证效率;覆盖率优化

参考资源链接:[UVMHarness:接口连接的便利工具](https://wenku.csdn.net/doc/6412b622be7fbd1778d45a15?spm=1055.2635.3001.10343)

# 1. UVM验证环境基础介绍

## 1.1 UVM的起源和发展

UVM(Universal Verification Methodology,通用验证方法学)是基于IEEE 1800 SystemVerilog语言的验证方法学,它起源于2005年,并在2011年成为IEEE官方推荐的验证标准。UVM集合了多种验证技术的优点,为复杂的系统级芯片设计提供了一套全面、灵活的验证平台。

## 1.2 UVM组件的基本类型和作用

UVM验证环境主要由以下组件构成:

- **uvm_driver**: 负责向DUT(设计组件)发送激励(transactions)。

- **uvm_monitor**: 用于监视DUT的接口信号,并将观察到的信息(transactions)发送到其他UVM组件,如uvm_scoreboard。

- **uvm_agent**: 封装了driver、monitor以及一个或多个_sequences_,它是UVM验证的基本组成单元。

- **uvm_scoreboard**: 用于检查输出数据的正确性,通常通过比较预期结果和实际结果来完成。

- **uvm_env**: 将多个agents、scoreboards和其他环境组件组织起来形成一个完整的验证环境。

- **uvm_test**: 定义测试流程,包括初始化环境、序列生成等,是UVM验证过程中的顶层组件。

通过这些组件的协作,UVM能够提供一个高效且可重用的验证环境,以满足日益增长的硬件设计验证需求。接下来章节将深入探讨UVM验证环境的理论框架,让我们更好地理解其工作原理和组织结构。

# 2. UVM验证环境的理论框架

## 2.1 UVM的基本概念和组成

### 2.1.1 UVM的起源和发展

统一验证方法学(Universal Verification Methodology, UVM)是一种基于SystemVerilog的验证环境框架,旨在提供一个全面、可复用的验证平台以支持复杂的集成电路设计。UVM是IEEE 1800.2-2017标准的一部分,它继承了OVM(Open Verification Methodology)的优点,并且在2010年之后逐渐成为验证领域的主流框架。

UVM的出现,是随着半导体行业对更高效、更可复用的验证方法学的需求而产生的。其前身OVM由Cadence公司推出,随着验证需求的增长,开源验证方法学逐渐得到认可,于是产生了更为完善的UVM。UVM通过IEEE的标准化流程,确保了其在未来技术发展的兼容性和可扩展性。

UVM的发展历程也代表了验证方法学的成熟,它将面向对象编程的优势引入到硬件验证中,极大地提升了验证工作的效率和质量。设计与验证的分离,使得验证工程师可以专注于测试用例的设计,而不用过多关注底层细节。随着UVM的普及和标准化,验证工程师可以借助丰富的社区资源和工具支持,来构建、维护和改进自己的验证环境。

### 2.1.2 UVM组件的基本类型和作用

UVM框架定义了一系列预定义的组件,每个组件都有明确的职责和接口,以便于构建复杂的验证环境。基本组件包括:

- **uvm_driver**:负责与待验证的DUT(Design Under Test)交互,生成激励并驱动其运行。

- **uvm_monitor**:监视DUT的行为,并收集信息,这些信息可以用于生成报告或用于后续的分析。

- **uvm_agent**:封装了driver和monitor,有时还包括一个或多个序列器(sequencer),作为验证环境的基本构建块。

- **uvm_scoreboard**:对比预期结果和DUT输出,验证DUT的功能是否正确。

- **uvm_sequence_item**:定义了事务的基础属性和行为,它是生成激励的基础。

- **uvm_sequence**:用于定义一系列事务的执行顺序,控制事务的生成和执行流程。

- **uvm_env**:将agent、scoreboard等组件组织起来,形成完整的测试环境。

- **uvm_test**:定义测试的高层策略,包括选择和执行不同的sequence,以及配置环境中的组件。

这些组件之间通过标准接口进行通信,确保了验证环境的灵活性和可扩展性。通过组合和配置这些组件,验证工程师可以构建针对特定设计的高效验证环境。随着UVM的发展,其组件也在不断地丰富和完善,以适应日益复杂的验证需求。

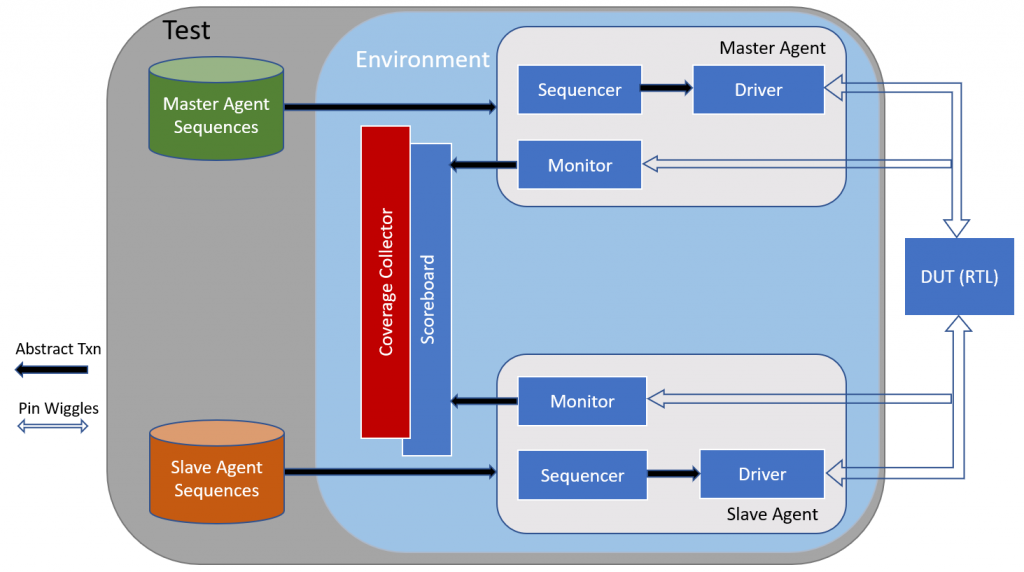

## 2.2 UVM的测试平台架构

### 2.2.1 测试平台的层次结构

UVM测试平台具有清晰的层次结构,它由多个层次构成,每层都有其特定的责任和接口。这种层次化的设计提供了强大的模块化,使得复杂的验证环境可以被灵活地组织和管理。UVM的层次结构通常包括以下几个部分:

- **testbench**:测试平台的最顶层,负责启动和管理测试。

- **uvm_env**:包含所有验证组件,是验证环境的核心。

- **uvm_agent**:每个agent负责与DUT的特定接口进行交互,它封装了driver、monitor和sequencer。

- **uvm_driver**:驱动DUT运行,发送激励到DUT。

- **uvm_monitor**:监测DUT的行为,并将收集到的信息传递给scoreboard或analysis components。

- **uvm_sequencer**:管理事务序列,协调driver和sequence之间的通信。

这种层次化的结构使得验证环境具有高度的可重用性和可维护性,便于进行大规模的验证工作。各层之间的通信通过标准UVM消息和回调机制完成,从而保持了组件间的解耦合性,提高了代码的可维护性和可读性。

### 2.2.2 事务、序列和驱动的角色

在UVM中,事务(transaction)是交互的基本单元,它代表了在DUT和验证环境中传递的数据包或操作。事务在UVM测试平台中扮演着核心角色,以下是与事务相关的关键组件和它们的作用:

- **事务**:定义了数据的传输或操作的细节,例如一个总线事务或一个内存访问请求。

- **序列**:由多个事务组成,定义了事务的生成顺序,可以看作事务的模板或脚本。

- **驱动**:负责执行事务,将事务转化为DUT可以理解的信号或操作。

事务是驱动和sequencer之间的中介。驱动从sequencer接收事务,并将其转换为硬件信号,从而驱动DUT执行相应的操作。而sequencer负责调度序列中的事务,它根据序列生成的指令来组织和发送事务给驱动。

在UVM中,事务的传输通过事务邮箱(transaction mailbox)来实现,这是一个FIFO队列,序列和驱动通过它来交换事务。sequencer将事务放入邮箱,驱动从邮箱中取出事务并执行。

### 2.2.3 Agent、环境和测试的交互

在UVM测试平台中,agent、环境和测试之间通过特定的接口和通信机制进行交互,以实现整个验证流程的协同工作。它们之间的交互关系如下:

- **Agent**:位于环境与DUT之间,是验证环境的一个封装模块。一个agent可以包含一个或多个driver、monitor和sequencer,它们协作执行与DUT的交互操作。

- **Environment**:将多个相关的agent组合在一起,创建一个针对特定DUT的完整验证环境。环境通常包含scoreboard、coverage收集器和其他分析组件,用于分析和评估DUT的行为。

- **Test**:位于环境之上,是验证流程的入口点。它负责创建并配置环境、定义测试的序列,并在测试结束后进行资源清理。

在交互过程中,测试通过调用环境中的组件来初始化验证环境和执行测试流程。测试会实例化一个或多个环境,根据测试策略配置它们,并启动相应的sequence。环境是通过set_config_string、set_config_int等UVM配置机制来配置的。每个agent和其组件(如driver、monitor、sequencer)与环境中的其他组件通信,完成其在验证流程中的职责。

环境会收集来自agent的数据,传递给scoreboard和coverage组件进行分析。scoreboard会比较期望的行为与DUT实际的输出,以确保DUT的功能正确性。coverage组件则收集功能覆盖率数据,提供覆盖分析。

## 2.3 UVM的配置管理

### 2.3.1 配置对象和参数化

UVM的配置对象是管理验证环境参数的强大工具,它允许验证工程师通过配置文件或代码灵活地控制验证环境的行为。UVM配置对象的作用和特点包括:

- **配置对象**:提供了一种结构化和类型安全的方式来参数化验证环境,可以存储和管理验证环境中的配置参数。

- **参数化**:允许在不修改代码的情况下调整验证环境的参数,提高了验证环境的灵活性和可重用性。

在UVM中,配置对象通过一系列的配置宏来实现,这些宏定义了配置参数的属性和约束。使用这些宏,验证工程师可以创建自定义的配置参数,并将它们应用到验证组件中。配置对象通过set和get方法,以及配置宏提供的其他辅助功能,提供了一种方便的途径来访问和修改验证环境的配置。

利用UVM的配置管理,可以轻松地实现参数化测试,例如改变事务大小、频率、功能集,或是改变序列的行为。此外,UVM配置对象支持层次化的配置,能够以一种分级的方式组织配置参数,这为大型验证项目的管理带来了便利。

### 2.3.2 配置的优先级和继承规则

UVM中的配置系统支持多层次、多优先级的配置管理,以确保在存在多个配置源时,可以遵循预设的规则来决定最终的配置值。配置系统中的优先级和继承规则包括:

- **多层次配置**:UVM提供了灵活的多层次配置机制,允许在不同层级定义配置参数,如全局配置、环境配置、agent配置、组件配置等。

- **继承规则**:子层级的配置参数可以继承父层级的参数值,但如果子层级中有同名的参数,则可以覆盖父层级的值。

优先级和继承的规则确保了配置的灵活性和精确性。当一个配置参数在多个层级都有定义时,UVM配置系统会根据优先级规则选择最终使用的配置值。一般情况下,配置系统会从最接近组件的层级开始,向上查找配置值,直到找到一个有效的值。如果组件所在层级没有定义,则会逐级向上查询,直到找到定义了该参数的层级。这个过程遵循的是最近优先原则,即最近的配置参数覆盖最远的配置参数。

继承规则也支持参数的隐藏和修改。一个子层级可以显式地隐藏掉继承自父层级的参数,或者显式地设置一个新的值来覆盖父层级的配置。这样的设计使得配置管理既灵活又可控,能够适应复杂和多变的验证场景。

为了清晰地展示UVM配置的优先级和继承规则,这里提供一个简化的代码示例:

```systemverilog

class env extends uvm_env;

// ...

virtual function void build_phase(uvm_phase phase);

// 配置序列长度

this.uvm_sequence_length = 10;

// ...

endfunction

endclass

class agent extends uvm_agent;

// ...

virtual function void build_phase(uvm_phase phase);

// 隐藏环境中的序列长度设置

this.uvm_sequence_length = null;

// ...

endfunction

endclass

class my_test extends uvm_test;

// ...

virtual function void build_phase(uvm_phase phase);

// 覆盖环境和agent的序列长度设置

uvm_resource_db#(int)::set(this, "uvm_sequence_length", 20, UVM_NONE);

endfunction

endclass

```

在这个例子中,`my_test`中定义的序列长度值将覆盖`env`和`agent`中相应的配置值。此外,`agent`中的代码通过将`uvm_sequence_length`设为`null`,显式地隐藏了来自其父环境`env`的设置,实现了配置的层次控制。

# 3. UVM验证环境实战搭建

## 3.1 UVM环境的搭建准备

在开始搭建UVM验证环境之前,必须确保所有环境依赖软件已经安装并配置正确。这包括但不限于仿真器、UVM库以及项目所需的任何特定工具或插件。本节将详细讨论如何完成环境的准备工作。

### 3.1.1 环境依赖软件的安装和配置

**安装仿真器和UVM库**

```bash

# 示例命令,具体的安装命令会依赖于选定的仿真器和操作系统

sudo apt-get install <simulator-package-name>

git clone https://github.com/UVM-Simulator/UVM-Example.git

```

仿真器是运行UVM测试的底层平台,UVM库提供了UVM的运行时环境。对于安装这两个组件,你需要从仿真器供应商处获取安装包,并通过适当的包管理器安装。对于UVM库,推荐使用官方提供的包或从源代码进行编译安装。

安装完成后,需要对UVM库进行配置,确保仿真器能够在运行时链接到正确的库文件。

**配置环境变量**

```bash

# 设置环境变量,如LD_LIBRARY_PATH(Linux)或PATH(Windows)

export LD_LIBRARY_PATH=/path/to/uvm/lib:$LD_LIBRARY_PATH

```

确保仿真器和UVM库的路径都被添加到环境变量中,以便在命令行中直接访问。

### 3.1.2 项目结构的规划和初始化

**项目结构规划**

合理规划UVM项目的目录结构至关重要,有助于维护和扩展。下面是一个基本的UVM项目目录结构示例:

```

my_project/

|-- src/

| |-- agent/

| |-- env/

| |-- sequences/

| |-- top/

| `-- test/

|-- inc/

|-- scripts/

`-- Makefile

```

- `src/` 包含所有的源代码文件。

- `inc/` 包含所有的头文件和UVM类定义。

- `scripts/` 包含自动化脚本,例如Makefile等。

- `Makefile` 包含构建和运行项目所需的命令。

**项目初始化**

```bash

# 使用git初始化项目版本库

git init

# 创建项目目录结构

mkdir -p src/{agent,env,sequences,top,test} inc scripts

touch scripts/Makefile

```

执行上述命令可以帮助你快速建立项目结构。你可以根据自己的需求来调整这个结构。

## 3.2 UVM组件的编写和集成

在完成项目结构的初始化后,接下来的步骤是编写UVM组件并将其集成到验证环境中。

### 3.2.1 序列和驱动的实现

**序列编写**

```verilog

class my_sequence extends uvm_sequence #(my_transaction);

// 类成员、方法和参数

virtual task body();

// 实现序列的body方法

`uvm_info(get_type_name(), "Executing my_sequence", UVM_LOW)

// 创建和发送事务

endtask

endclass

```

序列类控制事务的生成和发送顺序。在`body()`方法中,你可以编写事务生成逻辑。

**驱动编写**

```verilog

class my_driver extends uvm_driver #(my_transaction);

// 类成员、方法和参数

virtual task run_phase(uvm_phase phase);

// 实现驱动的run_phase逻辑

forever begin

seq_item_port.get_next_item(req);

// 对req进行处理,发送事务到DUT

seq_item_port.item_done();

end

endtask

endclass

```

驱动接收来自序列的事务,并将它们转换为可以在DUT(设计下测试)上执行的信号。

### 3.2.2 代理和监视器的构建

**代理构建**

```verilog

class my_agent extends uvm_agent;

// 类成员、方法和参数

my_driver m_driver;

my_sequencer m_sequencer;

my_monitor m_monitor;

// 构造函数、build_phase等

virtual function void build_phase(uvm_phase phase);

// 实例化驱动、序列器、监视器

endfunction

virtual function void connect_phase(uvm_phase phase);

// 连接驱动和序列器

endfunction

endclass

```

代理封装了驱动、序列器和监视器,负责管理这些组件。`build_phase`中实例化组件,`connect_phase`中进行组件间的连接。

**监视器构建**

```verilog

class my_monitor extends uvm_monitor;

// 类成员、方法和参数

virtual task run_phase(uvm_phase phase);

// 实现监视器的run_phase逻辑

forever begin

// 从DUT捕获信号,转换为事务

end

endtask

endclass

```

监视器负责观察DUT的行为,并将观察到的信号转换为事务对象,供后续分析。

### 3.2.3 环境和测试的组装

**环境组装**

```verilog

class my_env extends uvm_env;

// 类成员、方法和参数

my_agent m_agent;

// 构造函数、build_phase等

virtual function void build_phase(uvm_phase phase);

// 实例化代理和其他组件

endfunction

virtual task run_phase(uvm_phase phase);

// 实现环境的运行逻辑

endtask

endclass

```

验证环境是其他所有组件的容器,它将所有组件连接在一起并控制它们的执行。

**测试编写**

```verilog

class my_test extends uvm_test;

// 类成员、方法和参数

my_env m_env;

my_sequence m_sequence;

// 构造函数、build_phase、main_phase等

virtual function void build_phase(uvm_phase phase);

// 实例化环境

endfunction

virtual task main_phase(uvm_phase phase);

// 测试的主体逻辑

phase.raise_objection(this);

// 启动序列

m_sequence.start(m_env.m_agent.m_sequencer);

phase.drop_objection(this);

endtask

endclass

```

测试类定义了整个测试流程,包括如何配置环境,启动哪些序列等。

## 3.3 UVM的运行和调试

在编写好UVM组件并成功将它们集成后,接下来是运行和调试阶段。这个阶段会执行测试用例并收集验证结果。

### 3.3.1 运行测试用例和查看波形

**运行测试用例**

```bash

# 使用仿真器运行UVM测试

./simulator -uvm -do run.do

```

运行测试用例通常涉及运行仿真器并指定一个包含UVM运行命令的脚本。

**查看波形**

```bash

# 假设仿真器支持波形查看

view_wave

```

在波形查看工具中,可以观察到事务的时序和信号的变化。

### 3.3.2 调试技巧和日志分析

**调试技巧**

调试是发现和修复问题的关键步骤。UVM提供了多种日志级别,如UVM_LOW、UVM_MEDIUM和UVM_HIGH,根据需要调整日志级别可以帮助你专注于特定的信息。

**日志分析**

```verilog

`uvm_info("TAG", "Message", UVM_LOW)

```

日志消息使用`uvm_info`宏定义,其中`TAG`是消息来源的标签,`Message`是实际的信息内容。

### 3.3.3 重用和覆盖率报告

**重用**

```verilog

// 通过重载build_phase方法,实现组件的重用

virtual function void build_phase(uvm_phase phase);

if (!uvm_config_db#(string)::get(this, "", "type", typestr)) begin

`uvm_fatal("UVMConfig", "Type string not found")

end

// 根据typestr决定实例化哪个类型的代理

endfunction

```

通过重用现有代码,可以在不同项目中快速部署UVM环境。

**覆盖率报告**

```verilog

# 启用覆盖率收集

uvm_config_db#(bit)::set(null, "*", "coverage", 1);

# 查看覆盖率报告

report_coverage();

```

覆盖率报告是验证过程中的关键,它表明了哪些功能或代码已经经过测试。UVM提供了内置的覆盖率收集和报告机制。

## 3.4 UVM运行和调试的进阶

UVM验证环境的构建和运行不仅仅是启动一个仿真那么简单。以下是一些进阶的运行和调试技巧,帮助优化验证效率。

### 3.4.1 运行时动态控制

```verilog

// 动态启动和停止序列

phase.raise_objection(this);

// 动态停止序列

phase.drop_objection(this);

```

在运行时,可以通过上下文句柄中的`raise_objection()`和`drop_objection()`方法来控制仿真流程。

### 3.4.2 深入理解UVM配置数据库

UVM配置数据库(`uvm_config_db`)是整个UVM验证环境中的关键组件,它允许从运行时动态设置和获取参数。

```verilog

// 设置参数到UVM数据库

uvm_config_db#(type_id)::set(this, "hierarchy_name", "param_name", param_value);

// 从UVM数据库获取参数

if (!uvm_config_db#(type_id)::get(this, "hierarchy_name", "param_name", local_var))

`uvm_fatal("GETFAIL", "Failed to get param_name from hierarchy_name")

```

通过`uvm_config_db`,验证工程师可以将参数和配置传递给UVM环境中的任意组件,实现高度的灵活性和可配置性。

### 3.4.3 使用UVM报告器

```verilog

// 使用UVM报告器记录事件和错误

uvm_report_info("TAG", "Informational message", UVM_NONE);

uvm_report_warning("TAG", "Warning message", UVM_NONE);

```

UVM报告器是另一种强大的机制,它可以帮助跟踪和记录仿真过程中的各种事件和警告。

### 3.4.4 高级覆盖率收集和分析

```verilog

// 启用交叉覆盖率收集

uvm_config_db#(bit)::set(null, "*", "cross覆盖率", 1);

```

高级覆盖率是复杂设计验证的关键。UVM支持多种类型的覆盖率,包括功能覆盖率、代码覆盖率、状态覆盖率、交叉覆盖率等。

### 3.4.5 验证环境的性能优化

```verilog

// 通过增加UVM组件的并行度来优化性能

uvm_config_db#(bit)::set(null, "*", "parallel", 1);

```

优化UVM验证环境的性能可能包括增加组件的并行度,合理管理事务队列,以及使用更加高效的数据结构。

通过掌握UVM运行和调试的进阶知识,验证工程师可以构建更加健壮和高效的验证环境,从而加速设计的验证周期,提高设计质量。

### 3.4.6 验证环境的文档化

```verilog

// 生成UVM环境的文档

uvm_top.print topology;

```

文档是项目管理和维护的关键。UVM提供了`print topology`等方法,帮助生成环境的文档描述,这对于项目文档化非常有帮助。

上述进阶技巧是构建和维护高效UVM验证环境的重要组成部分。理解和运用好这些技巧,可以显著提升验证效率和设计质量。

# 4. UVM验证环境的高级特性

## 4.1 UVM的覆盖策略

### 4.1.1 代码覆盖率和功能覆盖率

在复杂的设计验证中,仅仅通过运行测试用例并不能保证设计的所有方面都得到了充分验证。这就需要覆盖策略来确保验证的完备性。UVM验证环境中使用的主要覆盖类型包括代码覆盖率和功能覆盖率。

代码覆盖率关注的是源代码的执行情况,它是衡量测试用例质量的一个关键指标。UVM提供了多种代码覆盖率的监测方式,包括行覆盖率(line coverage)、分支覆盖率(branch coverage)、状态机覆盖率(FSM coverage)等。代码覆盖率的主要目的是确保测试用例能够覆盖到设计代码的所有路径,以减少潜在的设计漏洞。

功能覆盖率则是基于设计的规格说明书来定义的,它直接关联到设计的功能点。功能覆盖模型需要设计者根据设计的规格来定义哪些功能是需要被验证的,包括但不限于输入参数的组合、状态机的状态转换等。功能覆盖率通过收集运行期间的功能事件来检查设计是否满足既定的功能需求。

### 4.1.2 覆盖模型的设计和实现

覆盖模型的设计和实现是UVM验证流程中的一个关键步骤。一个有效的覆盖模型可以帮助验证工程师发现测试中可能遗漏的部分。设计覆盖模型时,通常会遵循以下步骤:

1. 定义覆盖点:覆盖点是覆盖模型中的基本元素,它们代表了设计的关键参数或状态。例如,一个设计的接口可能会有一个读/写信号,这就可以被定义为两个覆盖点。

2. 组合覆盖点:通过组合不同的覆盖点来创建覆盖组,覆盖组可以更好地描述设计的复杂行为。比如,一个写操作是否成功可能依赖于多个覆盖点的组合。

3. 覆盖模型的实现:在UVM中,可以使用`covergroup`类来创建和管理覆盖点和覆盖组。覆盖模型通常在UVM组件的`build_phase`方法中定义,以确保在组件的生命周期中尽早被实例化。

4. 收集和分析覆盖数据:在测试执行过程中,UVM运行时会自动收集覆盖数据。完成后,验证工程师可以使用UVM提供的工具或第三方工具来分析覆盖数据,确定测试是否达到覆盖目标。

实现覆盖模型的代码示例如下:

```verilog

class my_covergroup extends uvm_covergroup;

coverpoint my_signal_a;

coverpoint my_signal_b {

bins low = {0};

bins high = {1};

}

coverpoint my_signal_c;

cross my_signal_a, my_signal_b, my_signal_c;

endclass

```

在这个例子中,我们定义了一个`my_covergroup`,它有三个信号的覆盖点,以及一个覆盖组。这允许我们检查不同信号值的组合。

覆盖策略的实施能够显著提升验证的效率和可靠性。通过量化和监控验证过程,工程师可以更有针对性地进行测试用例的设计,以确保设计的每个方面都被充分地测试过。

## 4.2 UVM的事务级建模(TLM)

### 4.2.1 TLM的基本概念

事务级建模(TLM)是UVM验证环境的核心组成部分,它允许设计和验证工程师以事务的方式来交流信息,而不需要对事务的详细实现有深入的了解。这种抽象化大大提高了验证效率,因为它使得组件之间可以不必依赖于信号级或时序级的细节。

TLM的基本思想是,通过定义一系列标准接口和组件通信协议,允许不同的验证组件之间交换信息。这些信息通常是高层次的事务描述,如内存读写请求、数据包等。

在UVM中,TLM通信是通过端口(port)、导出(export)、导出实现(imp)和邮箱(TLM FIFOs)来实现的。TLM通信在性能优化和并行验证方面提供了巨大优势。

### 4.2.2 TLM端口和接口的应用

TLM端口是UVM组件用来请求服务的接口。每个端口都有一个或多个导出,而导出则是连接到其他组件的接口,其他组件实现了这些接口来响应端口的请求。这种分离的接口和实现机制为组件之间的松耦合通信提供了便利。

例如,在一个处理器模型和内存模型之间的通信中,处理器模型会通过TLM写端口(`write_port`)发起内存写事务请求,而内存模型会有一个相应的导出(`write_export`)来响应这些请求。

```verilog

class processor extends uvm_component;

uvm_write_port#(mem_transaction) write_port;

// ...

function void build_phase(uvm_phase phase);

write_port = new("write_port", this);

endfunction

endclass

class memory extends uvm_component;

uvm_write_imp#(mem_transaction) write_imp;

// ...

function void build_phase(uvm_phase phase);

write_imp = new("write_imp", this);

endfunction

virtual function void write(mem_transaction tr);

// Handle the write transaction

endfunction

endclass

```

在这个例子中,`processor`组件创建了一个写端口来发出事务请求,而`memory`组件实现了一个写导出来响应这些请求。

### 4.2.3 TLM事务在UVM环境中的传递

TLM事务的传递是通过TLM端口和导出之间的通信完成的。事务通过端口发出后,会由连接到相应端口的导出来接收。这种传递可以是同步的也可以是异步的。

在同步传递中,事务被发送后,发送方会等待直到接收方处理完事务。在异步传递中,发送方可以继续执行其他任务,而不需要等待接收方的处理结果。

UVM提供了一系列的宏来简化TLM事务的传递,例如`uvm_send`宏可以用来发送事务到同步或异步的导出。

TLM事务的传递流程图如下:

```mermaid

graph LR

A[Processor Write Port] -->|sends transaction| B[Memory Write Export]

B -->|receives transaction| C[Memory Handle Transaction]

```

TLM的使用不仅简化了通信,还提供了更好的可重用性和模块化,这对于大型设计的验证尤其重要。通过使用TLM,验证工程师可以构建一个更加灵活和可维护的验证环境。

## 4.3 UVM的多核并行验证

### 4.3.1 并行验证的必要性和优势

随着集成电路设计复杂性的增加,传统的串行验证方法已经无法满足按时交付高质量验证结果的需求。并行验证技术应运而生,它允许同时运行多个测试,以提高验证效率。

在UVM中实现并行验证有其必要性和明显的优势:

1. 提高吞吐量:并行验证通过同时运行多个测试用例,显著增加了单位时间内可以执行的测试用例数量。

2. 早期发现错误:并行测试可以同时触发多个不同的故障模式,有助于在设计早期发现和定位问题。

3. 提高资源利用率:并行验证可以更好地利用现有的计算资源,提高硬件利用率。

4. 加快验证收敛速度:通过并行运行多个测试用例,可以更快地实现验证的全面覆盖。

并行验证的实现一般涉及到测试用例的选择、调度策略、资源分配和结果收集等几个方面。在UVM中,可以利用UVM的资源池(resource pool)和事件(events)来管理并行测试的执行。

### 4.3.2 并行测试的调度和执行

并行测试的调度是指根据一定的规则和策略来决定哪些测试用例在何时执行。UVM提供了一些内置机制来支持并行测试,例如使用`uvm_test_done`事件来同步多个测试用例的结束。

在并行测试执行中,可能需要考虑以下因素:

- 测试用例的依赖关系:一些测试用例可能需要在其他测试用例完成后才能执行。

- 测试用例的运行时间:优先运行预计耗时较长的测试用例,以提高资源利用率。

- 测试用例的覆盖范围:尽量避免重复覆盖相同的设计部分,以实现有效的验证。

并行测试的执行通常涉及到创建多个UVM测试对象,并通过UVM的运行机制来调度它们的执行。

### 4.3.3 并行测试的结果合并和分析

在并行测试中,每个测试用例会产生自己的结果,包括日志文件、波形和覆盖率数据等。为了评估整个验证过程的成功与否,需要合并这些结果并进行分析。

结果合并通常涉及到日志文件的整合、波形文件的同步、覆盖率数据的汇总等。UVM提供了相应的工具和方法来处理这些任务,如`uvm_top`的`report_phase`可以用来收集各个测试用例的日志信息。

合并后的结果可以用来进行更全面的分析,以确保验证没有遗漏任何重要部分,并且能够确定验证的完成度。

```mermaid

graph LR

A[Start Parallel Testing] --> B[Schedule Test Cases]

B --> C[Execute Tests]

C --> D[Merge Results]

D --> E[Analyze Coverage and Logs]

E --> F[Final Verification Report]

```

并行验证策略的实施需要细致的计划和管理,以确保测试的正确性和效率。但是,它的优势使得并行验证成为大型设计验证项目的首选方法。通过并行验证,验证工程师可以更快地发现和修复错误,缩短验证周期,从而推动整个项目向前发展。

# 5. UVM验证环境的案例分析

## 5.1 具体项目的UVM验证环境搭建

### 5.1.1 项目背景和验证目标

在进行UVM验证环境搭建之前,了解项目背景和明确验证目标是至关重要的一步。假设我们正在进行一个基于ARM架构的处理器开发项目,其目标是确保处理器的各种操作模式和功能都能正确地在UVM环境中进行验证。具体的验证目标包括:

- 核心功能的正确性,如算术运算、逻辑运算和控制流。

- 不同模式下的行为,例如用户模式、系统模式等。

- 性能指标,如最大工作频率和处理速度。

- 与外设接口的互操作性验证。

### 5.1.2 验证环境设计和实现

为了验证上述目标,我们需要设计一个能够模拟所有外部操作的UVM验证环境。以下是环境设计和实现的关键步骤:

- **环境组件的划分**:根据处理器的不同功能模块划分UVM Agent,如运算单元Agent、控制单元Agent、接口Agent等。

- **序列和事务的定义**:创建可以覆盖所有验证场景的序列,定义事务以模拟处理器的输入输出。

- **驱动和监视器的编写**:实现能够发送事务到DUT和监视事务响应的驱动和监视器。

- **检查器的集成**:设计检查器来验证DUT输出和预期结果之间的匹配。

- **配置管理**:使用UVM的配置机制来灵活地对测试环境进行参数化,以适应不同的验证场景。

## 5.2 验证案例的运行和优化

### 5.2.1 案例的运行过程和问题定位

一旦环境搭建完成,接下来就是运行验证案例。这个过程可能包括:

- **启动UVM仿真**:通过指定的命令和参数来启动仿真。

- **波形和日志分析**:查看波形图和日志信息来定位问题。

- **覆盖率收集**:利用代码和功能覆盖率工具来评估验证的全面性。

问题定位是验证过程中的关键一环,可能涉及到的步骤包括:

- **错误追踪**:在日志或波形中找到异常行为。

- **回溯测试**:尝试不同的测试案例来重现问题。

- **调试和修复**:一旦问题定位到具体的测试案例,就可以开始修复并进行回归测试。

### 5.2.2 验证效率和覆盖率的优化

随着测试案例数量的增加,确保高效率和高覆盖率是非常重要的。可以采取以下措施:

- **自动化测试**:实现自动化测试流程,包括测试案例生成、执行和结果收集。

- **优先级划分**:根据功能复杂性和风险等级,对测试案例进行优先级排序。

- **回归策略优化**:基于覆盖率和错误发现率来优化回归测试集。

- **重用性增强**:通过组件重用和参数化来减少重复工作。

## 5.3 项目中的教训和最佳实践

### 5.3.1 常见问题总结和解决方案

在实际项目中,可能会遇到各种挑战,包括但不限于:

- **环境搭建问题**:环境依赖冲突、组件兼容性问题。

- **性能瓶颈**:仿真运行缓慢,特别是在大数据量或复杂算法上。

- **覆盖率不达标**:关键功能点未能被有效测试。

对于这些问题,解决方案可能包括:

- **环境配置标准化**:确保所有开发人员和测试人员遵循统一的环境配置步骤。

- **性能分析工具应用**:使用专业的分析工具对仿真性能进行优化。

- **覆盖率驱动开发**:持续增加测试案例,直到覆盖率达到预定目标。

### 5.3.2 验证流程的改进和最佳实践分享

在项目完成后,总结和分享最佳实践可以帮助团队提升效率和质量。最佳实践可能包括:

- **预研和计划**:在项目开始之前进行充分的预研和计划。

- **代码审查和复审**:定期的代码审查可以有效提升代码质量。

- **持续集成和持续部署**:实现CI/CD流程,确保代码的持续集成和更新。

通过分享这些实践,团队可以避免未来的错误,同时提升整个组织的验证能力。

0

0