【UVM与SystemVerilog协同】:双剑合璧,提升验证效率的终极秘诀

发布时间: 2024-12-26 23:07:12 阅读量: 8 订阅数: 14

# 摘要

本文旨在详细探讨UVM与SystemVerilog的协同工作原理及应用。首先介绍了UVM基础理论与实践,包括其架构、组件、通信机制以及测试环境搭建的方法。接着,深入分析了SystemVerilog的面向对象特性、随机化与约束技术,以及断言和覆盖率的使用,这些在UVM中发挥着重要作用。文章进一步阐述了UVM事务级建模、混合仿真技术和报告机制等高级协同技术。最后,针对UVM与SystemVerilog协同的性能优化问题,提出了性能分析、代码优化技术以及自动化测试流程的设计策略。通过案例分析与实践,本文为验证工程师提供了一套全面的解决方案,以提高复杂系统设计的验证效率和效果。

# 关键字

UVM;SystemVerilog;面向对象特性;随机化与约束;事务级建模;性能优化

参考资源链接:[UVMHarness:接口连接的便利工具](https://wenku.csdn.net/doc/6412b622be7fbd1778d45a15?spm=1055.2635.3001.10343)

# 1. UVM与SystemVerilog协同概述

## 1.1 协同的重要性

在现代集成电路设计验证领域中,UVM(Universal Verification Methodology)和SystemVerilog已经成为了行业标准。SystemVerilog不仅增强了硬件描述语言的能力,更是在UVM中起到了核心作用,为复杂的验证需求提供了强大的支持。两者的结合,为验证工程师提供了一个高效且灵活的验证环境,能够快速搭建和迭代复杂的测试场景。

## 1.2 UVM与SystemVerilog的基本联系

SystemVerilog为UVM提供了语言层面的支持,特别是在类的定义、随机化和断言等方面。通过利用SystemVerilog的强大功能,UVM可以实现更加模块化、可重用的验证环境。协同工作不仅仅体现在语法上的互补,更在于其深层次的验证方法学的结合,使得验证过程更加规范和高效。

## 1.3 协同应用的场景和价值

在复杂芯片的验证中,UVM与SystemVerilog协同工作能大幅提升验证工作的覆盖率和质量,缩短产品的上市时间。例如,在进行事务级建模(TLM)时,使用SystemVerilog的面向对象特性可以更有效地构建和管理测试环境,而在编写激励和驱动时,SystemVerilog的随机化功能则可以快速生成大量有代表性的测试数据。这种协同工作不仅提升了验证工作的效率,也增强了验证的深度和广度。

# 2. ```

# 第二章:UVM基础理论与实践

## 2.1 UVM的基本概念和组成

### 2.1.1 UVM的架构和组件

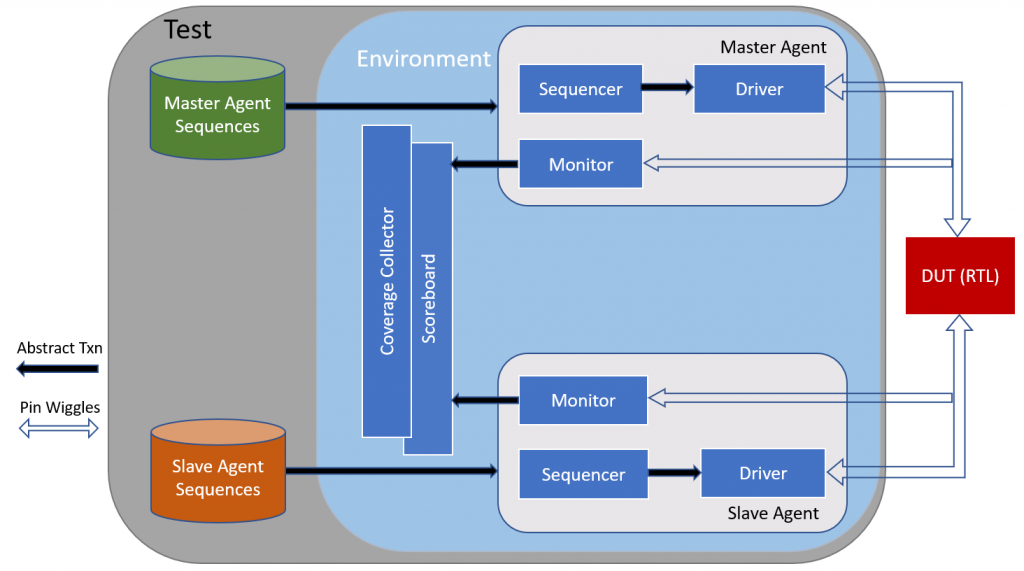

UVM(Universal Verification Methodology)是一种基于SystemVerilog的验证方法学,它为设计验证提供了一套完整的架构和组件。UVM核心是一个类库,利用面向对象编程的特性,为用户提供了丰富的接口和抽象基类。UVM的架构基于TLM(Transaction Level Modeling)的概念,支持多种层次的验证,从底层的门级仿真到高层次的事务级建模。

UVM的架构由以下主要组件构成:

- **uvm_root**:UVM测试的顶层对象,用于初始化UVM环境,例如启动仿真、注册所有组件,并且负责整个仿真流程的生命周期。

- **uvm_scoreboard**:负责比对输入和输出事务,保证DUT(Design Under Test)的功能正确性。

- **uvm_driver**:负责将序列(sequence)中的事务驱动到DUT中。

- **uvm_monitor**:监视DUT的行为,收集信息,并将观察到的事务转发到其他组件,如uvm_scoreboard。

- **uvm_agent**:封装了驱动、监视器和序列器,为复用提供了方便。

- **uvm_env**:可以包含多个agent和scoreboard,模拟整个验证环境。

### 2.1.2 UVM中的通信机制

UVM的通信机制主要依赖于TLM组件之间的数据交换。它使用事务(transaction)作为数据交换的基本单元。事务可以是简单的信号变化,也可以是复杂的总线交易数据。事务经过驱动(driver)传递到DUT,监视器(monitor)观察DUT的行为,并将事务报告给scoreboard或其他分析器。

事务在UVM中通过以下方式在不同的TLM组件间传递:

- **序列(sequence)**:定义了一系列事务,驱动器根据序列来驱动DUT。

- **通信通道(port, export, imp)**:用于UVM组件之间的连接,以传递事务。

- **阻塞和非阻塞传输(put, get)**:使用`uvm_transaction`派生类的实例进行通信。

这些机制通过以下UVM标准组件实现:

- **uvm_sequencer**:存储并管理事务序列。

- **uvm_sequence_item**:代表单个事务的基本类型。

- **uvm_sequence**:可以产生事务序列,配合sequencer使用。

## 2.2 UVM测试环境的搭建

### 2.2.1 测试平台的构建步骤

搭建一个UVM测试环境通常需要以下步骤:

1. **定义DUT接口**:首先需要定义与DUT交互的接口类,确保测试环境能够与DUT通信。

2. **创建驱动和监视器**:设计对应的uvm_driver和uvm_monitor,监视器负责捕获DUT的输出,驱动则负责向DUT发送数据。

3. **构建序列**:创建相应的uvm_sequence,可以是基本的事务序列,也可以是复杂场景的序列。

4. **集成到agent**:将驱动、监视器和序列器封装到uvm_agent中,以便于复用和管理。

5. **环境封装**:将一个或多个agent和scoreboard组合到uvm_env中,形成完整的验证环境。

6. **运行测试**:利用uvm_test基类编写测试用例,并在其中启动序列,开始验证。

### 2.2.2 测试用例和序列的开发

测试用例是UVM验证过程中的核心,它负责调用序列来驱动DUT,并通过scoreboard来验证DUT的行为。以下是一个简单的测试用例开发流程:

1. **继承uvm_test类**:创建一个新的类,继承自`uvm_test`,这个类将会用来编写和执行测试。

2. **创建序列实例**:创建一个或多个序列实例,并将它们与sequencer连接。

3. **编写测试序列**:在序列类中重载`body`方法,编写具体的事务序列。

4. **配置环境**:使用uvm_config_db来配置所有的组件,确保它们被正确初始化。

5. **启动测试序列**:在测试用例的`main_phase`或`run_phase`方法中启动序列。

6. **结果验证**:通过scoreboard对DUT的响应事务进行验证,并产生报告。

## 2.3 UVM中的预测器和评分器

### 2.3.1 预测器的作用与实现

在UVM环境中,预测器(predictor)用于预测DUT的期望行为,它通常与监视器(monitor)协同工作。监视器捕获DUT的实时行为,而预测器则根据输入数据和已知的设计规则预测DUT应该产生的输出。

预测器的实现通常涉及以下步骤:

1. **继承uvm_component**:创建一个新的类,继承自`uvm_component`。

2. **定义预测逻辑**:在该类中定义预测逻辑,通常包括输入事务的处理和输出事务的预测。

3. **连接监视器**:与监视器组件建立连接,通过TLM端口接收监视器捕获的事务。

4. **产生预测事务**:基于预测逻辑,产生与实际DUT输出匹配的预测事务。

5. **与scoreboard交互**:将预测事务传递给scoreboard,进行结果对比。

### 2.3.2 评分器的作用与实现

评分器(scorer)在UVM中与预测器协同工作,用来比对监视器收集的事务和预测器生成的预测事务。它的作用是确保DUT的输出与预期的行为一致。

实现一个评分器通常包括:

1. **继承uvm_component**:创建一个新的评分器类,继承自`uvm_component`。

2. **连接监视器和预测器**:评分器需要连接到监视器和预测器,以接收它们产生的事务。

3. **实施比对逻辑**:在评分器类中实现事务比对的逻辑。

4. **报告不匹配事务**:如果发现不匹配的事务,评分器需要记录错误,并给出详细信息。

为了实现高效准确的比对,评分器可能需要使用到UVM提供的各种断言和比较机制。

```

```mermaid

flowchart LR

subgraph uvm_component ["uvm_component"]

direction LR

uvm_driver["uvm_driver"]

uvm_

```

0

0