【计算机组成原理基础】:掌握核心概念,从术语解析到性能提升

发布时间: 2024-11-15 03:37:54 阅读量: 54 订阅数: 50

Java-美妆神域_3rm1m18i_221-wx.zip

# 1. 计算机组成原理概述

计算机科学与技术的领域中,了解计算机的组成原理是至关重要的。计算机组成原理涉及到多个核心组件,如中央处理单元(CPU)、存储系统、输入/输出系统等。这些组件协同工作,构成了复杂而功能强大的计算机体系结构。在本章中,我们将从宏观角度介绍这些组成部分的基本功能和它们在计算机系统中的重要性。

计算机系统是一个高度集成的系统,它的运作依赖于组件间的精确协调。这些组件不仅包括硬件,如处理器、内存和存储设备,还包括软件,如操作系统和应用程序。为了充分理解这些组件如何协同工作,我们将首先探讨它们的基本组成原理。这将为后续章节中对各个组件深入分析和优化奠定坚实的基础。

## 理解计算机的基本构成

计算机系统是由多个相互连接的部分构成的。理解这些部分如何协同工作是理解计算机组成原理的基础。这些部分主要包括:

- **中央处理单元(CPU)**:执行程序指令的处理器,计算机的“大脑”。

- **存储系统**:包括随机存取存储器(RAM)和非易失性存储器,如硬盘和固态驱动器(SSD),用于数据和指令的存储。

- **输入/输出系统**:提供计算机与外部设备(如键盘、鼠标、显示器)的数据交互接口。

以上只是对计算机组成原理的简单概述。后续章节将会详细探讨这些组件的工作原理及其对计算机性能的影响。

# 2. 核心组件的功能与工作原理

### 2.1 中央处理单元(CPU)

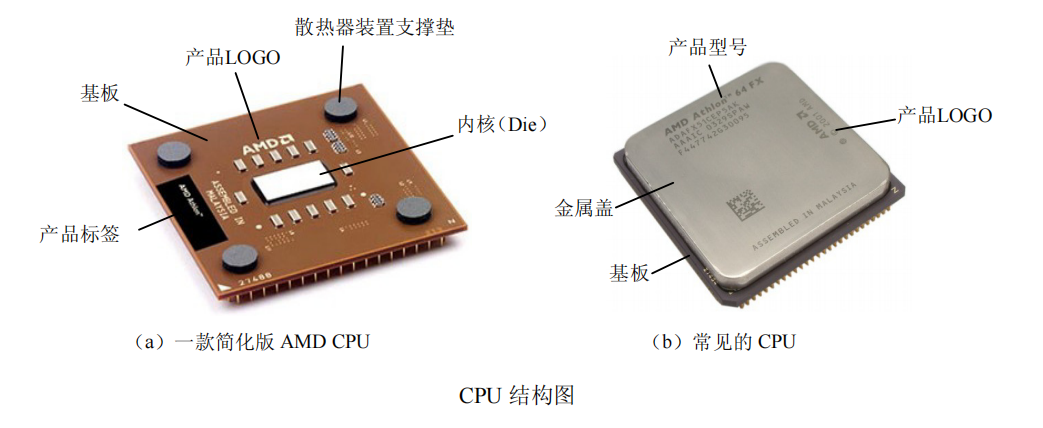

#### 2.1.1 CPU的结构与功能

在现代计算机系统中,中央处理单元(CPU)是执行计算和处理任务的核心部件。它由算术逻辑单元(ALU)、控制单元(CU)和寄存器组构成,负责解释和执行指令、处理数据和协调计算机各个组件之间的信息流动。

- 算术逻辑单元(ALU):主要负责执行算术和逻辑运算。例如,执行加法、减法运算,以及执行逻辑运算如与、或、非等。

- 控制单元(CU):从内存中取出指令,解释指令,并指挥系统其他部分执行指令中的操作。

- 寄存器组:用于存储临时数据,包括通用寄存器、指针寄存器和累加器等。它们的访问速度非常快,用于存储和处理指令执行过程中产生的中间数据。

CPU的时钟频率是衡量其处理能力的关键指标,高频率意味着每秒能执行更多指令。现代CPU通常采用流水线技术来提高效率,即同时处理多条指令的不同部分。

```mermaid

graph TB

A[指令获取] --> B[指令解码]

B --> C[执行指令]

C --> D[访问内存]

D --> E[写回结果]

```

#### 2.1.2 指令集架构和微架构

指令集架构定义了CPU可识别和执行的指令集合,以及这些指令如何编码和存储。常见的指令集架构包括x86、ARM、MIPS等,每种指令集都有其特定的指令格式、寻址模式和操作类型。

微架构则涉及到CPU的物理设计和实现,它描述了CPU内部的工作原理和组件之间的连接方式。微架构的设计对CPU的性能有着直接影响。例如,现代CPU使用了多级流水线、超标量执行单元、分支预测机制等高级微架构技术来提升性能。

```mermaid

classDiagram

class InstructionSet {

+Format format

+AddressingMode addressingMode

+Operation operation

}

class Microarchitecture {

+Pipeline pipeline

+SuperscalarExecutionUnit executionUnit

+BranchPrediction mechanism

}

InstructionSet <|-- x86

InstructionSet <|-- ARM

Microarchitecture <|-- Core_i7

Microarchitecture <|-- Snapdragon

```

### 2.2 存储系统

#### 2.2.1 主存和高速缓存的工作原理

主存(RAM)是计算机用于存储正在运行的程序和数据的部件。高速缓存(Cache)是比主存更快的存储层次,用于减少CPU访问主存的延迟。

- 主存:提供足够的存储空间来保持操作系统、应用程序以及数据。现代计算机通常使用动态随机存取存储器(DRAM)。

- 高速缓存:分为多级,如L1、L2和L3。L1缓存速度最快但容量最小,L3缓存速度较慢但容量更大。高速缓存使用局部性原理来预测CPU接下来需要哪些数据,并将这些数据提前加载到缓存中。

```markdown

| 缓存级别 | 大小 | 速度 | 位置 |

|---------|------------|------|------------------|

| L1 | 64 - 256 KB | 最快 | CPU核心内部 |

| L2 | 256 KB - 4 MB | 较慢 | CPU核心内部或共享 |

| L3 | 4 MB - 32 MB | 更慢 | CPU内部共享 |

```

#### 2.2.2 存储层次和虚拟内存管理

计算机存储层次结构包括了从快速的CPU寄存器、到高速缓存、主存,再到慢速但大容量的硬盘和外部存储。每一层存储都基于成本和性能的权衡设计,用于优化系统性能。

- 虚拟内存管理:操作系统通过虚拟内存管理,允许程序使用的内存地址是虚拟的,这些地址被转换为实际的物理内存地址。当物理内存不足时,操作系统将一部分内容交换(swap)到硬盘上,形成虚拟内存。

### 2.3 输入/输出系统

#### 2.3.1 I/O接口和设备

I/O接口是计算机与外部设备(如键盘、显示器、网络接口)之间的连接点。它负责管理数据的输入和输出过程,包括数据格式的转换、速率的匹配和错误的检查。

- 串行接口:如USB(通用串行总线)、串行端口,以串行方式传输数据。

- 并行接口:如IEEE 1284,并行方式传输数据,现已较少使用。

- 网络接口:如以太网接口,提供计算机之间的网络通信功能。

```markdown

| I/O接口 | 速度 | 用途 | 特点 |

|---------|--------|------------------|-------------------------------|

| USB 3.0 | 5 Gbps | 外部设备连接 | 快速传输,即插即用 |

| SATA | 6 Gbps | 硬盘驱动器连接 | 大容量存储设备连接 |

| PCIe 3.0| 8 GT/s | 显卡、网络卡连接 | 高速总线,扩展槽连接主要部件 |

```

#### 2.3.2 总线技术和数据传输

总线是计算机内部连接各个组件的电子信号传输路径,包括数据总线、地址总线和控制总线。总线技术对数据传输效率和计算机性能有显著影响。

- 数据总线宽度:决定了CPU一次能处理多少位数据。

- 地址总线宽度:决定了CPU能直接访问的最大内存空间。

- 控制总线:用于控制数据传输的方向和时序。

在设计高性能计算机时,优化总线技术和采用高速数据传输协议(如PCI Express)是非常重要的。

```mermaid

graph LR

A[CPU] -->|数据总线| B[北桥芯片]

B -->|数据总线| C[主存]

B -->|控制总线| D[南桥芯片]

D -->|PCIe| E[显卡]

D -->|USB| F[外部设备]

```

通过本章节的介绍,您应该对CPU、存储系统和输入/输出系统的核心组件有了深入的理解。下一章节,我们将深入探讨指令集和汇编语言的基础知识,以及它们在计算机程序设计中的应用。

# 3. 指令集和汇编语言

## 3.1 指令集架构基础

### 3.1.1 指令格式和寻址模式

在计算机系统中,指令集架构(Instruction Set Architecture, ISA)是硬件和软件之间沟通的桥梁,定义了计算机处理器能够识别和执行的机器指令集。指令格式是这种机器指令的编码方式,通常包含操作码(opcode)和一个或多个操作数。操作码指定要执行的操作类型,比如加法、减法等,而操作数指明数据来源和去向。

寻址模式则是指定如何寻找或计算操作数地址的方式。不同的寻址模式允许不同的灵活性和复杂度。常见的寻址模式包括立即寻址(其中操作数直接包含在指令中)、直接寻址、间接寻址、寄存器寻址、基址寻址、变址寻址等。每种模式在处理数据访问、参数传递和程序的内存管理方面都有其特定的应用场景和优势。

```assembly

; 示例:x86架构的汇编指令使用不同寻址模式

; 立即寻址模式: MOV AX, 0x1234 ; 将立即数0x1234移动到寄存器AX中

; 寄存器寻址模式: MOV AX, BX ; 将寄存器BX的值移动到寄存器AX中

; 直接寻址模式: MOV AX, [0x4000] ; 将内存地址0x4000处的数据移动到AX中

; 基址寻址模式: MOV AX, [BX+0x10] ; 将基于寄存器BX和偏移量0x10的内存地址处的数据移动到AX中

```

### 3.1.2 指令类型和操作

指令类型通常可以根据它们的功能进行分类。基本指令涉及数据的加载和存储、算术和逻辑运算以及控制流的变化。算术指令执行加、减、乘、除等基本数学运算,逻辑指令处理布尔运算(比如AND、OR、NOT),控制流指令则改变程序执行的顺序,包括条件分支和循环控制。

操作数可以是整数、浮点数、字符或字符串,也可以是高级数据结构,如数组或结构体。根据操作数的不同,指令可以分为多种类型,如数据传输指令(如MOV、PUSH、POP)、算术逻辑指令(如ADD、SUB、MUL、DIV)、控制转移指令(如JMP、CALL、RET)等。

```assembly

; 示例:不同类型的x86指令

; 数据传输指令: MOV AX, BX ; 将BX寄存器的值传送到AX寄存器中

; 算术指令: ADD AX, BX ; 将AX寄存器的值与BX寄存器的值相加,并将结果存回AX寄存器

; 控制转移指令: JMP 0x100 ; 无条件跳转到内存地址0x100处执行指令

```

## 3.2 汇编语言编程

### 3.2.1 汇编语言的基本结构

汇编语言是一种低级语言,与机器代码一一对应,但采用人类可读的符号表示。每条汇编指令通常对应于一条机器指令。汇编语言的基本结构包括指令、标签、操作数和注释。

- 指令是执行特定操作的代码。

- 标签是用于标识指令或数据的名称,在跳转和数据定义中使用。

- 操作数是指令中使用的数据或寄存器。

- 注释是对代码进行解释的文本,通常以分号(;)或感叹号(!)开头。

```assembly

; 示例:简单的汇编代码结构

section .text

global _start

_start: ; 程序入口标签

mov eax, 1 ; 系统调用号,1代表exit系统调用

mov ebx, 0 ; 退出状态码

int 0x80 ; 触发中断,执行系统调用

section .data

msg db 'Hello, World!', 0xA ; 定义字符串数据和换行符

```

### 3.2.2 实用汇编语言编程技巧

在进行汇编语言编程时,有许多技巧可以帮助编写更高效和可维护的代码。首先,熟悉指令集架构对于编写高性能的汇编程序至关重要。了解各种指令的执行时间和资源消耗可以优化代码的性能。

其次,合理的使用寄存器可以减少对内存的访问次数,从而提高执行速度。将频繁使用的变量存储在寄存器中是常见的优化手段。

此外,结构化的代码设计可以帮助维护代码的清晰度和可读性。这包括使用宏、函数和模块化设计,以及编写清晰的注释和文档。

```assembly

; 示例:使用寄存器优化性能

; 假设我们要频繁使用变量sum

section .text

global _start

_start:

xor eax, eax ; 清零EAX寄存器,用于存储sum

mov ecx, 10 ; 设置计数器ECX为10

loop_start:

add eax, ecx ; 将计数器值加到EAX寄存器

dec ecx ; 计数器减1

jnz loop_start ; 如果ECX不为零,跳转回loop_start

; 此时EAX寄存器中存储的就是累加的结果sum

```

## 3.3 指令集与性能

### 3.3.1 指令流水线和超标量处理

指令流水线技术是现代处理器提升吞吐量和性能的关键技术之一。它允许在单一处理器内并行执行多条指令的不同阶段,从而减少每个指令完成所需的总时间。超标量处理器可以同时发出多条指令,这进一步增加了指令处理的并行度。

流水线的每个阶段都执行不同的任务,例如取指、译码、执行、访问内存和写回。这种分解任务的方法确保了处理器在等待某些操作完成时,可以进行其他指令的处理。

超标量处理架构通常配备多个功能单元,这些单元能够独立并行地处理不同的指令流。高级流水线和超标量技术相结合,能够在每个时钟周期内发射多条指令,显著提升处理器的处理能力。

```assembly

; 无法提供代码示例,因为流水线和超标量处理属于硬件层面的技术细节,不直接体现在汇编代码中。

```

### 3.3.2 并行计算和指令级并行

并行计算是指同时使用多个计算资源来解决计算问题的过程,其目的是加速计算速度和提高资源利用率。指令级并行(Instruction-Level Parallelism, ILP)是并行计算的一种形式,它涉及在一个时钟周期内执行多个操作或指令。

为了实现ILP,处理器必须能够同时检测和发射多个独立指令。这需要复杂的硬件支持,例如指令重排缓存(Reorder Buffer)、预测执行机制和寄存器重命名等技术。

超标量处理器和超线程(Hyper-Threading)技术都是实现指令级并行的手段。超线程技术通过在单个物理处理器内模拟两个(或更多)逻辑处理器,使得每个时钟周期内能够更加高效地利用处理器资源。

```assembly

; 无法提供代码示例,因为指令级并行的实现主要依赖于底层硬件设计,不直接体现在汇编代码中。

```

在下一章节中,我们将探讨计算机体系结构的性能优化,进一步分析如何通过改进硬件设计和软件编写提升系统性能。

# 4. 计算机体系结构的性能优化

## 4.1 性能评测指标

在现代计算机体系结构中,性能评测是一个多维度的过程,涉及对不同硬件组件和软件配置的综合考量。评测指标是衡量计算机性能的量化标准,它们提供了一个可以客观比较不同系统性能的基准。

### 4.1.1 CPU性能评测标准

CPU性能是计算机性能的最重要的指标之一,其性能评测标准通常包括以下几个关键方面:

- **时钟频率(Clock Speed)**:CPU的运行速度,以GHz为单位。它决定了CPU每秒钟可以执行多少个周期。

- **IPC(Instructions Per Cycle)**:每个时钟周期内可执行的指令数量。IPC高意味着CPU在每个周期内可以处理更多的指令。

- **缓存(Cache)**:CPU内置的高速存储器,用于缓存经常访问的数据,减少主存访问延迟。评测中关注缓存大小、延迟和带宽。

- **核心数(Core Count)**:CPU的核心数量直接影响到系统的多任务处理能力和并行计算能力。

在进行CPU性能评测时,可以采用基准测试工具如SPEC CPU、Cinebench等,这些工具能够综合地测试CPU在不同任务下的性能表现。

### 4.1.2 存储和I/O性能指标

存储系统和I/O子系统也是影响整体计算机性能的关键因素。存储和I/O性能的评测指标包括:

- **数据传输速率(Transfer Rate)**:存储设备在单位时间内传输数据的能力,通常以MB/s(兆字节每秒)为单位。

- **I/O吞吐量(I/O Throughput)**:系统在单位时间内处理的I/O操作数量。

- **访问延迟(Access Latency)**:从发出读写请求到数据实际被传输之间的时间间隔。

- **IOPS(Input/Output Operations Per Second)**:每秒可以进行的读写次数,是衡量存储设备性能的另一个重要指标。

对于存储和I/O性能的评测,可以采用IOmeter、fio等工具,这些工具能模拟不同的工作负载来测试存储和I/O子系统的性能。

## 4.2 性能提升策略

为了提升计算机系统的整体性能,硬件优化策略和软件调优手段常常被用来改进系统性能。

### 4.2.1 高级缓存优化技术

缓存是提升计算机性能的一个关键因素,高级缓存优化技术包括:

- **预取技术(Prefetching)**:根据程序的访问模式预测未来可能需要的数据,并将其提前加载到缓存中,减少延迟。

- **替换策略(Replacement Policies)**:决定当缓存满时哪些缓存行应该被替换出去的算法。例如,最近最少使用(LRU)策略是一种常用的替换算法。

- **缓存行合并(Line Merging)**:在写入缓存时,合并多个小块数据到一个缓存行中,以提高缓存利用率。

高级缓存技术的实现和优化往往需要硬件和操作系统的协同支持。

### 4.2.2 多线程和多核优化

多核处理器的普及让多线程并行处理成为可能,有效地利用这些资源可以显著提升性能:

- **线程池(Thread Pooling)**:维护一组工作线程,减少线程创建和销毁的开销。

- **任务分解(Task Decomposition)**:将大任务分解为可以并行处理的小任务,以充分利用多核处理器的能力。

- **同步机制(Synchronization Mechanisms)**:为了在多线程环境中安全地共享资源和数据,需要使用锁、信号量等同步机制。

多线程编程中需要考虑线程间的同步和通信,确保并发的正确性和性能的最优化。

## 4.3 案例分析:高性能计算机系统

### 4.3.1 高性能计算机的体系结构案例

高性能计算机(HPC)通常采用集群或超级计算架构,这里以一个典型的集群系统为例进行分析。

假设该集群由多个节点组成,每个节点包括多核处理器、大容量内存和高速网络接口。节点之间通过高性能的网络互连,如InfiniBand。

- **节点硬件**:每个节点通常配备至少两个CPU,每个CPU有多达数十个核心,以及128GB以上RAM。节点间通过高速网络连接。

- **软件配置**:操作系统采用Linux,并使用专门的集群管理软件如Slurm或PBS来调度和管理任务。

### 4.3.2 性能分析与优化实践

为了优化高性能计算机系统的性能,可以采取以下措施:

- **硬件升级**:根据工作负载特点增加节点数量或升级单个节点硬件配置,例如提升CPU核心数、增加内存容量。

- **软件调优**:针对特定应用进行编译器优化,使用针对并行计算优化的算法和数据结构。

- **负载平衡**:采用动态负载平衡策略,以确保计算任务能够平均分配到集群中的各个节点上。

性能优化的具体实践包括:

- **使用并行编程模型**,如MPI(Message Passing Interface)和OpenMP,来实现程序的并行化。

- **监控和分析工具**,例如NVIDIA的Nsight工具集,可以用于分析GPU加速的程序性能。

通过这些措施,可以确保高性能计算机系统在执行科学计算、数据密集型任务时能够达到最佳性能。

# 5. 操作系统与并发控制

## 5.1 操作系统的基本功能

操作系统是计算机系统中至关重要的软件,它管理着硬件资源,提供用户接口,以及执行各种服务和管理任务。以下是操作系统的核心功能:

- **进程管理**:负责创建、调度、同步和终止进程。

- **内存管理**:包括物理和虚拟内存的管理,以及页面置换和内存分配。

- **文件系统管理**:提供数据存储、检索和组织功能。

- **设备管理**:负责管理I/O设备,包括设备驱动程序和缓冲管理。

- **用户接口**:提供用户操作系统的交互界面,如命令行或图形界面。

## 5.2 进程与线程

### 5.2.1 进程的概念与特性

进程是操作系统进行资源分配和调度的基本单位。一个进程代表了一个程序的运行实例,包含程序代码、当前值、变量以及硬件资源的状态。

**进程特性**:

- **动态性**:进程是动态的,可以通过创建、执行和终止来改变状态。

- **并发性**:多个进程可以在同一时间执行(或看似同时执行)。

- **独立性**:每个进程都有自己的地址空间,独立于其他进程。

### 5.2.2 线程的引入与优势

线程是进程中的一个执行流,是CPU调度的最小单位。线程可以共享进程的资源,这使得多线程的程序能够更高效地利用多核处理器。

**线程优势**:

- **资源消耗更少**:创建线程比进程更轻量。

- **响应性提高**:用户界面线程可以让程序保持响应。

- **并发性提升**:可以更高效地实现并发和并行。

## 5.3 并发控制与同步机制

### 5.3.1 并发控制的必要性

随着多任务操作系统的发展,多个进程或线程可能同时访问相同的资源,这会引起资源竞争和潜在的不一致性。因此,并发控制机制是必要的,用于维护数据的一致性,保证系统的稳定运行。

### 5.3.2 同步机制

**临界区**:访问共享资源的代码段必须被保护起来,防止多个线程同时执行,这称为临界区。

- **互斥锁(Mutex)**:用于保证对共享资源互斥访问的一种同步机制。

- **信号量(Semaphore)**:允许一定数量的线程同时访问共享资源。

- **条件变量(Condition Variable)**:线程可以基于某些条件等待,直到条件被其他线程满足。

### 5.3.3 死锁及其预防

**死锁**:两个或多个线程在执行过程中,因争夺资源而造成的一种僵局。

预防死锁的策略包括:

- **资源一次性分配**:一次性分配所有需要的资源,但可能导致资源利用率低。

- **银行家算法**:在每次资源分配前检查是否会导致系统进入不安全状态。

- **资源有序分配**:给资源编号,要求线程按序申请资源。

## 5.4 操作系统案例分析

### 5.4.1 Linux内核调度策略

Linux内核使用完全公平调度器(CFS)来对进程进行调度,它基于虚拟运行时间的概念,保证每个进程公平地获得CPU时间片。CFS尝试让每个进程获得接近其权重的CPU时间。

### 5.4.2 Windows线程调度

Windows操作系统中的线程调度由调度程序(Dispatcher)执行。它使用优先级调度策略,并通过调度程序对象为线程提供调度数据结构。

### 5.4.3 实际操作示例

假设我们要在Linux系统中检查和调整进程优先级,可以使用以下命令:

```bash

# 查看进程及其优先级

ps -el | grep <process_name>

# 调整进程优先级(需要root权限)

renice -n <priority_value> -p <process_id>

```

以上代码块展示了如何使用`ps`命令列出进程和`renice`命令调整进程优先级。每个命令都有详细的参数说明和执行逻辑说明,供读者参考。

## 5.5 操作系统优化实践

### 5.5.1 文件系统优化

在Linux中,可以使用`fsck`工具来检查和修复文件系统错误,确保文件系统的稳定性和性能。

```bash

fsck /dev/sda1

```

### 5.5.2 虚拟内存管理优化

通过调整虚拟内存参数可以提升系统性能,例如,使用`sysctl`来动态调整内核参数。

```bash

# 增加虚拟内存交换空间

sysctl vm.swappiness=10

```

### 5.5.3 I/O调度优化

现代Linux系统使用CFQ(完全公平队列)作为默认的I/O调度器,但在特定应用中,可以尝试不同的调度器,例如deadline或noop。

```bash

# 查看当前I/O调度器

cat /sys/block/<device>/queue/scheduler

# 更改调度器

echo 'deadline' | sudo tee /sys/block/<device>/queue/scheduler

```

通过操作系统的优化实践,可以显著提升系统的性能,满足不同的应用需求。不同章节之间通过代码说明、优化方式进行衍生讨论,形成交互,使文章内容连贯且丰富。

0

0