指令集架构揭秘:掌握不同处理器设计的关键

发布时间: 2024-11-15 03:49:52 阅读量: 64 订阅数: 50

真正走向市场化 揭秘中国兆芯X86处理器.pdf

# 1. 指令集架构概述

在计算机科学的浩瀚领域中,指令集架构(Instruction Set Architecture,简称ISA)扮演着至关重要的角色。ISA是软件与硬件之间的桥梁,它定义了计算机处理器能理解和执行的指令集。在本章节中,我们将概述指令集架构的基本概念,并讨论它如何影响处理器设计和整个计算体系结构的发展。ISA既包括了CPU的指令集,也包括了各种寄存器、数据类型、寻址模式、中断以及异常处理机制等元素。理解ISA的重要性在于,它不仅决定了软件开发的效率,还深刻影响了处理器的性能、功耗和成本等关键指标。

## 指令集架构的基本组成

一个典型的指令集架构包括以下几个基本组成部分:

1. **指令集(Instruction Set)**:这是ISA的核心部分,包括了所有可以直接被处理器执行的操作码(操作指令)和它们的格式。

2. **寄存器(Registers)**:处理器内部的小型存储单元,用于快速访问数据和控制信息。

3. **数据类型(Data Types)**:ISA定义了处理器可以操作的数据类型,比如整数、浮点数等。

4. **内存寻址模式(Memory Addressing Modes)**:定义了处理器如何计算和确定数据在内存中的位置。

5. **中断和异常处理(Interrupts and Exception Handling)**:ISA描述了处理器如何响应和处理程序运行时发生的中断和异常。

## 指令集架构的分类

指令集架构可以按照不同的标准进行分类。按照复杂度可以分为复杂指令集计算机(Complex Instruction Set Computing,CISC)和精简指令集计算机(Reduced Instruction Set Computing,RISC)两大类。

- **CISC架构**,如x86系列,倾向于拥有较多的指令,每条指令可以执行复杂的功能。

- **RISC架构**,例如ARM和MIPS,指令较为简单,侧重于通过简化指令集来实现更高的效率和更快的执行速度。

这种分类法对处理器设计、微架构的选择和实现,以及软件编译器的优化策略等有着深远的影响。随着技术的发展,ISA也在不断地演进和创新,以适应新的计算需求和技术趋势。

# 2. 处理器设计的理论基础

### 2.1 微架构的概念与重要性

在处理器设计的领域中,微架构是一个核心概念。它是处理器功能的实现细节,包含了实现指令集架构(ISA)所需的所有硬件组件和它们之间的交互方式。微架构的重要性体现在它直接决定了处理器的性能、功耗以及制造成本。

#### 2.1.1 微架构与指令集架构的关系

微架构与指令集架构密不可分。指令集架构为微架构提供了蓝图,而微架构则是实现这些蓝图的建筑。ISA定义了处理器可以理解和执行的指令集,而微架构涉及这些指令在硬件层面的分解和流水线设计。换言之,微架构是在给定的ISA下,如何设计电路和执行单元以高效地处理指令。

#### 2.1.2 微架构设计的关键因素

微架构设计中,关键因素包括但不限于以下几个方面:

- **流水线深度**:决定指令执行的并行度和延迟。

- **执行单元设计**:影响指令处理速度和效率。

- **寄存器文件的大小与类型**:影响数据存储和访问的性能。

- **缓存架构**:影响处理器的缓存容量和访问速度。

#### 示例代码块

```verilog

// Verilog 示例代码:简单的流水线寄存器

module pipeline_register(

input clk,

input reset,

input [31:0] data_in,

output reg [31:0] data_out

);

always @(posedge clk or posedge reset) begin

if (reset) begin

data_out <= 32'b0;

end else begin

data_out <= data_in;

end

end

endmodule

```

在这个Verilog代码块中,我们展示了一个简单的流水线寄存器的实现。这个寄存器在每个时钟上升沿会将输入的数据传入输出。若复位信号被激活,则将输出置零。这在微架构设计中是非常基础且关键的组件。

### 2.2 指令集架构的设计原则

指令集架构的设计原则是处理器设计的核心,它直接影响到处理器的性能和应用范围。

#### 2.2.1 设计的灵活性与效率

灵活性和效率是设计指令集架构时需要权衡的两个关键指标。灵活性意味着架构能够适应各种计算需求,而效率则指的是在处理特定任务时的执行速度和资源利用率。

#### 2.2.2 设计的可扩展性与兼容性

可扩展性是处理器设计中考虑未来升级和功能扩展的能力。兼容性则指新架构能够与旧版本架构保持一定程度的向后兼容。保持良好的扩展性和兼容性能够使处理器生命周期更长,更容易被市场接受。

### 2.3 处理器流水线技术

处理器流水线技术是现代处理器设计的关键技术之一,它通过提高指令处理的并行度来提升处理速度。

#### 2.3.1 流水线的基本概念

流水线技术将指令的执行过程分解为多个阶段,每个阶段由不同的硬件模块处理。这样,处理器可以在同一时刻处理多条指令的不同阶段,从而提高效率。

#### 2.3.2 流水线的深入分析与优化

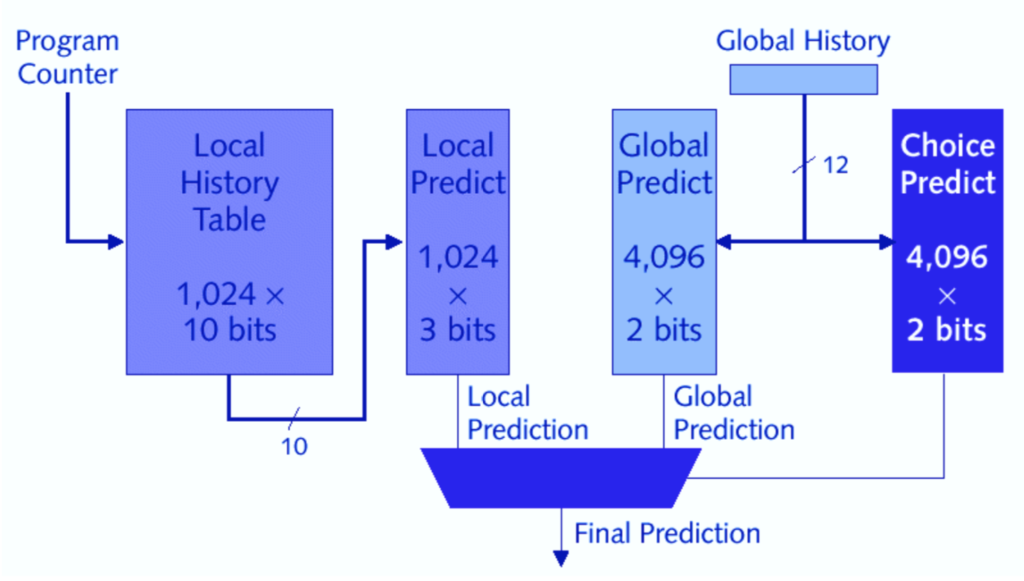

深入理解流水线的设计对于优化处理器性能至关重要。这涉及到平衡各个阶段的执行时间,处理数据冲突和控制冲突等问题。优化措施包括指令调度、分支预测、乱序执行等技术。

#### 流水线表格

| 阶段 | 描述 | 功能 |

| --- | --- | --- |

| IF | 指令获取 | 从内存获取指令 |

| ID | 指令译码 | 解析指令并准备操作数 |

| EX | 执行 | 运算指令的操作 |

| MEM | 访存 | 访问内存读写数据 |

| WB | 写回 | 将结果写回到寄存器 |

以上表格简述了经典的五级流水线阶段及其主要功能。

#### 流水线mermaid流程图

```mermaid

graph TD

IF[IF 指令获取] -->|指令| ID[ID 指令译码]

ID -->|操作数| EX[EX 执行]

EX -->|数据| MEM[MEM 访存]

MEM -->|结果| WB[WB 写回]

```

这个流程图展示了五级流水线的执行流程。

### 2.4 微架构设计的挑战与策略

微架构设计面临诸多挑战,包括实现高频率、低功耗、小面积以及高效率。为了应对这些挑战,设计师需要采取多种策略,如使用创新的电路设计技术、改进缓存和内存管理策略,以及采用先进的制程技术。

#### 2.4.1 电路设计创新

电路设计创新,例如使用多阈值CMOS(Multi-Threshold CMOS, MTCMOS)技术,可以有效地降低静态功耗,延长电池寿命,对于移动设备来说尤为重要。

#### 2.4.2 制程技术的进步

随着制程技术的进步,晶体管的尺寸不断缩小,使得在同样的面积里可以集成更多的晶体管,从而增加了处理器的性能。例如,7纳米制程技术允许在同一芯片上集成数十亿个晶体管。

#### 微架构设计的代码示例

```c++

// C++ 示例代码:微架构设计中的指令调度模拟

void pipeline_schedule() {

// 假设的指令序列

std::vector<Instruction> instructions = fetch_instructions();

// 初始化流水线阶段

std::vector<Stage> stages = initialize_stages();

// 指令调度逻辑

for (auto& instr : instructions) {

// 根据指令类型和资源情况分配至合适的流水线阶段

Stage& stage = find_appropriate_stage(instr, stages);

stage.execute(instr);

}

// 等待所有指令完成执行

wait_for_completion(stages);

}

```

以上代码块模拟了微架构设计中可能遇到的指令调度问题。这展示了一个基本的调度算法,展示了如何为不同类型的指令选择合适的流水线阶段。

### 2.5 微架构的未来发展

随着技术的发展,未来微架构设计将趋向于更高的集成度、更低的功耗和更强的计算能力。

#### 2.5.1 高集成度与多核处理器

多核处理器技术允许在同一芯片上集成多个独立的处理器核心,这提高了并行处理能力,使得多任务处理更为高效。

#### 2.5.2 低功耗设计

低功耗设计不仅对移动设备至关重要,对于数据中心等大规模部署的处理器也同样关键。通过使用先进的电源管理技术,例如动态电压和频率调整(DVFS),可以显著减少能耗。

#### 2.5.3 强大的计算能力

处理器设计者利用并行处理、向量扩展和专用硬件加速器等技术,来提高处理器的计算能力,以应对日益增长的数据处理需求。

以上就是处理器设计的理论基础章节的主要内容,下一章将对主流指令集架构进行深入解析。

# 3. 主流指令集架构解析

## 3.1 CISC架构:x86指令集的演进

### 3.1.1 x86架构的历史与特点

x86架构是计算机历史上最长寿且应用最广泛的指令集架构之一。它的起源可以追溯到1978年的Intel 8086处理器,这一架构最初是为了满足个人电脑对更高性能的需求而设计。x86架构采用了复杂指令集计算(Complex Instruction Set Computing,简称CISC)的理念,其特点是对指令集进行了广泛的扩展,支持多种复杂操作和寻址模式,使得软件可以更加高效地运行。

x86架构的一个显著特点是对向后兼容性的高度

0

0