CPU流水线技术详解:指令执行效率的飞跃

发布时间: 2024-11-15 04:04:55 阅读量: 7 订阅数: 10

# 1. CPU流水线技术概述

## 1.1 什么是CPU流水线技术

CPU流水线技术是现代微处理器设计中的一项核心概念,它允许处理器通过将指令执行过程细分为若干个子阶段(如取指、译码、执行等),并允许这些子阶段在时间上重叠进行来提高处理速度。简而言之,流水线技术是一种提高CPU吞吐量的技术,通过并行处理指令来缩短程序的总体执行时间。

## 1.2 流水线技术的重要性

在计算机发展的早期阶段,处理器的指令执行是顺序且单线程的,随着技术的发展,单个指令周期内能够完成的操作越来越多,但单线程的局限性导致了CPU的性能提升遇到了瓶颈。流水线技术的引入打破了这一局限,通过将指令执行过程分解为更小的单元,实现了指令级并行,极大提升了CPU的执行效率。

## 1.3 流水线技术的发展

流水线技术的发展经历了从简单的顺序流水线到复杂的超流水线和超标量技术的演变。现代处理器中,流水线技术已经变得高度复杂化,包括多个流水级、执行单元以及高级优化技术,如分支预测和指令重排等,都极大地提升了CPU的性能。随着多核心处理器的普及,流水线技术也在不断地与多核心架构进行融合,进一步拓展了其应用的广度和深度。

# 2. CPU流水线的基础理论

### 2.1 CPU基础架构与执行流程

#### 2.1.1 CPU的基本组成与功能

现代CPU(中央处理单元)是计算机的心脏,它负责处理所有的计算任务。一个典型的CPU包含以下几个关键部分:

- 控制单元(CU):负责解释指令集并控制数据流向。

- 算术逻辑单元(ALU):执行所有算术和逻辑运算。

- 寄存器组:存储临时数据和中间运算结果,快速读写访问。

- 缓存:高速存储,存放频繁访问的数据和指令。

CPU执行流程分为几个阶段:取指、译码、执行、访存和写回。每条指令都会经历这些阶段来完成操作。

```mermaid

graph LR

A[取指] --> B[译码]

B --> C[执行]

C --> D[访存]

D --> E[写回]

```

控制单元控制整个流程,从内存中按顺序取指令,译码后通过ALU或其他专用硬件执行,结果可能存储在寄存器或内存中。

#### 2.1.2 指令执行的基本周期

一个指令周期是指CPU执行一条指令所需的时间。它通常包括以下几个步骤:

1. IF(取指):CPU从内存中取指令。

2. ID(译码):解释指令含义和所需操作数。

3. EX(执行):ALU处理指令或进行数据传输。

4. MEM(访存):存取内存数据。

5. WB(写回):将结果写回寄存器。

指令周期的长短取决于CPU设计和当前指令的复杂性。现代CPU会同时处理多条指令来提高效率,这就是流水线技术的基础。

### 2.2 流水线的基本原理

#### 2.2.1 流水线的工作方式

流水线是将指令执行过程分割成若干个子过程,每个子过程由不同的硬件模块处理,而这些模块可以并行工作。这种方式可以使得CPU在一个时钟周期内同时处理多条指令的不同阶段,大幅提高了CPU的吞吐率。

在最简单的五阶段流水线中,每个阶段处理一条指令的一部分,并在下一个时钟周期内移交给下一个阶段。理想情况下,如果每个阶段耗时相同,且流水线被填满,则每个时钟周期都会有一个指令完成。

#### 2.2.2 流水线的分类与特性

流水线可以根据其架构和用途分类为标量流水线和向量流水线,其中标量流水线一次处理一个数据项,而向量流水线可以并行处理多个数据项。

流水线的特性包括:

- **并行性**:在处理多条指令时,流水线的不同阶段可以同时工作。

- **流水线冲突**:由于资源限制或数据依赖,可能发生的冲突,如结构冲突、数据冲突和控制冲突。

- **流水线暂停**:当检测到冲突时,流水线可能需要暂停,以解决冲突。

### 2.3 流水线的性能指标

#### 2.3.1 吞吐量、延迟与加速比

吞吐量是指单位时间内流水线能够处理的指令数。理想情况下,流水线的吞吐量是单周期执行的N倍,其中N是流水线的阶段数。延迟是指完成单个指令从开始到结束所需的总时间。加速比是指采用流水线技术后,相对于非流水线处理器性能的提升比例。

加速比可以用Amdahl定律来描述:加速比 = 1 / ((1 - p) + p/N),其中p是程序中可并行部分的比例,N是流水线的阶段数。

#### 2.3.2 流水线冲突与解决方案

流水线冲突是影响流水线性能的主要因素之一。有三种主要类型的冲突:

- **结构冲突**:不同的指令在同一时刻需要同一个硬件资源。

- **数据冲突**:指令之间存在数据依赖关系,导致潜在的错误结果。

- **控制冲突**:由于分支和跳转指令造成的流水线预测错误。

解决这些冲突的策略包括引入冲突检测和转发机制、增加流水线深度、使用分支预测等技术。

```mermaid

flowchart LR

A[取指] -->|冲突检测| B[冲突解决]

B --> C[译码]

C --> D[执行]

D --> E[访存]

E --> F[写回]

```

在冲突解决模块中,如果检测到冲突,流水线可以暂停,或者使用数据前递技术避免不必要的等待。

以上介绍了CPU流水线的基础理论,包括CPU的基本组成与执行流程、流水线工作原理及其性能指标等。接下来,我们将进一步探讨流水线设计与优化实践。

# 3. 流水线设计与优化实践

## 3.1 流水线的设计策略

### 3.1.1 阶段划分与指令对齐

CPU流水线的设计是将指令执行过程拆分为多个阶段,每个阶段处理指令的一部分。为了实现指令的并行处理,设计者必须确保每个阶段的处理时间大致相同,即流水线的平衡。不平衡的流水线会导致某些阶段成为瓶颈,从而降低整体性能。

在流水线设计中,指令对齐是关键步骤,它涉及将指令序列调整到与流水线的阶段结构相匹配。现代处理器通常采用复杂的指令集,这使得对齐过程变得更为复杂。例如,在x86架构中,由于指令长度可变,设计者必须考虑多种因素来实现有效的对齐策略。

### 3.1.2 数据前递与操作冲突的管理

数据前递是流水线设计中用于解决数据冲突的一种策略。当后续指令需要使用前序指令计算出的结果时,数据前递可以将这些数据直接从流水线的早期阶段传送到需要它们的后期阶段。这样可以减少数据等待的时间,提高流水线的效率。

操作冲突是指在流水线的不同阶段需要访问相同资源时发生的冲突。例如,多条指令在同一时钟周期内需要访问相同的寄存器或内存位置。为了解决操作冲突,硬件设计师通常会采用多种机制,比如设置缓冲区、引入转发逻辑或采用更高级的流水线技术。

## 3.2 流水线的优化技术

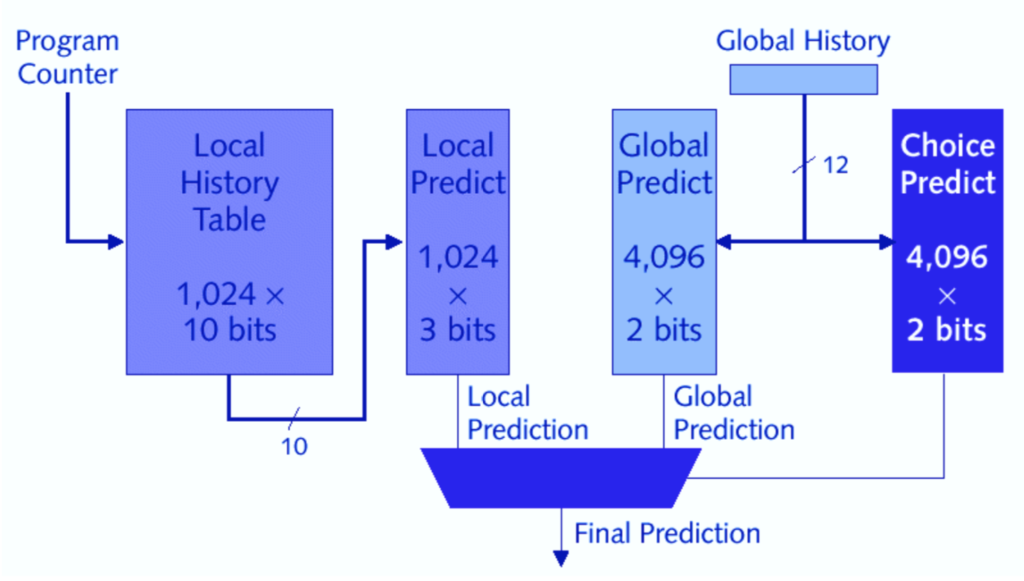

### 3.2.1 动态调度与分支预测

动态调度技术,如超标量处理器中的乱序执行,允许指令在执行时重新排序,以最大限度地减少等待时间并提高指令级并行度。动态调度的关键在于动态地检测和解决数据和控制依赖关系。

分支

0

0