【为何Calibre DRC设置如此关键】:专家解读设置对DRC结果的影响

发布时间: 2025-01-08 15:09:40 阅读量: 6 订阅数: 8

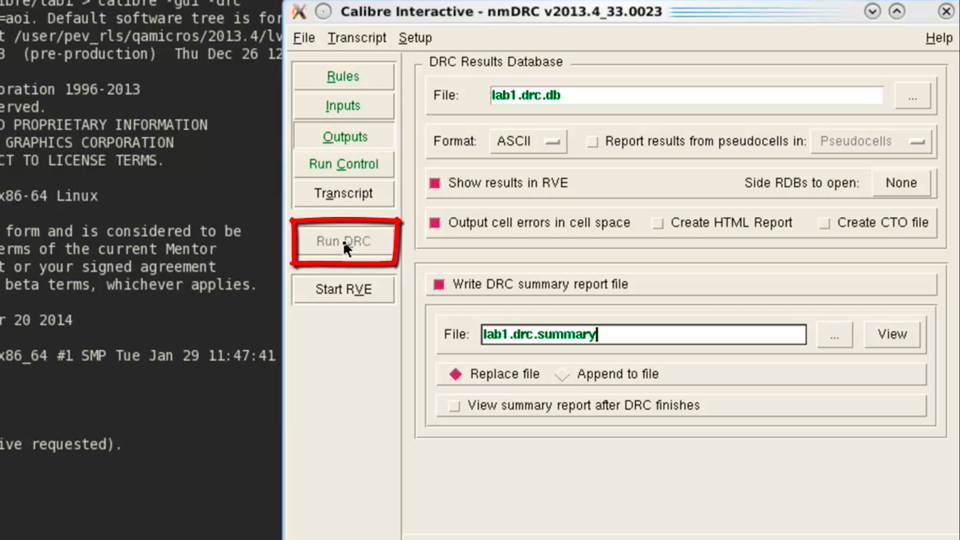

calibre跑DRC、更换DRC文件之前的出现的设置问题

# 摘要

随着集成电路设计复杂性的增加,Calibre设计规则检查(DRC)的重要性日益突出。本文首先介绍了Calibre DRC的基本概念及其在集成电路设计中的作用,随后深入探讨了DRC规则的基础理论,包括规则的类型、参数、条件,以及与制造工艺的关联。实践应用章节详细阐述了Calibre DRC的环境搭建、规则创建和管理以及检查执行和结果分析。深入探讨章节则重点分析了DRC规则的优化、错误处理和流片前DRC设置的重要性。最后,通过案例分析,本文展示了DRC设置策略的执行和经验教训,并对未来Calibre DRC设置的发展趋势与挑战进行了展望。

# 关键字

Calibre DRC;集成电路设计;设计规则检查;规则优化;错误处理;制造工艺关联;技术发展趋向

参考资源链接:[解决calibre DRC导入问题:路径、参数与许可证配置指南](https://wenku.csdn.net/doc/4n9525yshq?spm=1055.2635.3001.10343)

# 1. Calibre DRC的重要性与基本概念

## 1.1 Calibre DRC的简介

Calibre DRC(Design Rule Checking)是集成电路设计中不可或缺的一部分。它是一种自动化工具,用于确保设计符合制造工厂的制造规则。这些规则对于保证芯片的良率至关重要,特别是在纳米级别的设计中。通过自动化校验,DRC帮助设计师避免手工检查可能的疏漏,减少设计周期并提高生产效率。

## 1.2 Calibre DRC的作用

在集成电路设计流程中,Calibre DRC发挥着决定性的作用。它不仅能够检查电路设计是否满足最小尺寸和间距要求,还能检测出潜在的设计缺陷,如短路和开路等问题。通过DRC的验证,设计师可以在实际制造前修正设计错误,从而节省宝贵的时间和资源。

## 1.3 基本概念的深入

深入了解Calibre DRC之前,需要先掌握几个基本概念。首先是“设计规则”,它是由芯片制造商根据其制造工艺能力定义的一系列约束。其次是“设计数据库”,通常包含了物理设计信息,如层、几何形状和互连信息。Calibre DRC利用这些数据与设计规则进行比对,从而识别不符合规则的部分。

以上内容为第一章的概要性描述,接下来的章节将逐步深入探讨DRC规则的理论基础、实践应用以及优化策略等。

# 2. DRC规则的基础理论

## 2.1 设计规则检查(DRC)的定义与目的

### 2.1.1 DRC在集成电路设计中的作用

DRC,即设计规则检查(Design Rule Check),是集成电路设计流程中至关重要的一个环节。它主要用来确保集成电路布局(Layout)符合特定的制造工艺要求。随着半导体技术的发展,芯片设计的复杂性越来越高,任何小小的错误都可能导致芯片制造失败或功能异常。因此,DRC成为了保证设计质量不可或缺的一部分。

在芯片设计中,DRC的作用主要体现在以下几个方面:

- **确保可靠性**:通过DRC可以发现设计中可能导致制造缺陷的问题,从而避免这些问题在硅片制造过程中出现,减少产品的不合格率。

- **提高良率**:良好的DRC过程能够帮助设计师及时修正错误,提高集成电路的制造良率。

- **加速产品上市时间**:尽早发现和修复错误,可以缩短设计周期,加速产品上市时间。

### 2.1.2 DRC的类别及其基本原理

DRC可以分为静态DRC和动态DRC两大类:

- **静态DRC(Static DRC)**:这是最常见也是最基础的DRC类型,它关注的是在某个时刻电路的规则符合性。静态DRC通常包括检查设计中的特征尺寸(如线宽、间距)、设计的对称性、规则层对层的对准等。静态DRC的检查是基于预先定义的设计规则库进行的,当布局违反了这些规则时,将被标记为错误。

- **动态DRC(Dynamic DRC)**:也被称为时序DRC,它关注的是电路在不同工作条件下的规则符合性,特别是时序约束。动态DRC主要应用于时序分析和验证阶段,它会考虑电压、温度等因素的影响,确保电路在不同的工作环境下均能正常工作。

DRC的基本原理在于通过预先定义的规则来分析设计图,规则涵盖了制造工艺能够实现的最小尺寸限制、层间对齐要求以及材料兼容性等方面。这些规则是根据半导体工厂的实际制造能力制定的,确保设计能够在当前的工艺技术下被成功制造。

## 2.2 DRC规则的构成要素

### 2.2.1 设计规则的类型

DRC规则涉及设计的多个方面,包括但不限于以下几种类型:

- **几何规则(Geometric Rules)**:涉及层的定义、线宽、间距、边缘距离等。

- **电学规则(Electrical Rules)**:涉及电容、电阻、连线间的串扰等电气特性。

- **设计约束规则(Design Constraint Rules)**:涉及芯片尺寸、封装、引脚布局等。

- **制造规则(Manufacturing Rules)**:涉及层的堆叠、材料选择等。

### 2.2.2 规则的参数和条件

每一条规则都会定义一个或多个参数和条件。这些参数描述了规则的极限值,而条件则指出了规则适用的特定情况。例如,一条线宽规则可能包含最小线宽参数,而且该参数可能根据不同的制造工艺或不同的层有所不同。

规则参数通常包括:

- **最小值(Minimum)**:如最小线宽、最小间距等。

- **最大值(Maximum)**:如最大通孔直径、最大芯片尺寸等。

- **精确值(Exact)**:对于某些特定要求,如标准单元的高度、某些层的间距等,必须严格遵循一个特定值。

规则条件通常描述了规则适用的上下文,比如:

- **环境条件**:温度、电压水平。

- **特定层或区域**:只有在特定层或特定区域内的布局才受到该规则的约束。

## 2.3 DRC规则的理论基础

### 2.3.1 制造工艺与设计规则的关联

设计规则是基于制造工艺的限制和能力来设定的。随着工艺节点的缩小,制造工艺对设计规则的影响越来越大。例如,深紫外光(DUV)或极紫外光(EUV)光刻技术的限制会直接影响到线宽和间距的规则。DRC规则必须充分考虑这些工艺限制,以确保最终的产品设计能够在芯片制造过程中得以实现。

### 2.3.2 理想规则与实际规则的差异

尽管DRC规则试图模拟实际的制造过程,但在理想与实际之间仍然存在差异。理想规则是基于理论计算和假设的,但实际规则需要考虑到制造过程中的各种随机性和不确定性因素。因此,设计工程师在使用DRC时必须理解这些规则与实际制造之间的差异,并在必要时进行设计上的调整。例如,为降低制造过程中产生的随机缺陷,可能需要在某些区域引入额外的设计冗余。

在了解了DRC的基础理论之后,工程师们就可以深入研究具体的DRC设置和应用了。Calibre DRC作为业界广泛使用的DRC工具之一,其详细的环境搭建、规则创建以及检查执行等将在下一章节深入探讨。

在本章节,我们介绍了DRC的基本定义、目的和重要性,并且对DRC的规则构成进行了详细解析。接下来,我们将深入探讨Calibre DRC的实际应用,包括环境搭建、规则管理以及结果分析。

# 3. Calibre DRC的实践应用

## 3.1 Calibre DRC的环境搭建与配置

### 环境搭建的步骤和注意事项

在集成电路设计行业,Calibre DRC 是一个不可或缺的工具,它帮助工程师确保设计满足制造工艺的规则要求。Calibre 环境搭建是进行DRC检查的前提,以下是一些重要的步骤和注意事项。

首先,确认你有安装Calibre工具的计算机环境。Calibre一般在Unix/Linux系统中运行,确保系统环境符合安装要求。接下来,下载所需的Calibre软件包,并根据软件包中的安装指南执行安装。

安装完成后,重点是进行环境变量配置,这通常涉及到修改bashrc或相应的shell配置文件,添加Calibre相关命令的路径,如:

```bash

export PATH=/path/to/calibre/bin:$PATH

```

确保配置文件正确无误后,使用`source`命令重新加载配置文件,或关闭并重新打开终端窗口。

配置Calibre环境时,需要注意以下几点:

1. 保持环境一致性。对于多人协作的项目,最好在服务器或共享系统上安装Calibre,以保证每个人都在相同的环境下工作。

2. 使用最新版本的Calibre,以便利用最新的功能和性能优化。

3. 确保操作系统和Calibre软件的依赖库都更新到最新状态,以避免兼容性问题。

4. 对于大型项目,可以考虑

0

0