镁光HMC Gen2 160GB/s DRAM:高带宽封装与特性概览

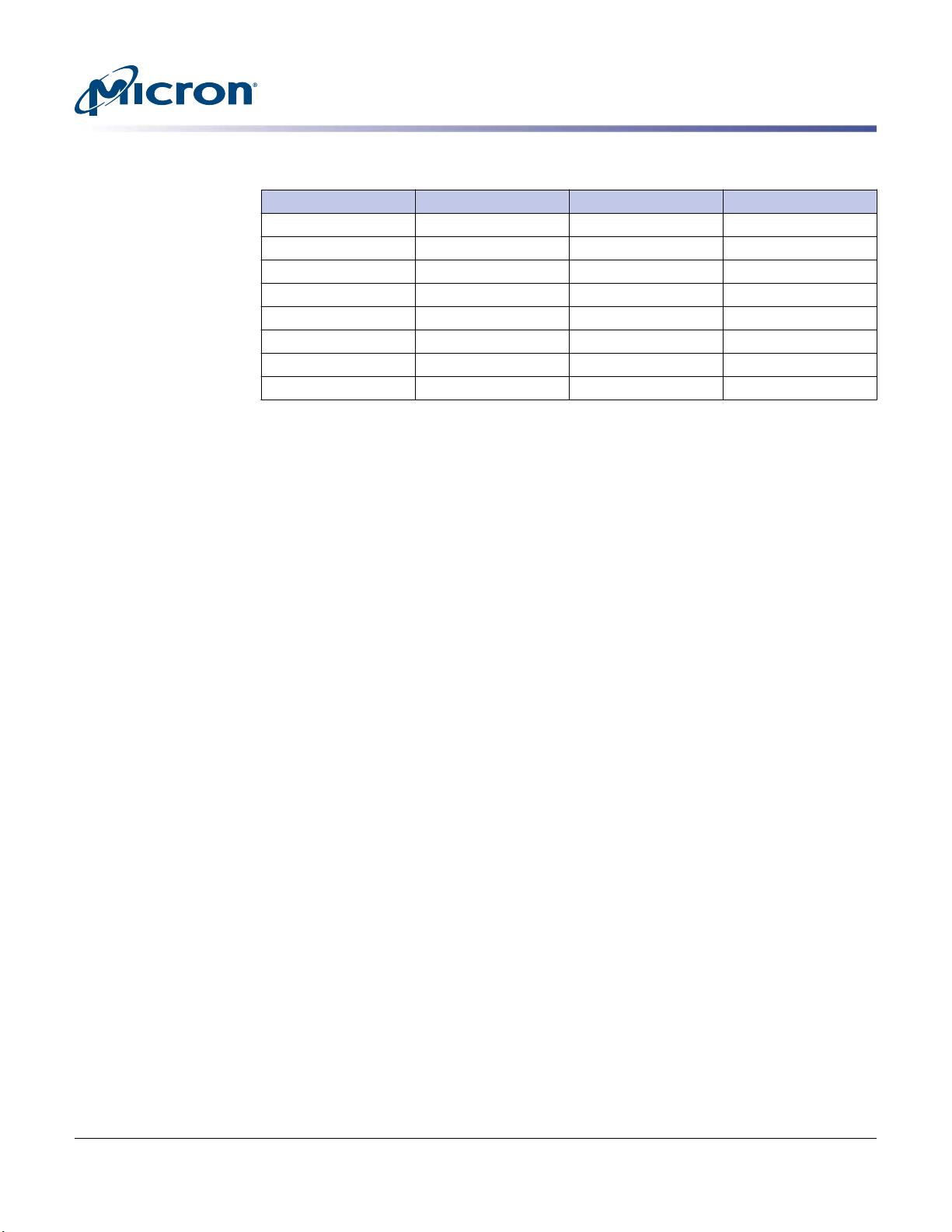

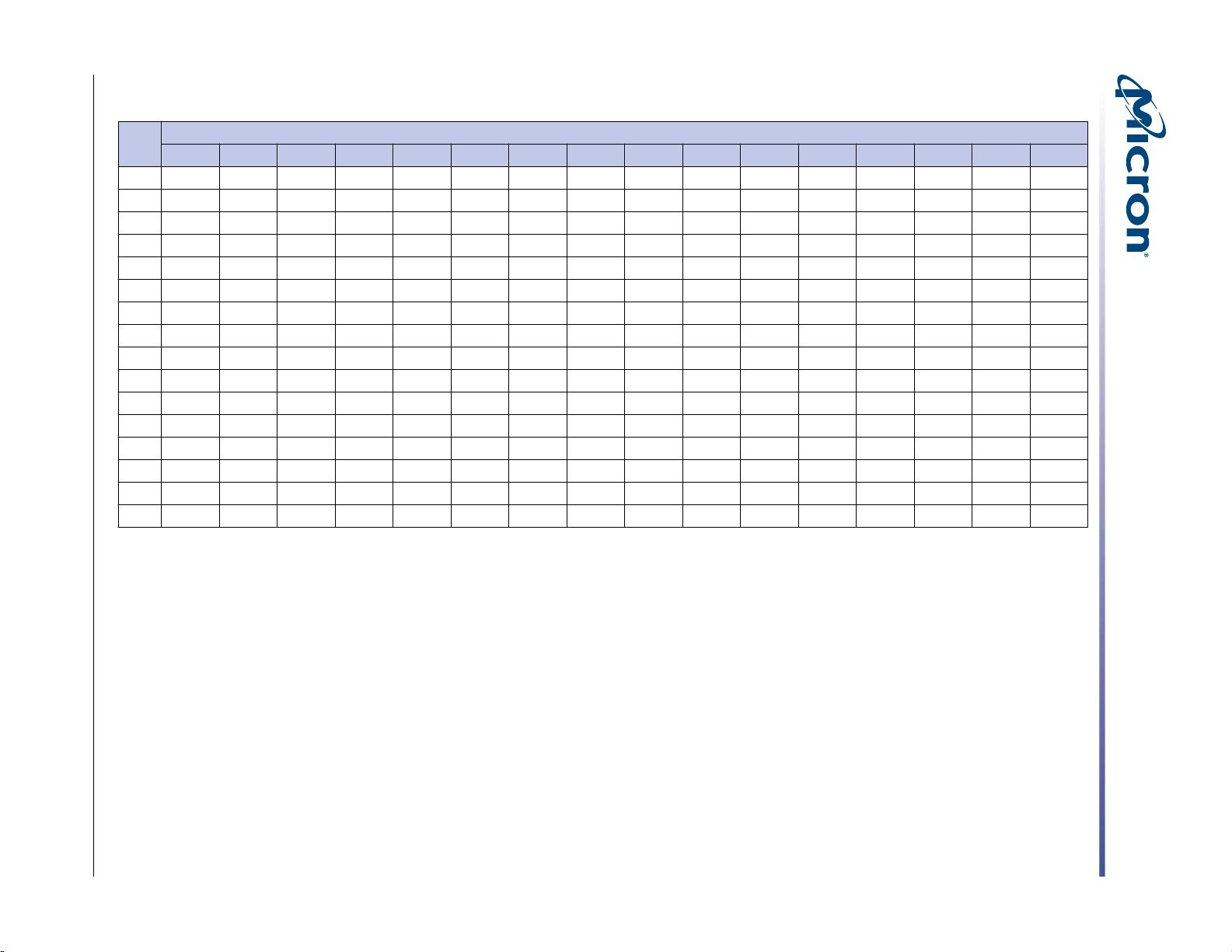

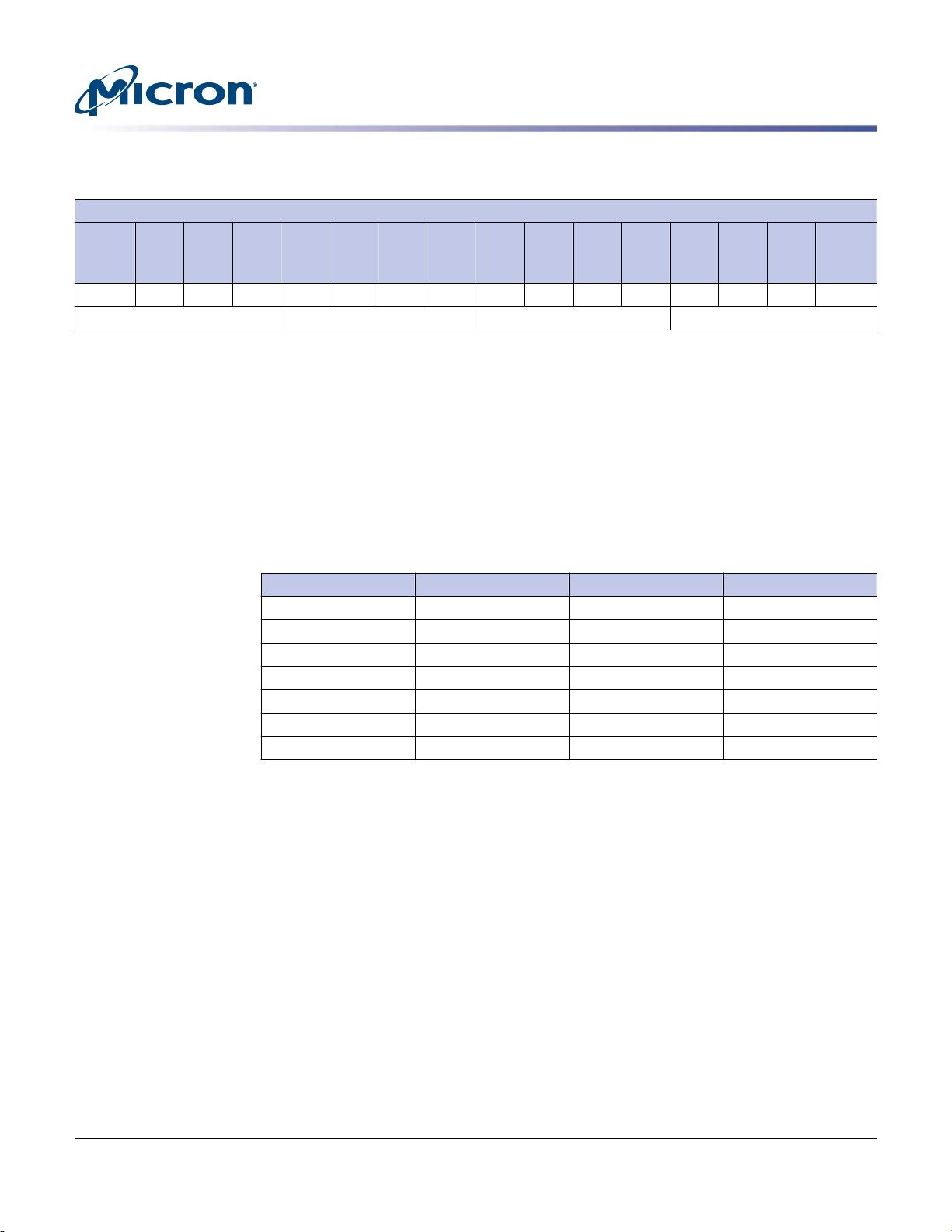

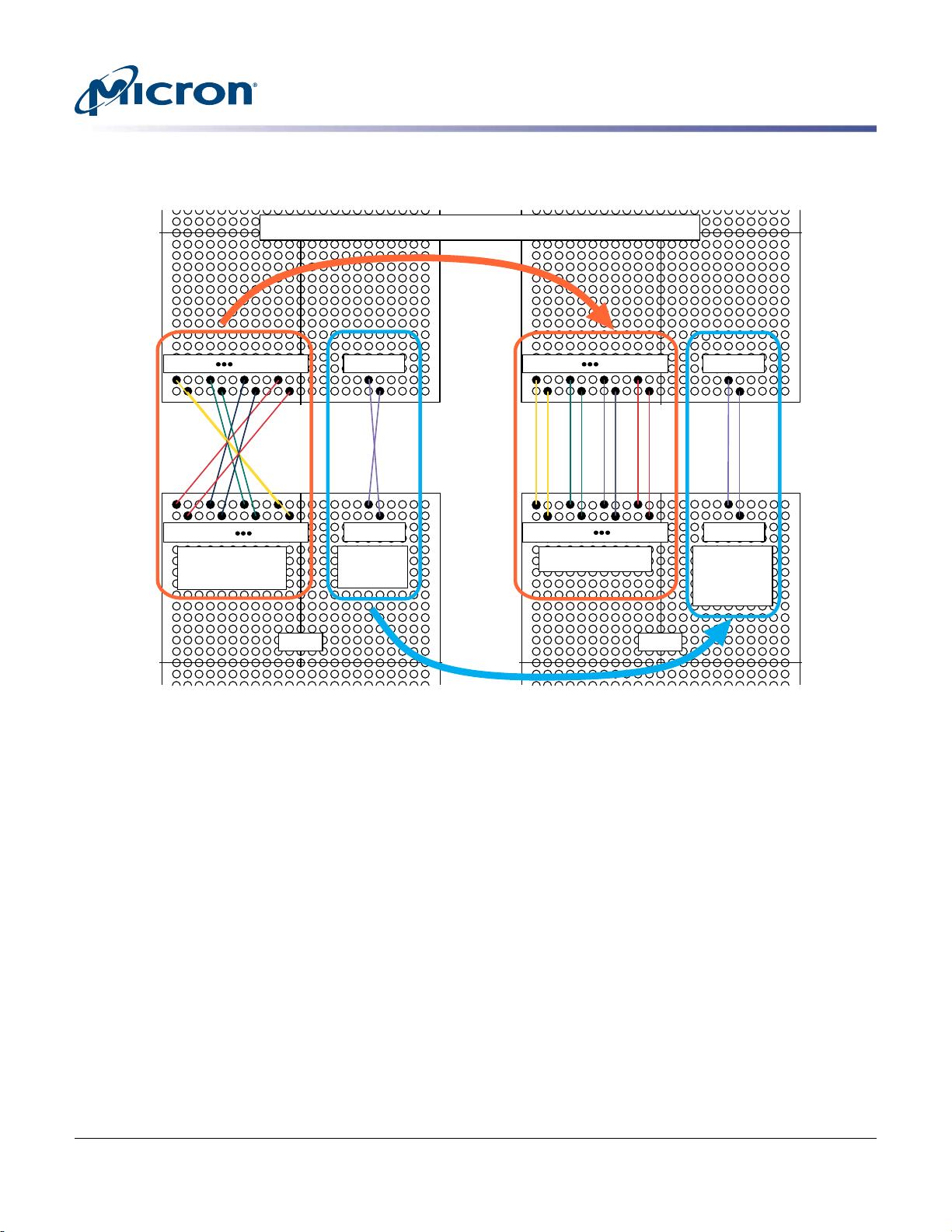

镁光公司(Micron Technology)的Hybrid Memory Cube (HMC) 是一种先进的内存解决方案,它将四个DRAMdie和一个逻辑die整合在一个单一封装中,利用通过硅通孔(Through-Silicon Via, TSV)技术进行堆叠。HMC的设计旨在提供高度集成和高带宽的数据存储与处理能力。 HMC Gen2的一个具体例子是MT43A4G40200-2GB4HDRAMstack,其特点是2GB的配置,包含128个独立的内存银行。每个内存银行被组织成16个独立的内存库(Vaults),采用了封闭页面内存架构,这意味着每个vault都有内置的内存控制器,能自动管理刷新控制,确保在各种温度下的数据完整性。此外,内部集成了错误检测和纠正(ECC)功能,以及高级RAS特性如数据擦除,以提高内存的可靠性。 在接口方面,HMC采用1.0V的VDD电源,VTT、VTR和VDDPLL设置为1.2V,而VDDK为1.5V。数据传输接口支持高达10/12.5/15Gb/s的串行连接器(SerDes I/O interface),可以配置成最多四条16-lane全双工的链接,从而实现高达160GB/s的带宽。这种设计支持基于包的数据和命令交互,能够处理1到128字节不等的数据包,且配备循环冗余校验(CRC)错误检测,出现错误时会自动重试。此外,每个链接都支持电源管理,TSV技术的应用使得封装密度更高,集成度更强。 HMC还具备内置自测试(BIST)功能,便于在制造过程中检测和修复潜在问题,以及JTAG接口(遵循IEEE 1149.1-2001和1149.6标准)和I2C接口(UM-10204 I2C bus specification),提供了灵活的调试和控制手段。这些特性共同确保了HMC在高性能计算、数据中心和嵌入式系统中的广泛应用,是现代高性能计算和存储系统中的关键组件。

剩余104页未读,继续阅读

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- AirKiss技术详解:无线传递信息与智能家居连接

- Hibernate主键生成策略详解

- 操作系统实验:位示图法管理磁盘空闲空间

- JSON详解:数据交换的主流格式

- Win7安装Ubuntu双系统详细指南

- FPGA内部结构与工作原理探索

- 信用评分模型解析:WOE、IV与ROC

- 使用LVS+Keepalived构建高可用负载均衡集群

- 微信小程序驱动餐饮与服装业创新转型:便捷管理与低成本优势

- 机器学习入门指南:从基础到进阶

- 解决Win7 IIS配置错误500.22与0x80070032

- SQL-DFS:优化HDFS小文件存储的解决方案

- Hadoop、Hbase、Spark环境部署与主机配置详解

- Kisso:加密会话Cookie实现的单点登录SSO

- OpenCV读取与拼接多幅图像教程

- QT实战:轻松生成与解析JSON数据

信息提交成功

信息提交成功