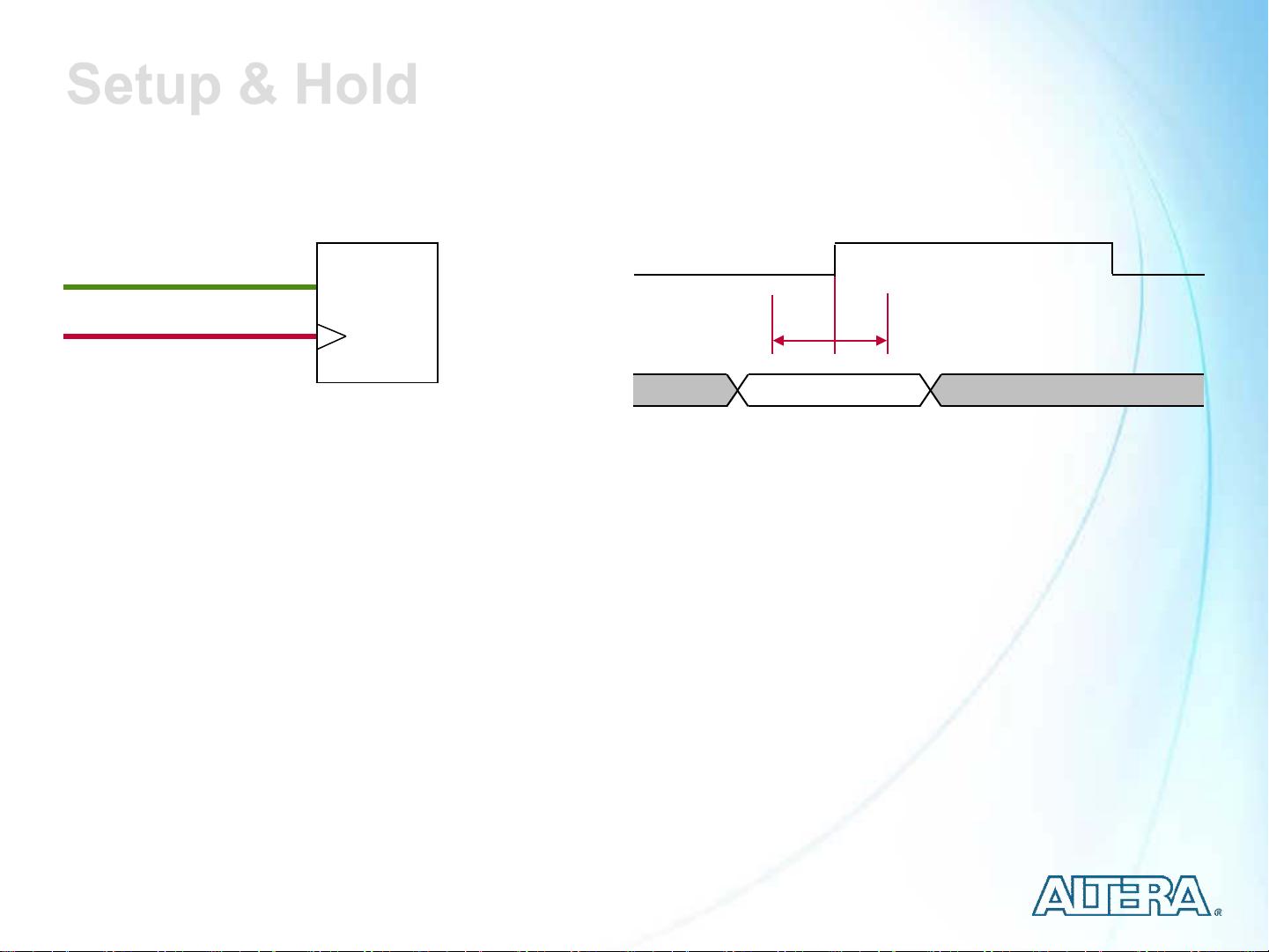

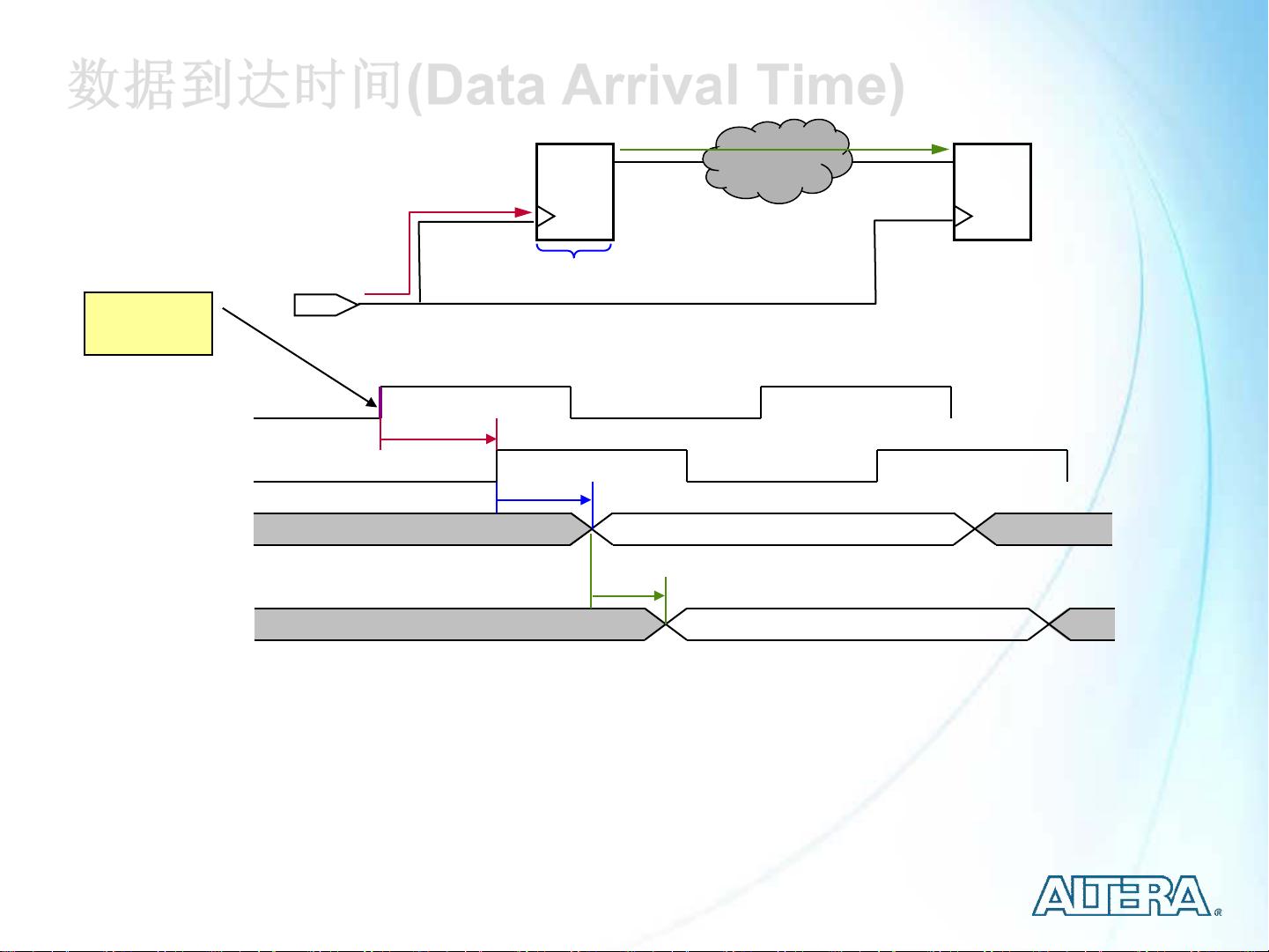

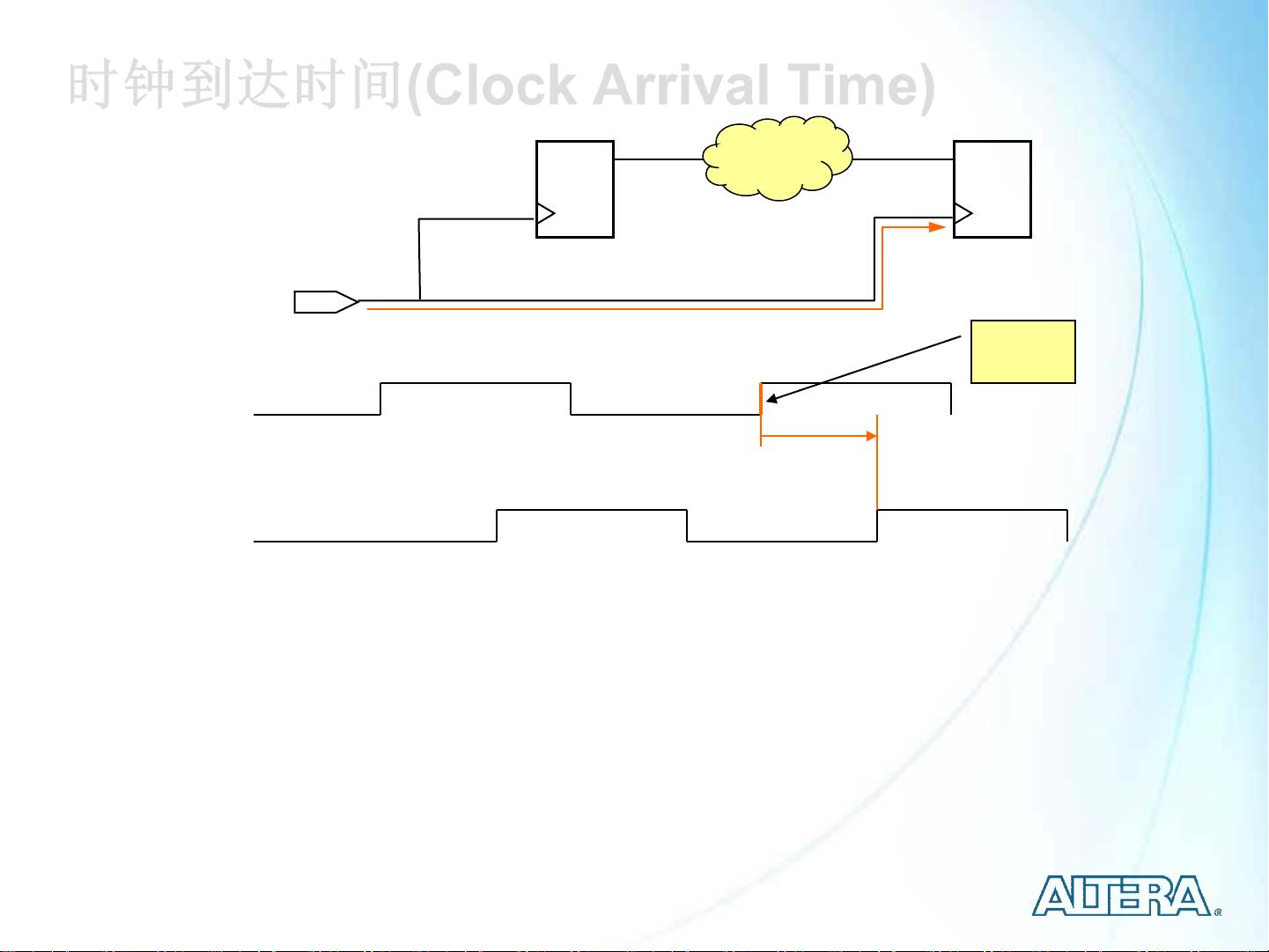

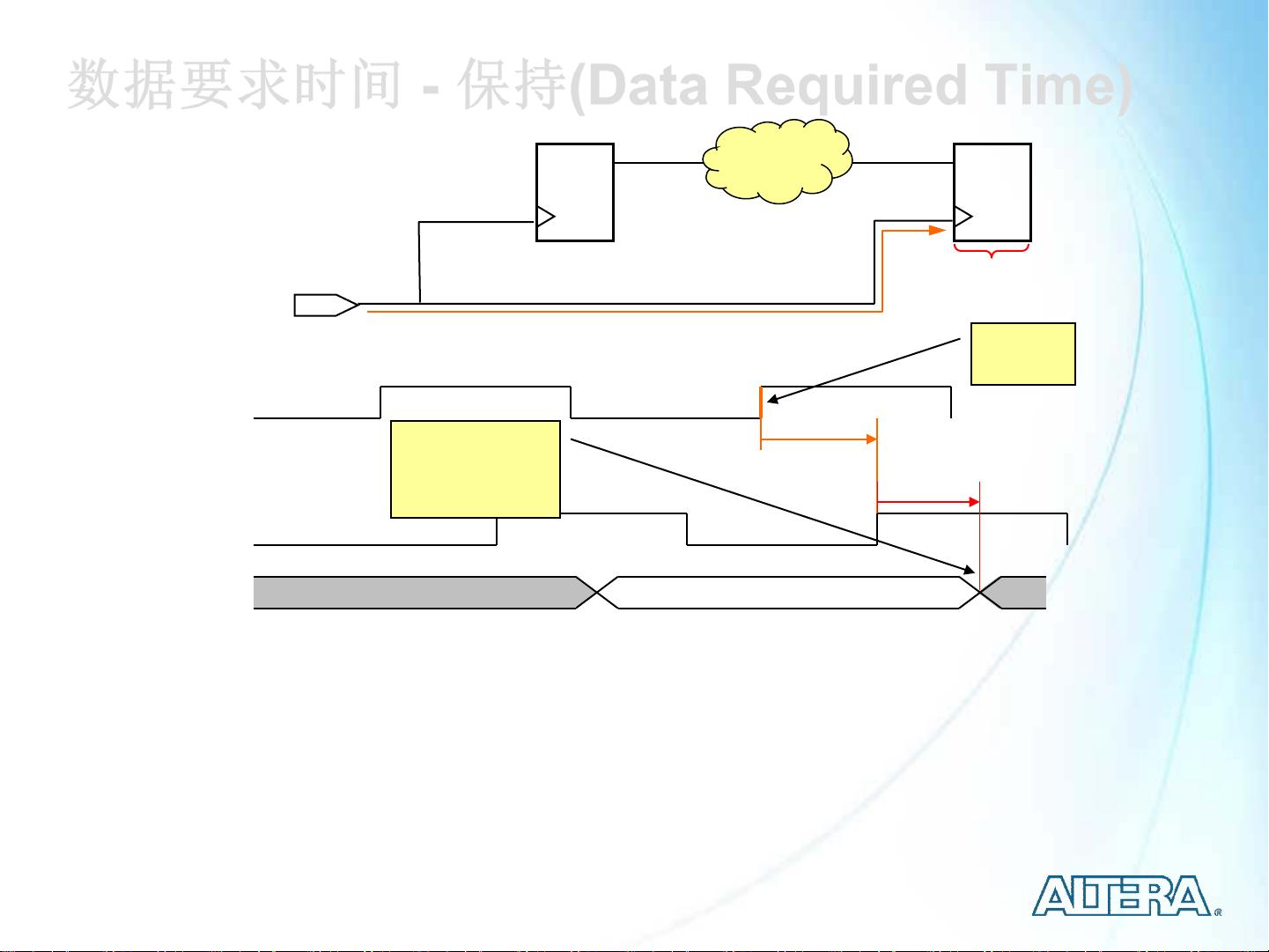

"TimeQuest是Altera公司提供的一个高级时序分析工具,主要应用于FPGA设计中的时序验证。这个教程详细介绍了如何使用TimeQuest进行时序分析,包括基本概念、分析流程、使用方法以及如何处理SDC Timing Constraints。教程特别强调了TimeQuest相对于传统时序分析器的优势,如其用户友好的GUI界面、对Synopsys设计约束(SDC)格式的支持和全面的脚本功能。" 在深入TimeQuest时序分析教程之前,我们首先理解一下时序分析的重要性。在FPGA设计中,确保电路在规定的时间内正确工作是至关重要的,这便是时序分析的目标。TimeQuest作为一个强大的工具,能够帮助设计师检查和优化设计的时序性能,确保设计满足时钟周期要求。 "分析流程"部分会讲解如何使用TimeQuest进行设计的时序分析,通常包括以下几个步骤: 1. **设定约束**:在设计中定义关键路径、时钟域转换等要求,这可以通过TimeQuest的GUI或SDC文件完成。 2. **综合和布局布线**:使用Quartus II进行逻辑综合和物理实现,TimeQuest会在这个过程中收集必要的时序信息。 3. **时序分析**:TimeQuest分析设计的时序路径,确定是否满足设定的约束。 4. **报告生成**:生成详细的时序报告,显示哪些路径接近或者超过了时序限制,以及可能的优化建议。 5. **迭代优化**:根据报告结果,设计师可能需要调整设计或修改约束,然后重复上述步骤,直到满足所有的时序要求。 "时序分析中基本概念"部分将涵盖时间延迟、最大时钟频率(即工作频率)、路径延迟、建立时间(Setup Time)和保持时间(Hold Time)等关键概念。这些概念是理解和使用TimeQuest的基础,也是确保设计正确性的关键。 "使用TimeQuest"章节会详细介绍如何操作TimeQuest的界面,包括添加和编辑约束、运行时序分析、查看和解析时序报告等。TimeQuest的用户友好界面使得非专业人员也能相对容易地理解和使用。 "SDC Timing Constraints"部分将讨论SDC文件格式,这是业界广泛接受的标准,用于定义设计的时序约束。TimeQuest不仅支持直接读取和解析SDC文件,还提供了简化SDC学习和使用的功能,使得用户能够更高效地管理设计的时序约束。 "移植老的约束文件"可能涉及到从旧版本工具或不同格式的约束文件转换到TimeQuest的SDC格式,这对于维护现有设计或升级工具链的用户来说是非常实用的。 TimeQuest时序分析教程是理解和掌握FPGA设计中时序验证的宝贵资源,无论是初学者还是经验丰富的工程师,都能从中受益。通过这个教程的学习,设计师可以更有效地使用TimeQuest进行时序分析,从而优化设计性能,保证设计的可靠性。

剩余115页未读,继续阅读

- 粉丝: 96

- 资源: 6

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析

信息提交成功

信息提交成功