DM9000A Ethernet Controller 数据手册

需积分: 10 48 浏览量

更新于2024-08-02

收藏 1.71MB PDF 举报

"DM9000A是DAVICOM半导体公司生产的一款集成以太网控制器,具有通用处理器接口。该器件集成了10/100M自适应以太网PHY,支持8位和16位两种工作模式,适用于各种嵌入式系统和网络设备。DM9000A的数据手册提供了详细的描述、块图、特性、引脚配置、引脚描述以及供应商控制和状态寄存器集等关键信息,帮助设计者理解和应用此芯片。"

DM9000A以太网控制器的主要特点包括:

1. **集成10/100M自适应功能**:能够自动检测并适应10Mbps或100Mbps的网络速度。

2. **通用处理器接口**:支持与多种微处理器进行通信,无论是8位还是16位模式,提供灵活的系统集成方案。

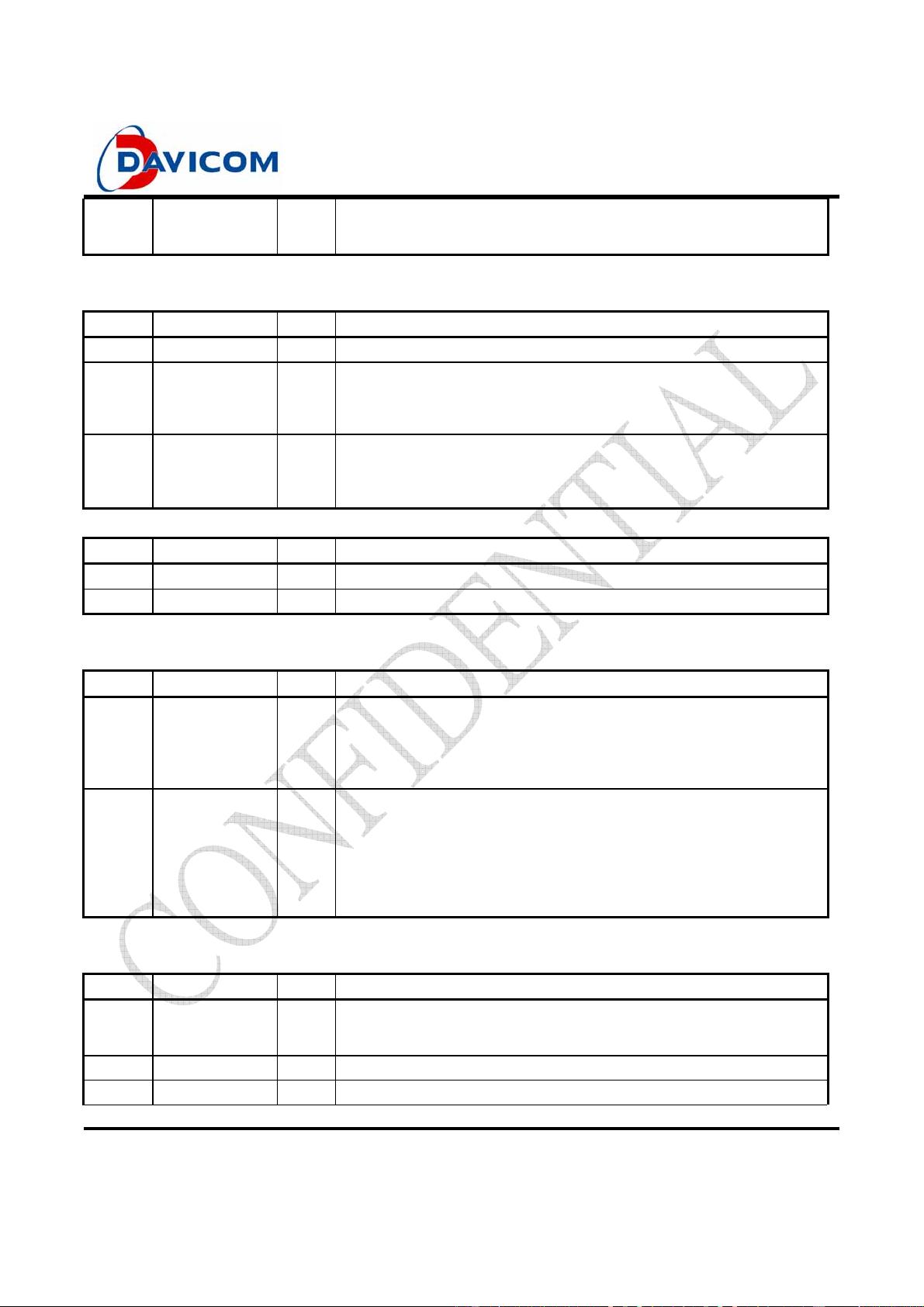

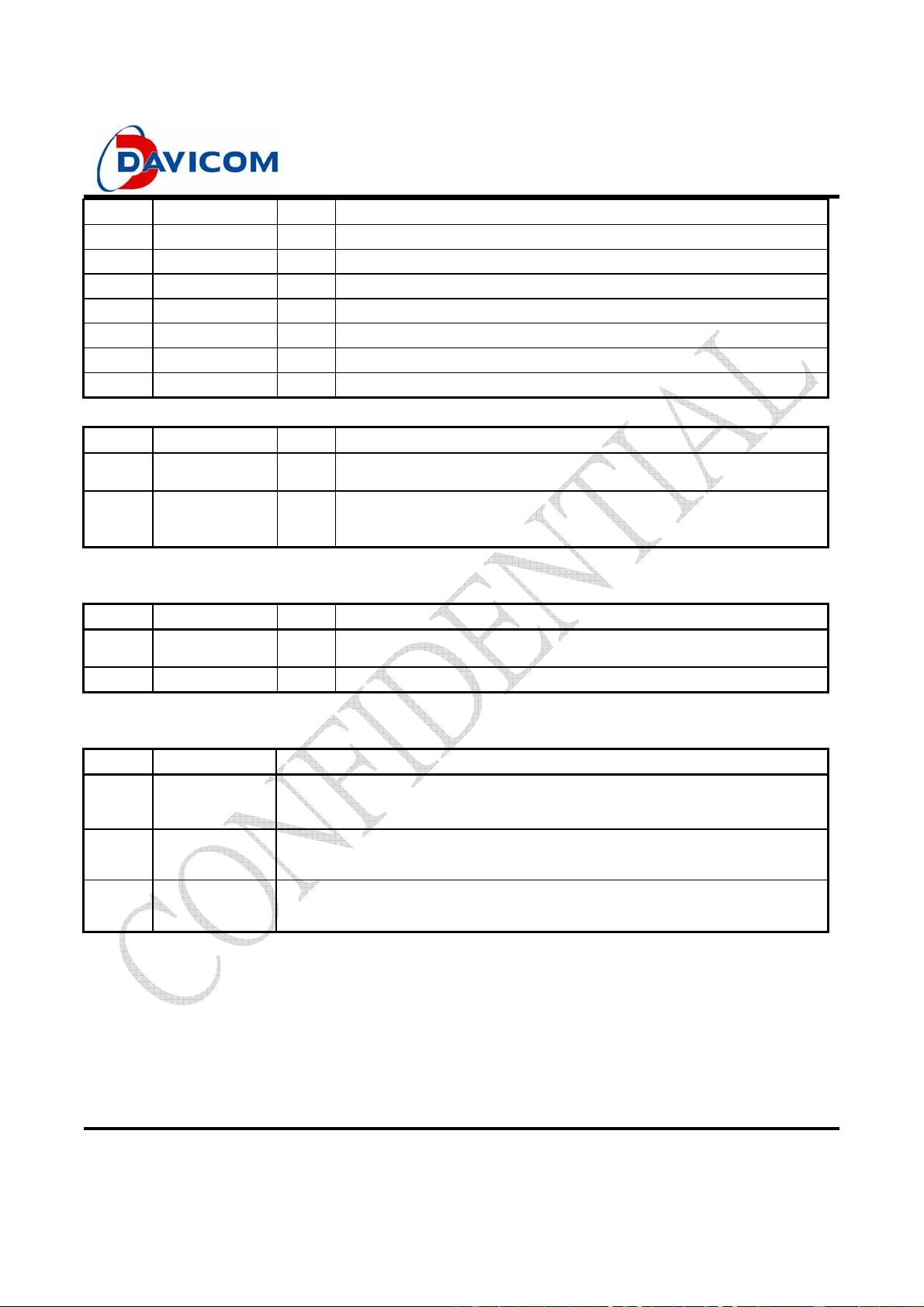

3. **丰富的引脚配置**:包括16-bit模式和8-bit模式两种配置,以适应不同硬件平台的需求。

4. **多接口支持**:包括处理器接口、EEPROM接口、时钟接口、LED接口和物理层接口(PHY),满足不同功能模块的需求。

5. **电源引脚和strap pins**:用于供电和配置芯片,确保稳定运行。

在引脚配置部分,DM9000A分为16-bit模式和8-bit模式,分别列出了对应的引脚分配,以适应不同宽度的总线操作。处理器接口详细描述了在8-bit模式下的工作方式,而EEPROM接口则允许存储配置信息。时钟接口用于接收外部时钟信号,确保数据传输的同步。LED接口则可用于指示网络状态,如连接、活动等。10/100 PHY/Fiber接口负责与物理网络介质的交互。

DM9000A的数据手册还详细介绍了各个控制和状态寄存器,这些寄存器是与处理器通信的关键,包括:

1. **网络控制寄存器(00H)**:用于设置网络工作模式、中断控制等。

2. **网络状态寄存器(01H)**:反映网络连接状态、错误信息等。

3. **TX控制寄存器(02H)**:管理数据发送过程,如设置发送队列、优先级等。

4. **TX状态寄存器I(03H)和II(04H)**:记录发送包的状态,如发送完成、错误信息等。

5. **RX控制寄存器(05H)**:控制数据接收,如接收使能、地址过滤等。

6. **RX状态寄存器(06H)**:提供接收数据的相关信息,如帧接收状态、错误标志等。

通过这些寄存器,开发者可以实现对DM9000A的精细控制,以实现高效、可靠的网络通信功能。同时,电源引脚和strap pins的设定也是确保芯片正确初始化和运行的重要环节。综合以上信息,设计人员可以全面理解DM9000A的功能特性,并在实际项目中有效利用。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2015-06-02 上传

157 浏览量

点击了解资源详情

点击了解资源详情