A Fast SNR Estimation Method for Sigma-Delta Modulator

Design

∗

Jiandong Cheng, Guoyong Shi, and Ailin Zhang

School of Microelectronics, Shanghai Jiao Tong University,

Shanghai 200240, China

shiguoyong@ic.sjtu.edu.cn

Abstract—This paper presents a fast symbolic method for computation

of the signal-to-noise ratio (SNR) of switched-capacitor sigma-delta

modulators. The key idea is to use a Taylor expansion polynomial to

approximate the rational expression of a noise transfer function (NTF).

This new method can be used in automatic optimization tools developed

for s witched-capacitor sigma-delta modulator design.

Index Terms—Sigma-Delta Modulator, Switched-Capacitor, Symbolic

Analysis.

I. INTRODUCTION

Switched-capacitor (SC) ΣΔ Modulators (SDMs) are widely used

for high performance analog signal processing [1]–[4]. Despite the

popularity of SDMs, automatic design tools ranging from circuit-

level to system-level are still lacking. Due to the mixed-signal nature,

circuit-level simulation by a SPICE simulator is extremely slow for

design verification. To quickly evaluate the performance of an SDM

design, behavior-level simulations are now popular [5], [6].

Recently, there have appeared quite a number of publications

addressing automatic synthesis methods of SDMs, which include

automatic design of loop-transfer function coefficients [7], design

space exploration [8], a synthesis method considering SNR (signal-

noise ratio) variation [9], topology optimization [10], and a method

to synthesize from architecture to netlist [11], etc. Other research on

system-level synthesis includes [12]–[14], etc.

Despite the variety of efforts, the desire for automatic SDM

synthesis is still far from reality. There are a number of intermediate

steps in the synthesis cycle requiring time-consuming evaluations,

such as proper selection of the loop-filter coefficients to guarantee

stability, speed and resolution tradeoff, and SNR evaluations, among

others. Design optimization usually requires running a synthesis

cycle for many times. If each run of the synthesis cycle is too

time-consuming, the design space exploration capability is damaged.

Therefore, satisfactory synthesis greatly depends on the efficiency in

every intermediate synthesis step.

In this work we specifically consider the issue of SNR computation

and propose a symbolic method for efficiency. Establishing SNR as

a function of the loop-transfer design parameters is also fundamental

to optimizing an SDM. Although the proposed method is an approx-

imate technique, it runs extremely fast with satisfactory accuracy.

In the following sections, we first make a simple review on the

SDM design in Section II, then point out that the loop-transfer design

of a switched-capacitor SDM can be analyzed by a symbolic analysis

tool in Section III. An efficient approximate calculation method for

SNR is introduced in Section IV. Test results for justifying the

accuracy of SNR approximation are reported in Section V. Section

VI concludes the paper.

∗

This research was supported in part by the National Natural Science

Foundation of China (NSFC Grant No. 61176129) and by the SJTU-Synopsys

Joint Research Project (2010-2013) sponsored by Synopsys, Inc.

II. REVIEW OF SIGMA-DELTA MODULATOR

The idea of SDM is to use a low-resolution internal ADC to achieve

high resolution by oversampling and feedback (noise-shaping). The

internal ADC could be single-bit, i.e. a two-level comparator [1].

Besides choosing a proper oversampling ratio (OSR), the design of

the loop-filter’s transfer function influences the SDM performance

greatly.

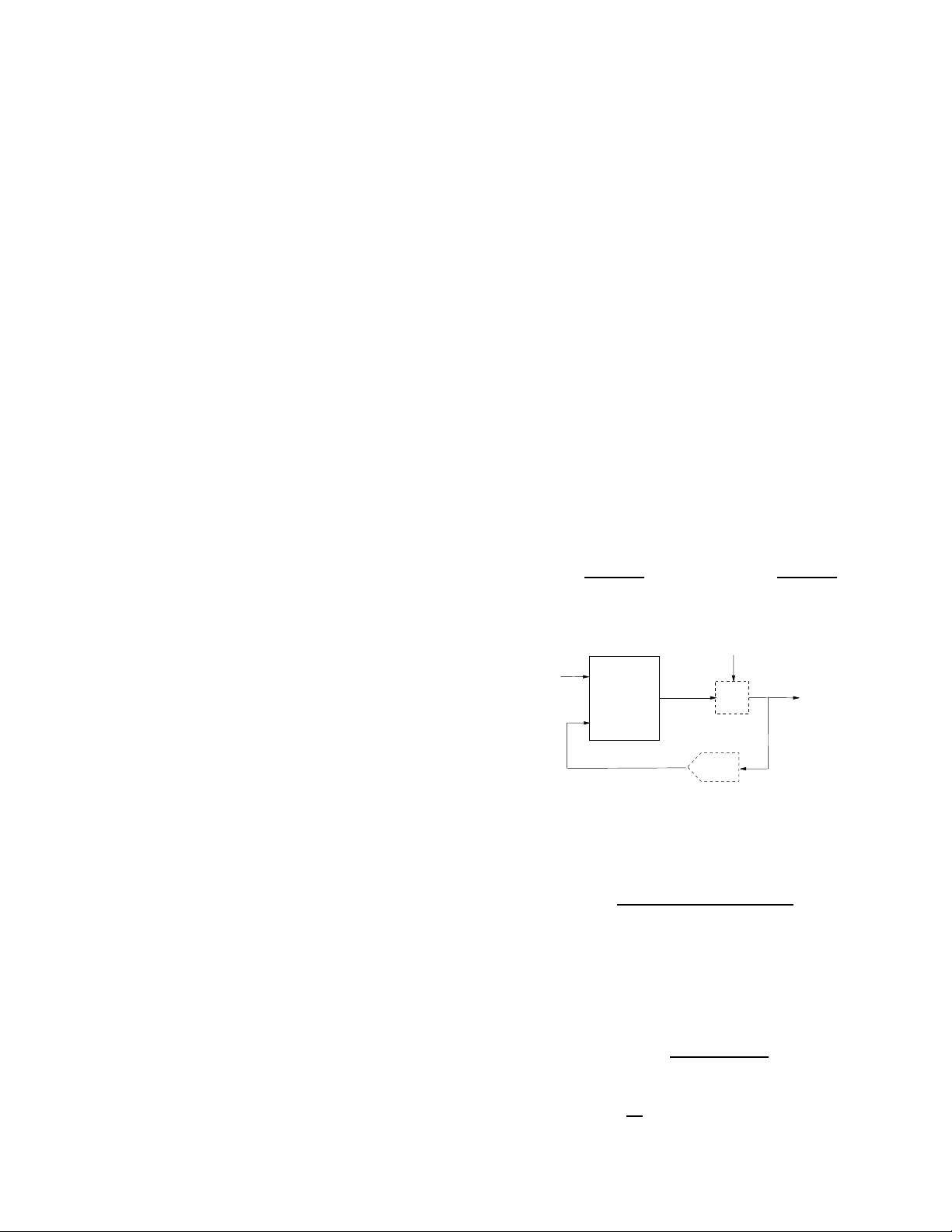

Fig. 1 shows the general structure of a single-stage SDM [4], where

u is the analog input and v is the digital output, and e stands for the

additive quantization noise. Overall, the output can be formulated as

[4]

V (z)=STF(z)U (z)+NTF(z)E(z) (1)

where the signal transfer function (STF) and the noise transfer

function (NTF) are

STF(z)=

L

0

(z)

1+L

1

(z)

and NTF(z)=

1

1+L

1

(z)

. (2)

Here, the plus in the denominator 1+L

1

(z) is due to a negative

feedback used in the DAC (digital-to-analog conversion) path.

V

0

L

1

DAC

Filter

Loop

Q

U

Y

E

L

Fig. 1. A single-stage ΣΔ modulator.

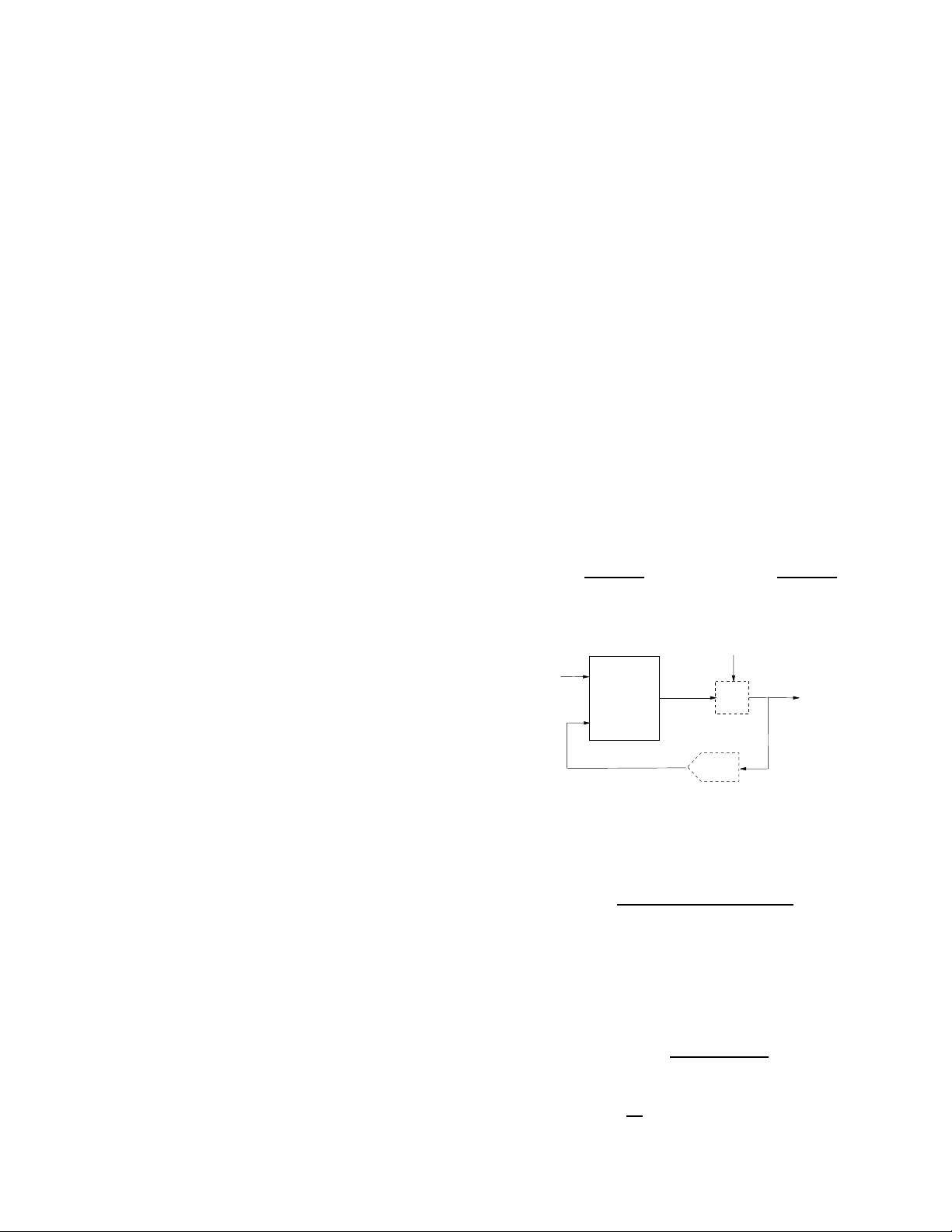

Shown in Fig. 2 is an example of second-order SDM [10]. The

STF and NTF of this modulator can be derived easily. In general, the

STF and NTF of an SDM have a rational form as follows

H(z)=

b

0

+ b

1

z + b

2

z

2

+ ... + b

m

z

m

a

0

+ a

1

z + a

2

z

2

+ ... + a

n

z

n

(3)

The coefficients can be derived as functions of the circuit parameters

in the loop-transfer architecture, such as the parameters shown in Fig.

2.

One important design metric is the SNR of an SDM. For a single-

stage SDM, by using the linear model, SNR can be calculated by the

following equations:

SNR = 10 lg

P

s

|STF(e

jω

0

)|

2

P

e,in

(4)

and

P

e,in

=

P

e

π

π/R

0

|NTF(e

jω

)|

2

dω (5)

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功