地平线机器人软硬件协同设计实践与AI效能优化

版权申诉

78 浏览量

更新于2024-07-05

收藏 8.92MB PDF 举报

“1-5+地平线在软硬件协同设计的一些实践.pdf”

这篇内容主要探讨了地平线机器人在软硬件协同设计方面的实践经验,特别是在人工智能(AI)芯片领域的创新。演讲者李建军,来自地平线编译器研发部,分享了公司在应对摩尔定律放缓背景下,如何通过软硬件结合来提升芯片效能。

首先,文章引用了John L. Hennesy和David A. Patterson的观点,认为计算机架构正进入一个新时代,语言设计、编译器创建和芯片架构师需要共同面对在不同数据流架构(DSA)之间平衡可移植性和效率的挑战。这与Chris Lattner在ASPLOS2021上的主题演讲相呼应,他强调了在软硬件协同设计时代,编译器和编程语言技术的重要性。

摩尔定律是芯片行业的一个核心概念,它预测了集成电路上可容纳的晶体管数量每两年将翻一番,从而带来性能的提升。然而,随着这一规律逐渐放缓,业界开始寻找新的性能指标。AI芯片的新摩尔定律不再单纯关注传统的Power(功耗)、Performance(性能)和Area(面积),而是转向了在保证识别精度的前提下,每单位成本的AI计算性能,如FPS(帧率)/Watt(瓦特)和FPS/$(帧率/成本)。此外,TOPS(每秒万亿次运算)/Watt和TOPS/$也被用来衡量理论峰值计算效能和实际性价比。

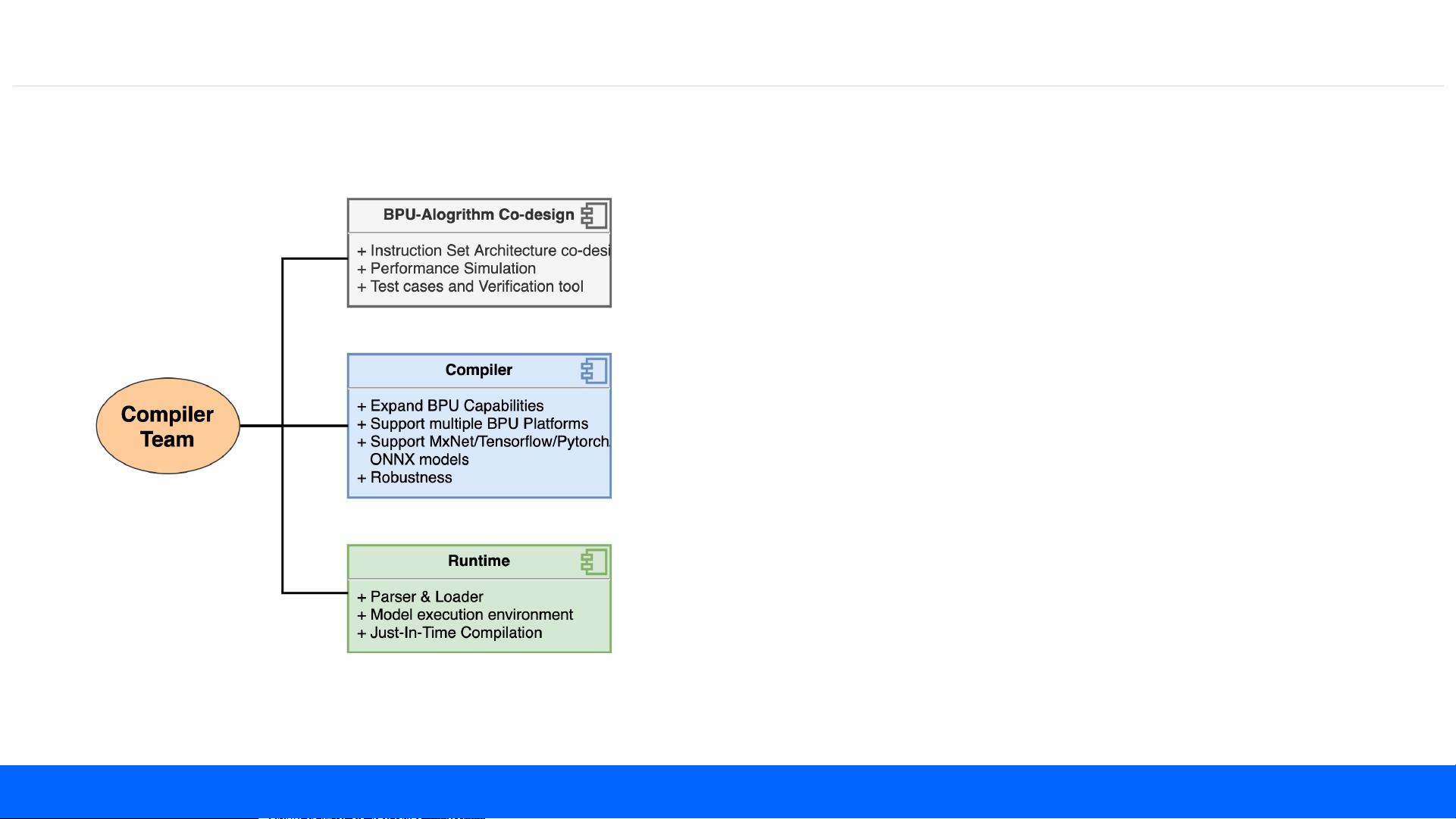

地平线机器人在编译器研发上采取了快速迭代的方法,6年内进行了4次迭代,并且与芯片研发紧密配合。在芯片架构设计初期就进行性能仿真预估,以确保软硬件优化的一致性。编译器的优化对于提高芯片的有效利用率(Utilization)至关重要,这是软硬件计算架构的目标之一。同时,AI算法效率也是算法研发人员关注的重点,通过提高FPS/TOPS比率,可以实现更高效的AI计算。

地平线机器人通过软硬件协同设计,不断优化编译器和芯片架构,以适应AI时代对芯片性能的新要求,追求在功耗、性能和成本之间找到最佳平衡点,以实现极致的AI效能。这种实践策略不仅展示了公司在AI领域的技术领先地位,也为整个行业提供了有价值的参考。

2022-07-06 上传

2019-12-01 上传

2023-06-09 上传

2023-04-17 上传

2023-12-16 上传

2023-05-29 上传

2023-10-22 上传

2023-05-28 上传

普通网友

- 粉丝: 12w+

- 资源: 9195

最新资源

- 掌握压缩文件管理:2工作.zip文件使用指南

- 易语言动态版置入代码技术解析

- C语言编程实现电脑系统测试工具开发

- Wireshark 64位:全面网络协议分析器,支持Unix和Windows

- QtSingleApplication: 确保单一实例运行的高效库

- 深入了解Go语言的解析器组合器PARC

- Apycula包安装与使用指南

- AkerAutoSetup安装包使用指南

- Arduino Due实现VR耳机的设计与编程

- DependencySwizzler: Xamarin iOS 库实现故事板 UIViewControllers 依赖注入

- Apycula包发布说明与下载指南

- 创建可拖动交互式图表界面的ampersand-touch-charts

- CMake项目入门:创建简单的C++项目

- AksharaJaana-*.*.*.*安装包说明与下载

- Arduino天气时钟项目:源代码及DHT22库文件解析

- MediaPlayer_server:控制媒体播放器的高级服务器