DC综合操作流程详解与关键步骤

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

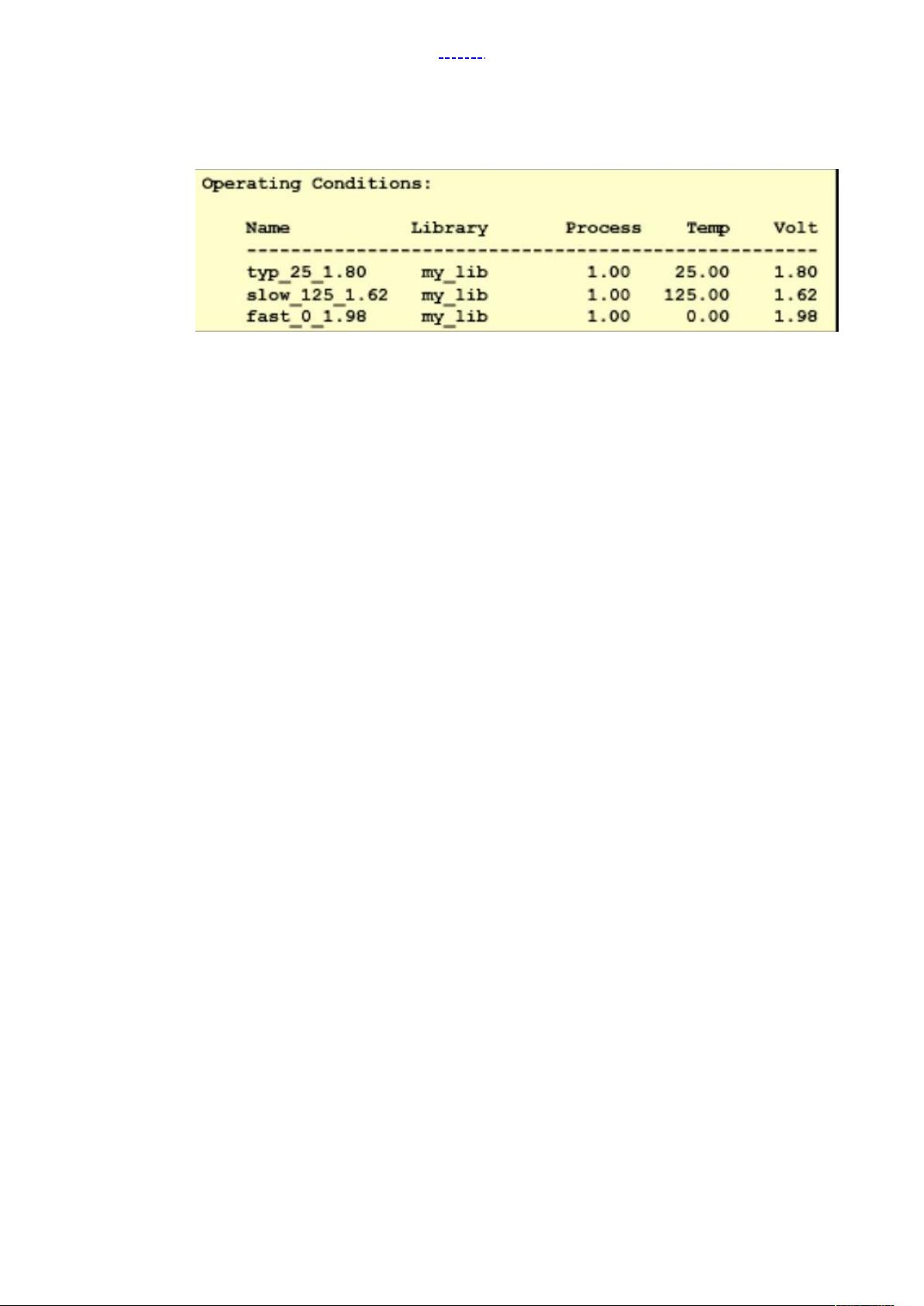

"DC综合操作流程的详细步骤及关键设置" 在计算机硬件设计领域,DC(Design Compiler)是一款广泛使用的逻辑综合工具,它能够将高级语言(如Verilog或VHDL)描述的设计转换成门级网表,为后续的布局布线等步骤做准备。以下是对"DC综合操作流程_设置流程.doc"中描述的知识点的详细解释: 1. **库的设置**: 库设置是DC综合的第一步,包括设定库路径、标准单元库、IO库等。这一步确保设计中使用的每个元件都能被正确识别。检查`.synopsys_dc.setup`文件与软件应用设置的一致性至关重要,以确保库配置无误。 2. **设计的读入**: 使用`read`或`analyze + elaborate`命令读入设计。`analyze`会解析HDL源代码并生成中间文件,而`elaborate`则基于这些中间文件构建设计的逻辑结构。 3. **环境属性的设置**: - **set_operating_conditions**:设置工作条件,如温度、电压和工艺条件,通常有最佳、典型和最差三种情况。 - **set_wire_load_model and set_wire_load_mode**:设定线负载模型和模式,用于模拟布线影响,确保设计在实际布线后的性能。 - **setload** 和 **set_drive/set_driving_cell**:设定负载和驱动单元,影响信号的传播速度和质量。 4. **设计规则约束**: - **set_max_transtion**:限制信号的最大转变速率,防止过度振荡。 - **set_max_capacitance**:设定最大电容限制,防止过度负载。 - **set_max_fanout**:设置最大扇出数,控制单个门驱动的其他门的数量。 5. **优化约束**: - **create_clock**:定义时钟信号。 - **set_clock_uncertainty**:设置时钟不确定性,考虑时钟抖动和延迟。 - **set_clock_latency**:设定时钟延迟。 - **set_input_delay/output_delay**:设置输入/输出延迟。 - **set_false_path**:标记非关键路径,避免不必要的优化。 - **set_multicycle_path**:定义多周期路径,允许某些路径在多个时钟周期内完成。 - **set_max_delay/set_min_delay**:设定最大和最小延迟目标。 - **set_max_area**:控制设计的面积,平衡速度和面积。 6. **注意事项**: - 在前端设计中通常不进行hold_time约束,这些约束通常在后端处理。 通过以上步骤,DC能够根据设计需求和约束进行逻辑综合,生成满足性能和面积目标的门级网表。在执行这些步骤时,还需要关注DC的输出信息,以便及时调整参数和约束,确保设计的正确性和优化效果。在实际操作中,应结合图形界面和命令行工具,灵活调整设置以达到最佳设计效果。

剩余20页未读,继续阅读

- 粉丝: 0

- 资源: 5万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 构建Cadence PSpice仿真模型库教程

- VMware 10.0安装指南:步骤详解与网络、文件共享解决方案

- 中国互联网20周年必读:影响行业的100本经典书籍

- SQL Server 2000 Analysis Services的经典MDX查询示例

- VC6.0 MFC操作Excel教程:亲测Win7下的应用与保存技巧

- 使用Python NetworkX处理网络图

- 科技驱动:计算机控制技术的革新与应用

- MF-1型机器人硬件与robobasic编程详解

- ADC性能指标解析:超越位数、SNR和谐波

- 通用示波器改造为逻辑分析仪:0-1字符显示与电路设计

- C++实现TCP控制台客户端

- SOA架构下ESB在卷烟厂的信息整合与决策支持

- 三维人脸识别:技术进展与应用解析

- 单张人脸图像的眼镜边框自动去除方法

- C语言绘制图形:余弦曲线与正弦函数示例

- Matlab 文件操作入门:fopen、fclose、fprintf、fscanf 等函数使用详解

信息提交成功

信息提交成功