Vivado Design Suite: BlockMemory Generator v8.3 - IP Guide & Des...

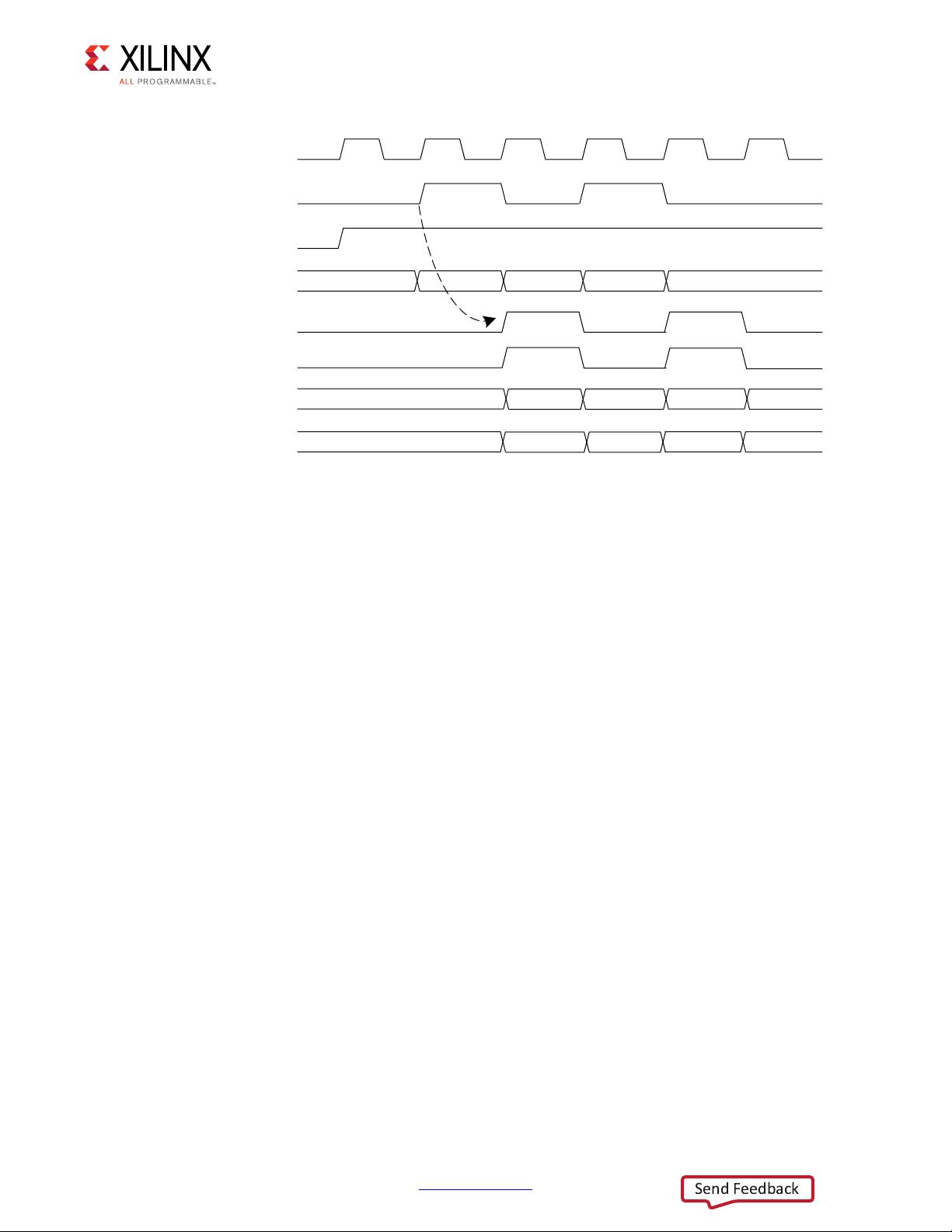

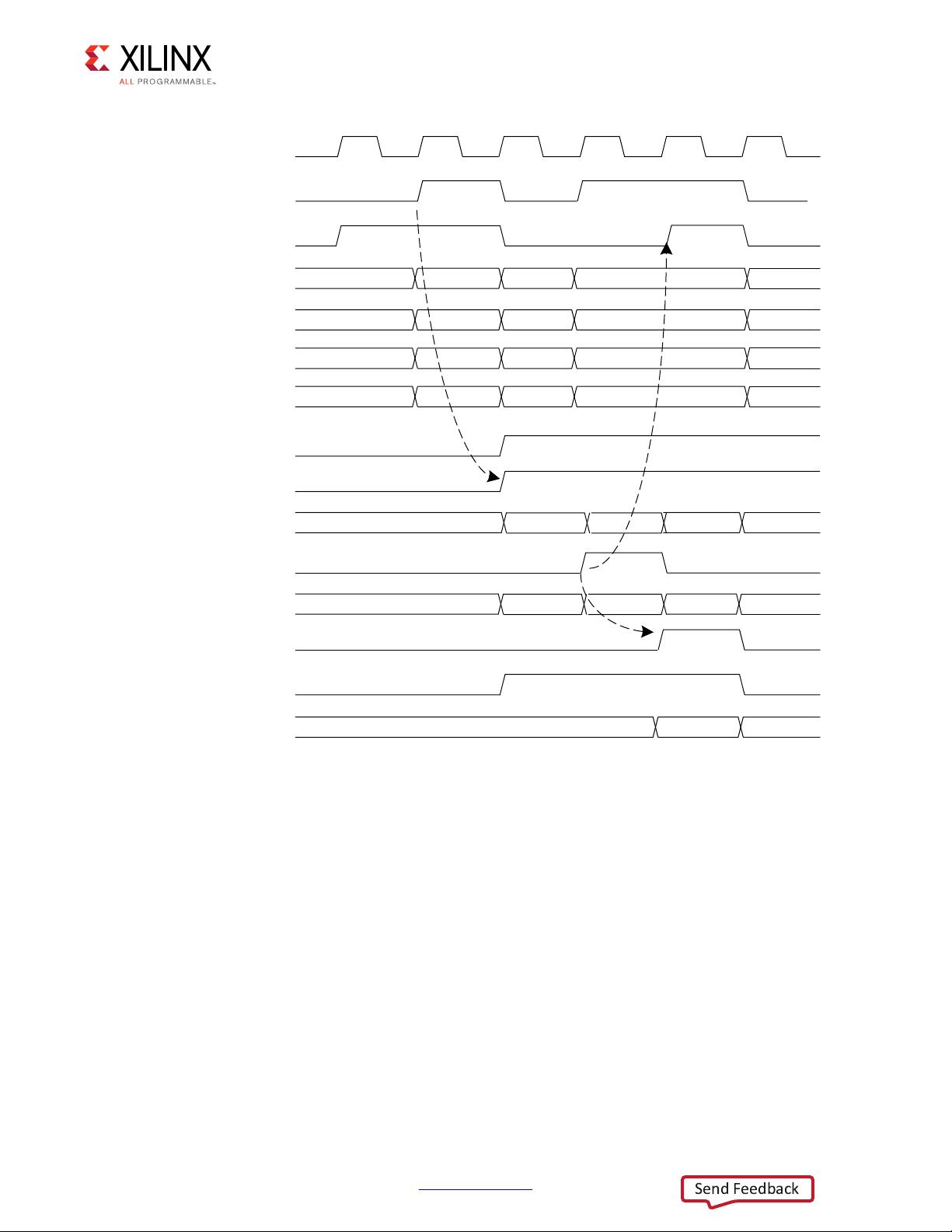

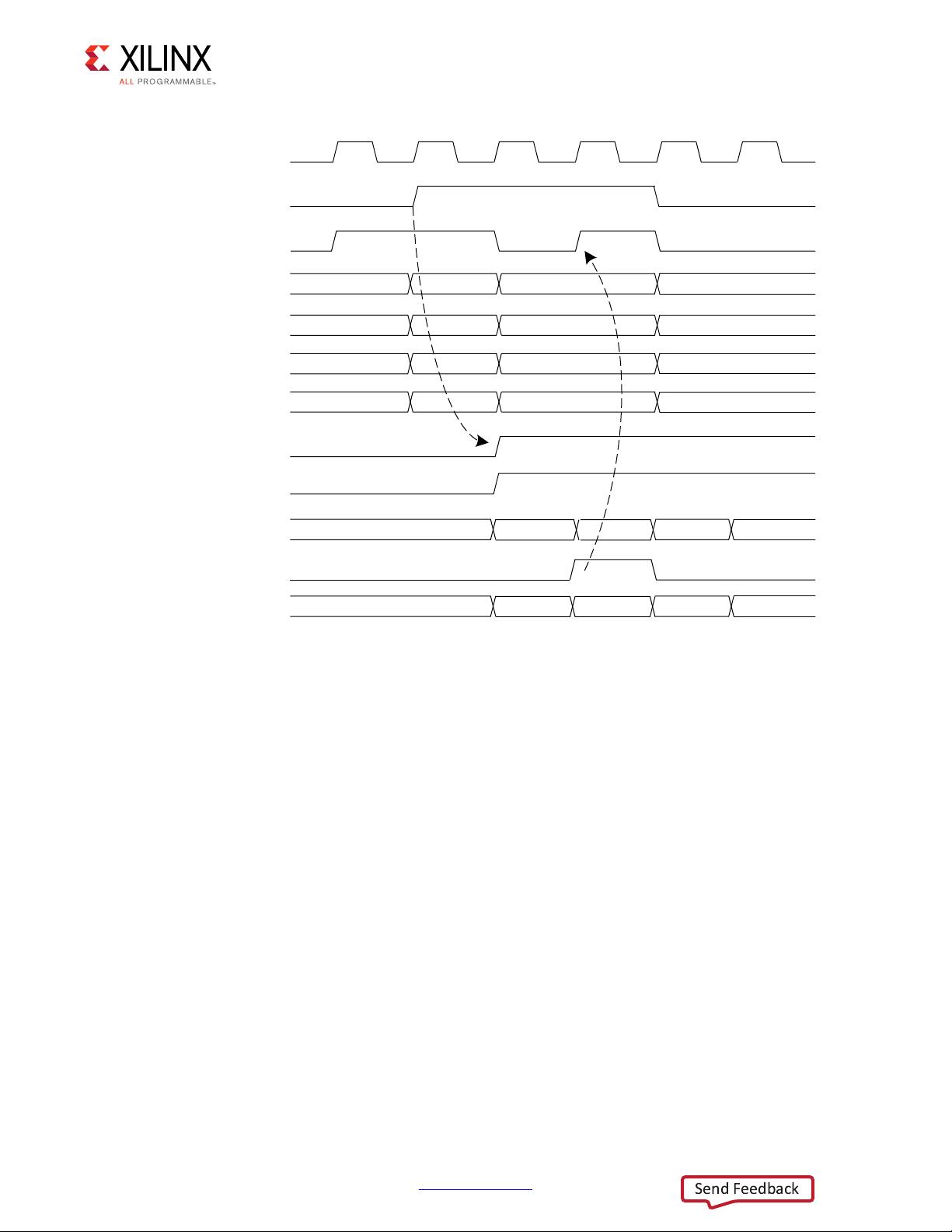

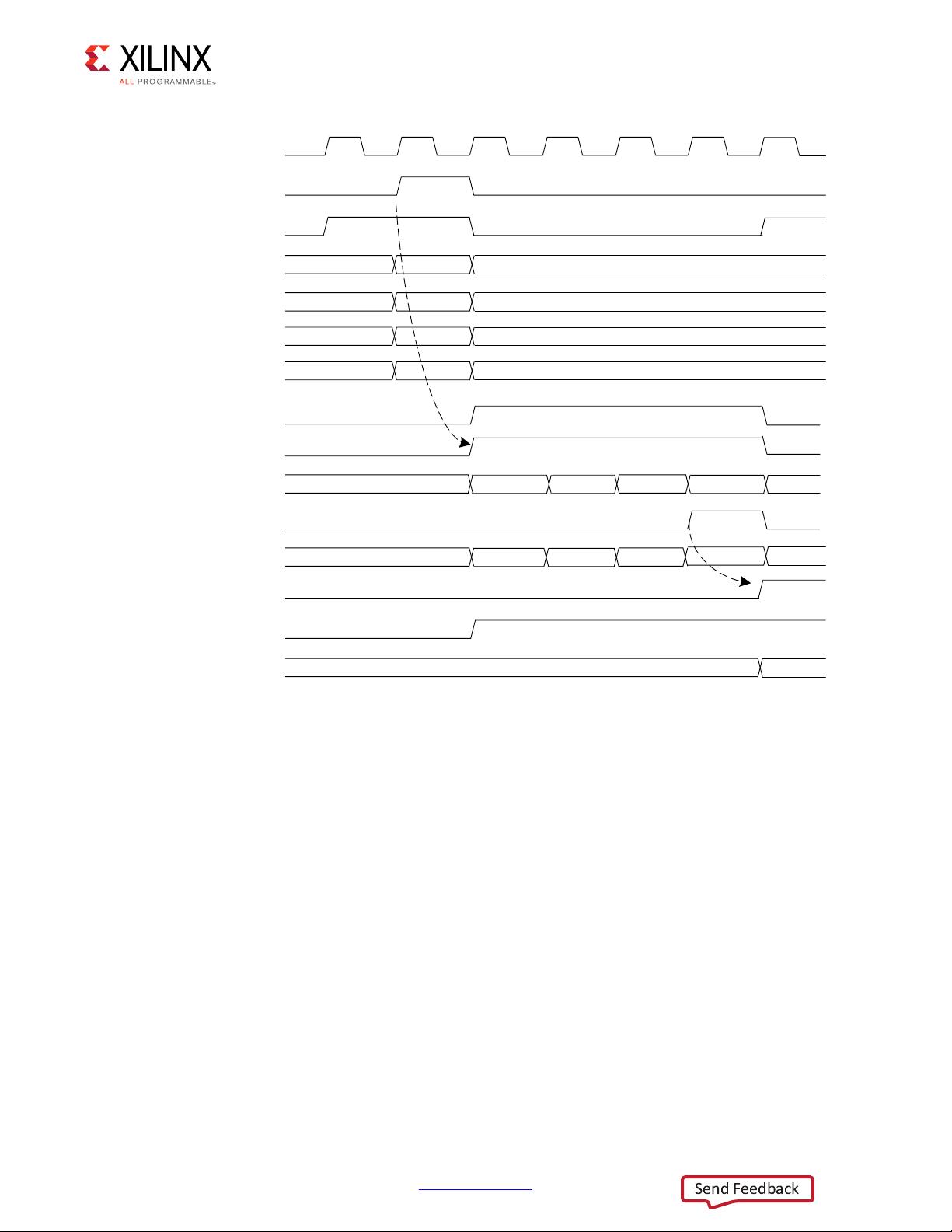

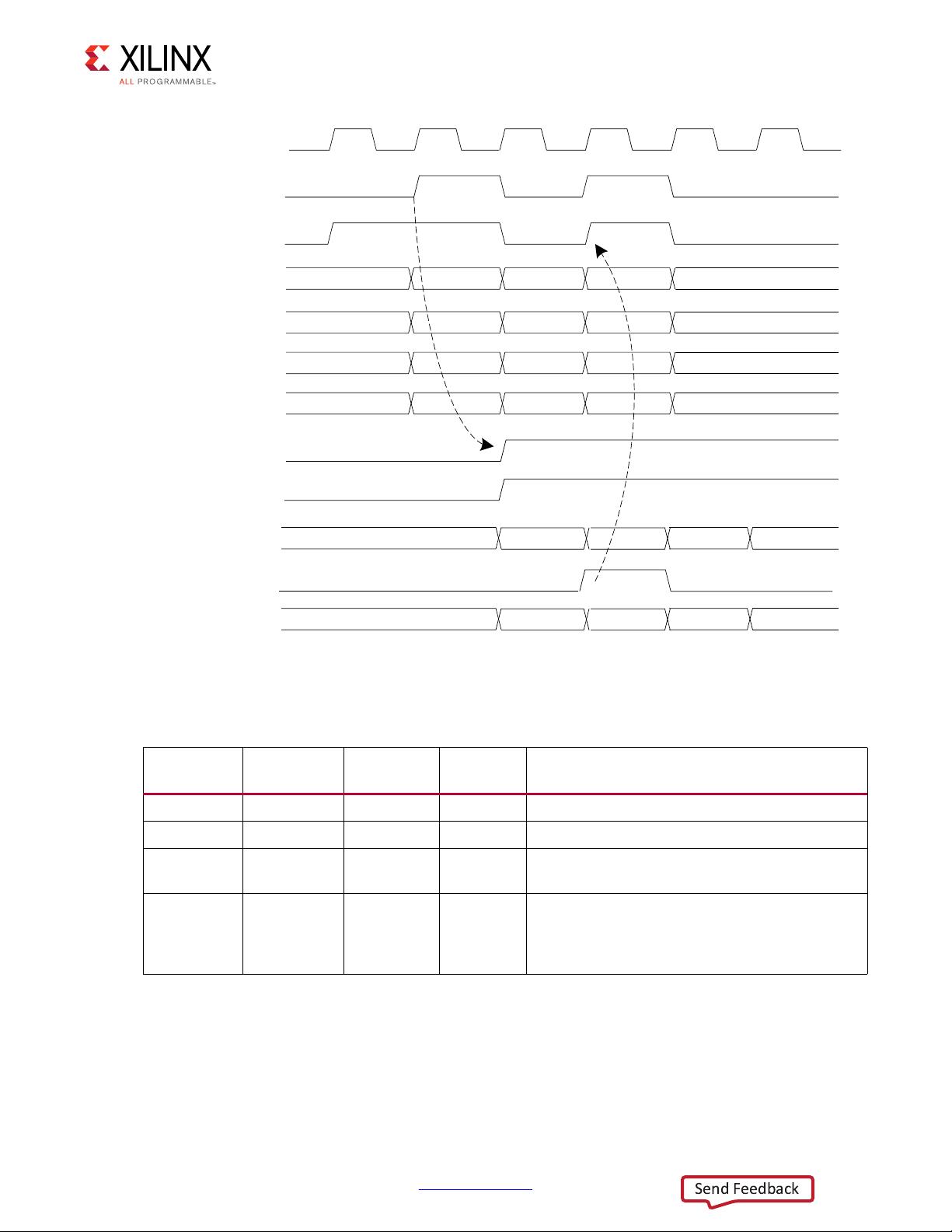

《RapidIP Block Memory Generator v8.3设计指南》是一份由Xilinx公司发布的LogiCORE IP产品手册,专注于BlockMemory Generator这款核心IP的详细设计和使用。该文档适用于Vivado Design Suite,特别是在v8.3版本下,旨在帮助用户理解和利用Block Memory Generator在各种应用中的优势。 **1. IP Facts**: - BlockMemory Generator提供了两种主要接口:Native Block Memory Generator和AXI4 Interface,支持高效的内存访问和配置。Native接口提供原生的内存管理功能,而AXI4则提供了更广泛的应用兼容性,适用于SoC设计中的系统级通信。 **2. Overview (概述)**: - 本章概述了Block Memory Generator的主要特性和优势,包括其性能、资源利用率以及针对不同应用场景的灵活性。此外,还提到了许可证和订购信息,帮助用户了解使用该IP的法律条款。 **3. Product Specification (产品规格)**: - 这一部分详细介绍了Block Memory Generator的性能指标,如吞吐量、带宽和时延等。资源占用方面,包括逻辑资源、存储器资源和I/O引脚,以便设计师在设计初期评估其对整体设计的影响。 **4. Designing with the Core (核心设计)**: - 设计流程指南包括通用设计原则、UltraScale架构设备特性(如多核支持、低功耗特性)、时钟管理和复位管理等内容,确保用户能充分利用硬件资源并遵循最佳实践。 **5. Design Flow Steps (设计流程步骤)**: - 从定制和生成核心IP开始,然后是约束设置,包括设置设计规则和目标平台。接下来介绍如何进行模拟验证、综合和实施,确保设计的正确性和性能。 **6. Detailed Example Design (详细示例设计)**: - 提供了使用Native和AXI4接口的详细设计例子,有助于读者通过实践理解如何在实际项目中集成和使用Block Memory Generator。 **7. Test Bench (测试台)**: - 对于每个接口类型,都给出了相应的测试台,用于验证IP的功能和性能。这部分包含错误消息和警告处理,帮助开发者调试和优化设计。 **8. Verification, Compliance, and Interoperability (验证、合规性和互操作性)**: - 附录A深入讨论了模拟验证方法,确保IP符合行业标准和Xilinx的规定,以及与其他IP的兼容性。 **9. Migrating and Upgrading (迁移和升级)**: - 在升级指南中,阐述了如何从旧版本的Vivado Design Suite平稳地迁移到v8.3版本,以及如何处理新版本带来的可能变化。 《pg058-blk-mem-gen.pdf》是Xilinx为Block Memory Generator提供的详尽设计文档,涵盖了IP的各个方面,从基本概念到实际设计和验证流程,为设计者提供了全面的支持。无论是初次使用者还是经验丰富的工程师,都能从中获得有价值的指导。

剩余128页未读,继续阅读

- 粉丝: 10

- 资源: 185

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 京瓷TASKalfa系列维修手册:安全与操作指南

- 小波变换在视频压缩中的应用

- Microsoft OfficeXP详解:WordXP、ExcelXP和PowerPointXP

- 雀巢在线媒介投放策划:门户网站与广告效果分析

- 用友NC-V56供应链功能升级详解(84页)

- 计算机病毒与防御策略探索

- 企业网NAT技术实践:2022年部署互联网出口策略

- 软件测试面试必备:概念、原则与常见问题解析

- 2022年Windows IIS服务器内外网配置详解与Serv-U FTP服务器安装

- 中国联通:企业级ICT转型与创新实践

- C#图形图像编程深入解析:GDI+与多媒体应用

- Xilinx AXI Interconnect v2.1用户指南

- DIY编程电缆全攻略:接口类型与自制指南

- 电脑维护与硬盘数据恢复指南

- 计算机网络技术专业剖析:人才培养与改革

- 量化多因子指数增强策略:微观视角的实证分析

信息提交成功

信息提交成功