© Copyright 2018 Xilinx

Xilinx Answer 71435 – Driver and XDMA IP Debug Guide 6

o Check for data integrity

o Report pass or fail

load_driver.sh: loads driver

perform_hwcount.sh: for hardware performance

Example Application

(Xilinx Answer 65444) provides the following applications:

dma_to_device

o [AXI-MM] dma_to_device –d /dev/xdma0_h2c_0 –f infile.bin –s 4096 –a 1000 –o 24

o [AXI-ST] dma_to_device –d /dev/xdma0_h2c_0 –f infile.bin –s 4096 –o 24

dma_from_device

o [AXI-MM] dma_from_device –d /dev/xdma0_c2h_0 –f outfile.bin –s 4096 –a 1000 –o 24

o [AXI-ST] dma_from_device –d /dev/xdma0_c2h_0 –f outfile.bin –s 4096 –o 24

reg_rw

linux utility ‘dd’ can also be used for the DMA. Linux ‘dd’ is a basic Linux utility to copy. It also gives bandwidth

information

o dd if=/dev/zero of=/dev/xdma0_h2c_0 bs=4096 count=1

Will transfer 4Kbytes from Host to Card

o dd of=/dev/null if=/dev/xdma0_c2h_0 bs=4096 count=1

• Will transfer 4Kbytes from Card to HostDMA Transfer flow for H2C and C2H

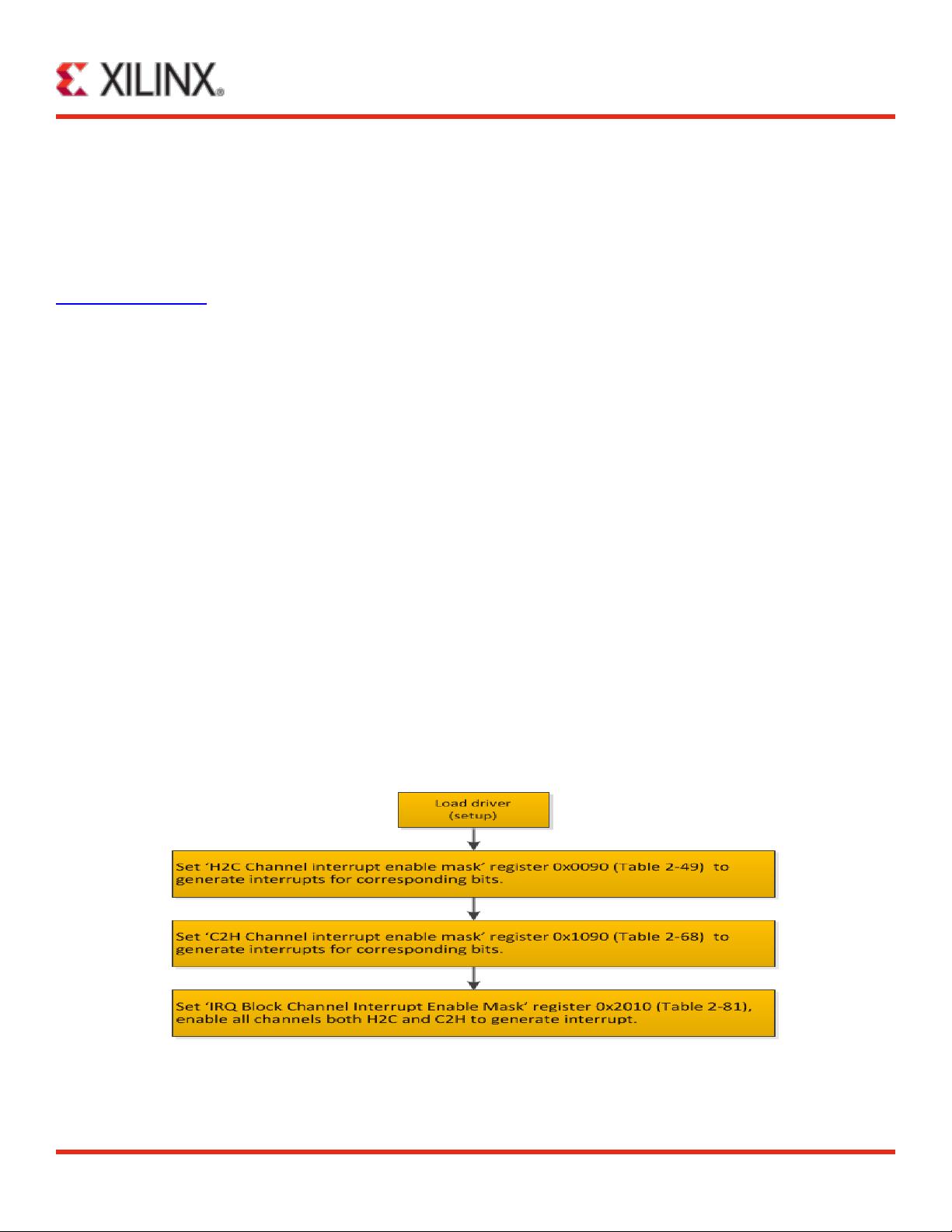

Register Programming during ‘driver load’ process