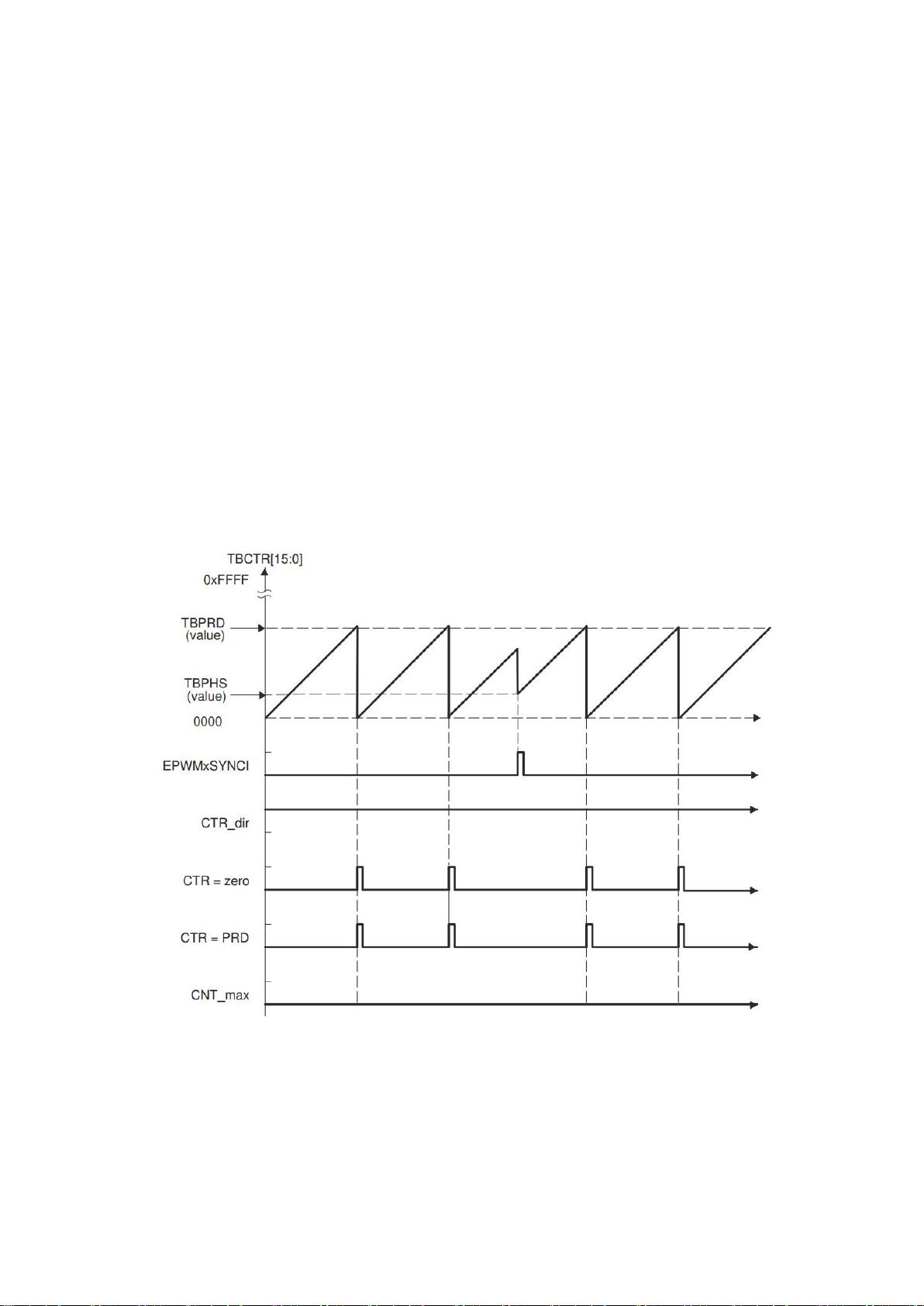

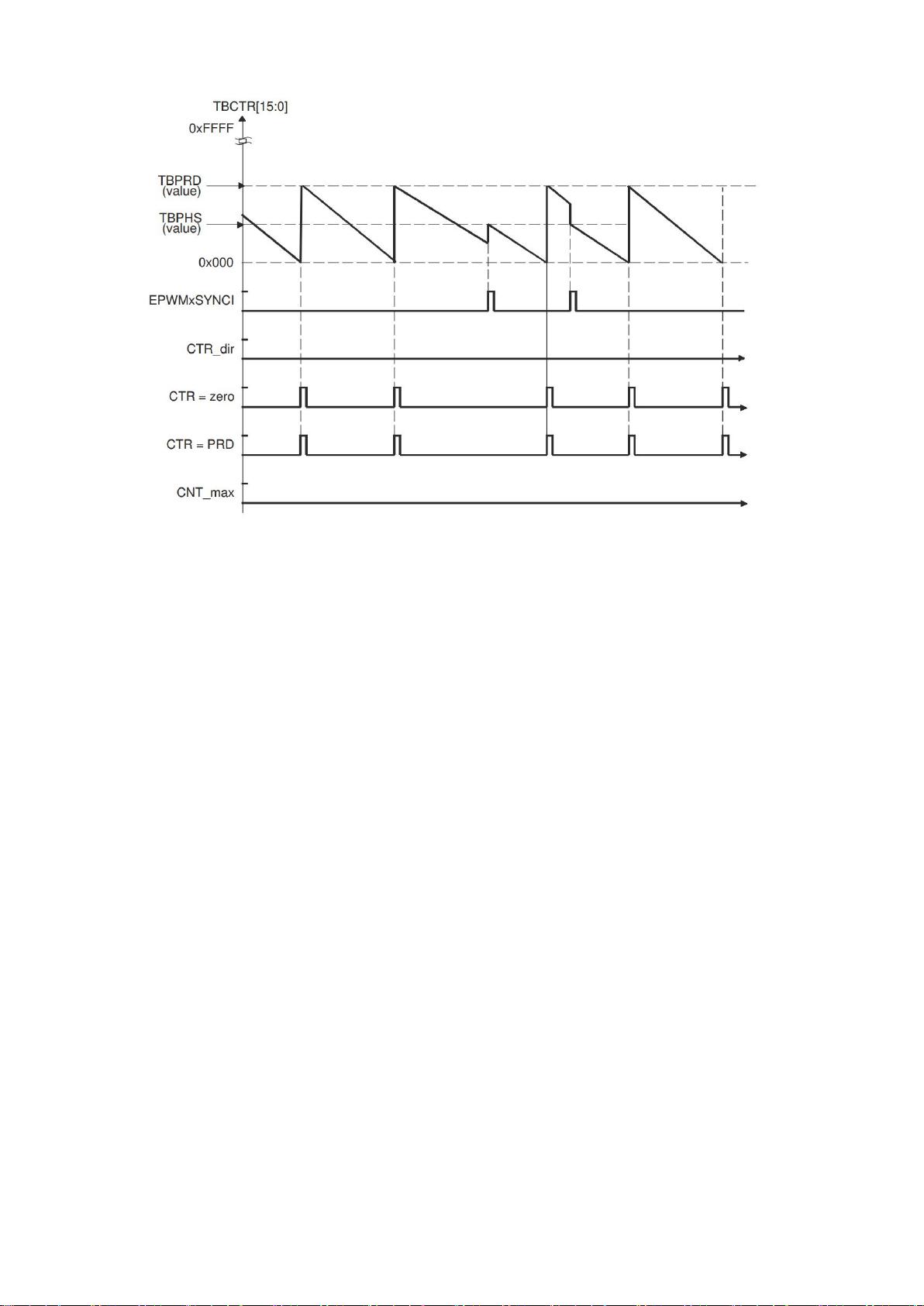

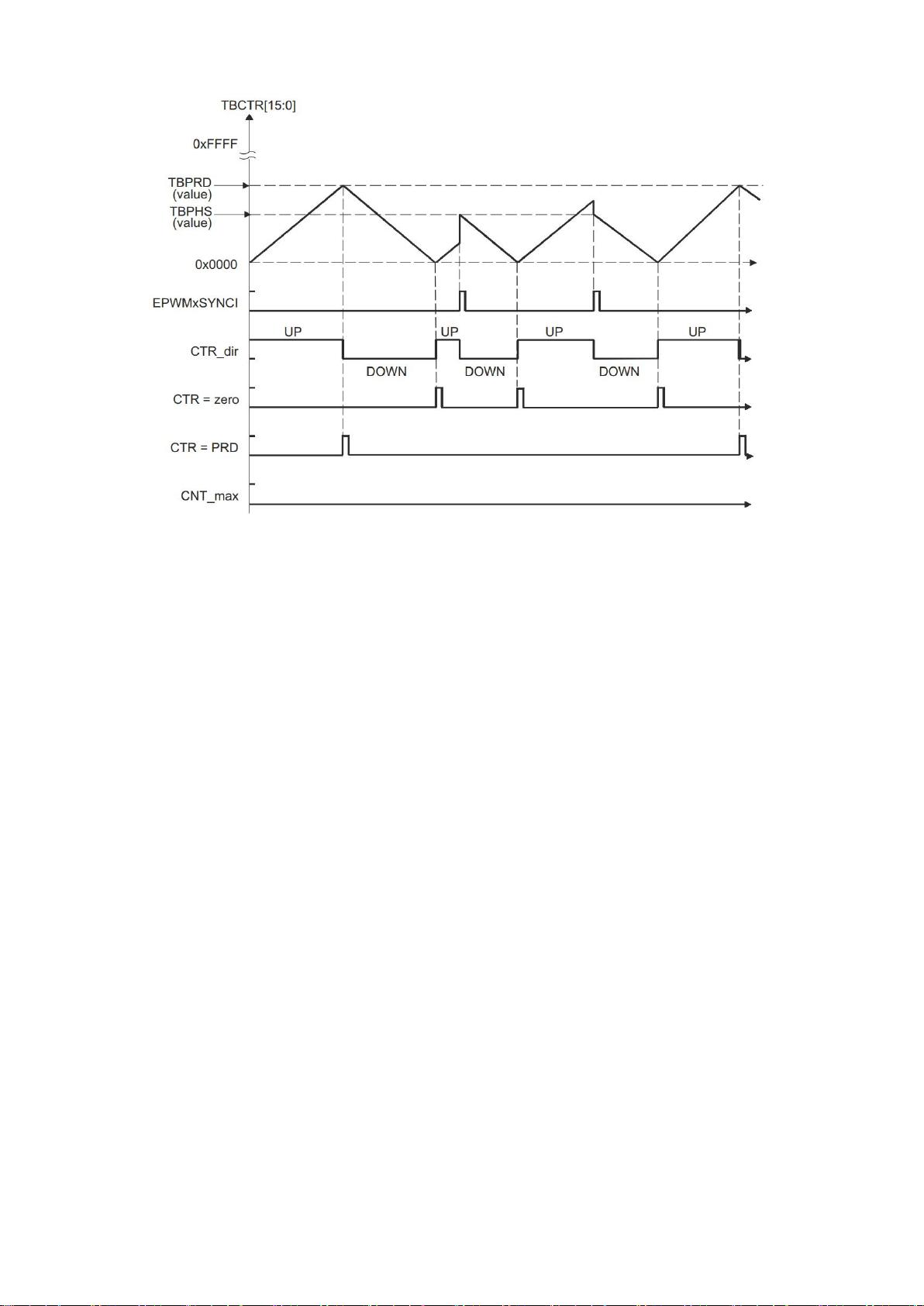

每个 ePWM 模块可配置为使用或忽略同步输入。如果设置了 TBCTL[PHSEN]位,则当出现以下情况之一时,ePWM

模块的时基计数器(TBCTR)将自动加载相位寄存器(TBPHS)内容:

• EPWMxSYNCI:同步输入脉冲:

当检测到输入同步脉冲时,相位寄存器的值加载到计数器寄存器中(TBPHS → TBCTR)。此操作发生在下一

个有效的时基时钟(TBCLK)边缘。

从内部主模块到从模块的延迟如下所示:

–if(TBCLK=EPWMCLK):2 个 EPWMCLK

–if(TBCLK<EPWMCLK):1 x TBCLK

• 软件强制同步脉冲:

将 1 写入 TBCTL[SWFSYNC]控制位将调用软件强制同步。该脉冲与同步输入信号进行 OR 运算,因此与

EPWMxSYNCI 上的脉冲具有相同的效果。

•数字比较事件同步脉冲:

DCAEVT1 和 DCBEVT1 数字比较事件可配置为生成与 EPWMxSYNCI 具有相同影响的同步脉冲。

注意

如果 EPWMxSYNCI 信号保持高电平,则同步不会持续发生。EPWMxSYNCI 处于上升沿激活状态。

此功能使 ePWM 模块能够自动与另一个 ePWM 模块的时基同步。超前或滞后相位控制可以添加到不同 ePWM 模块生

成的波形中,以使其同步。在上下计数模式下,TBCTL[PSHDIR]位在同步事件发生后立即配置时基计数器的方向,

新方向独立于同步事件之前的方向。在向上计数或向下计数模式下忽略 PHSDIR 位。示例见图 18-8 至图 18-11。

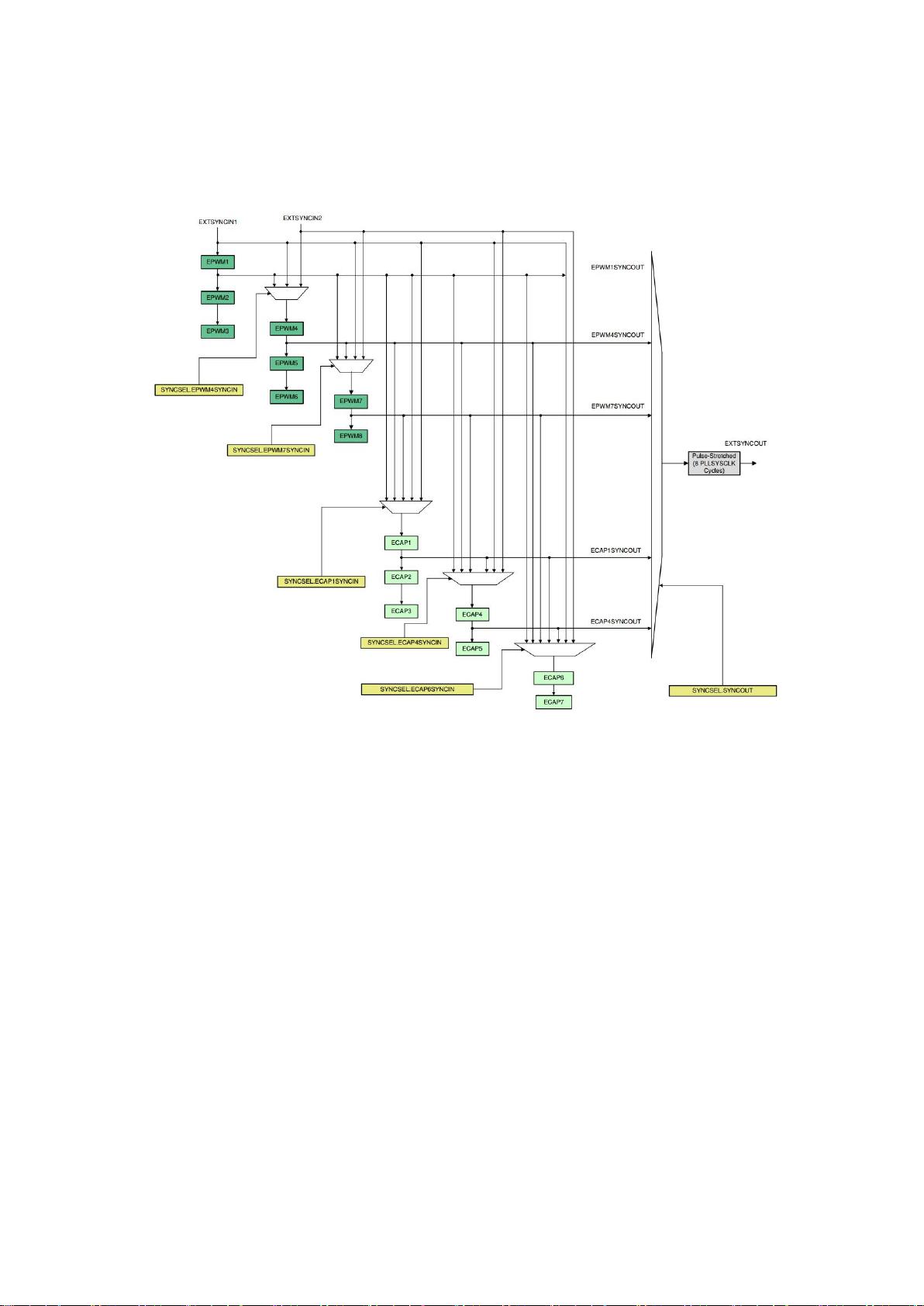

清除 TBCTL[PHSEN]位将 ePWM 配置为忽略同步输入脉冲。同步脉冲仍可通过 EPWMxSYNCO,并用于同步其他 ePWM

模块。通过这种方式,您可以设置主时基(例如,ePWM1),并且下游模块(ePWM2-ePWMx)可以选择与主模块

同步运行。有关同步策略的更多详细信息,请参见第 18.13 节。

18.4.4 多个 ePWM 模块的时基时钟锁相

TBCLKSYNC 位可用于全局同步设备上所有启用 ePWM 模块的时基时钟。该位是设备时钟启用寄存器的一部分,在

本手册的“系统控制和中断”部分进行了描述。当 TBCLKSYNC=0 时,所有 ePWM 模块的时基时钟停止(默认)。

当 TBCLKSYNC=1 时,所有 ePWM 时基时钟均以 TBCLK 的上升沿对齐的方式启动。

对于完全同步的 TBCLK,每个 ePWM 模块的 TBCTL 寄存器中的预分频器位必须设置相同。启用 ePWM 时钟的正确

程序如下:

1.启用各个 ePWM 模块时钟。这在

系统控制和中断

章节中进行了描述。

2.设置 TBCLKSYNC=0。这将停止任何启用的 ePWM 模块内的时基时钟。

3.配置预分频器值和所需的 ePWM 模式。

4.设置 TBCLKSYNC=1。

18.4.5 ePWM 模块之间对 TBPRD 和 CMPx 寄存器的同时写入

对于变频应用,需要在 ePWM 模块之间同时写入 TBPRD 和 CMPx 寄存器。这可以防止在 ePWM 模块之间更新所有寄

存器之前,CTR=0 或 CTR=PRD 脉冲强制这些寄存器的影子寄存器加载到活动状态(导致一些寄存器从新影子寄

存器值加载,而另一些寄存器从旧影子寄存器值加载)。为了支持