RocketChip:可高度参数化的SoC生成器

需积分: 2 155 浏览量

更新于2024-07-16

收藏 1.7MB PDF 举报

"HC31_T6_Rocket.pdf"

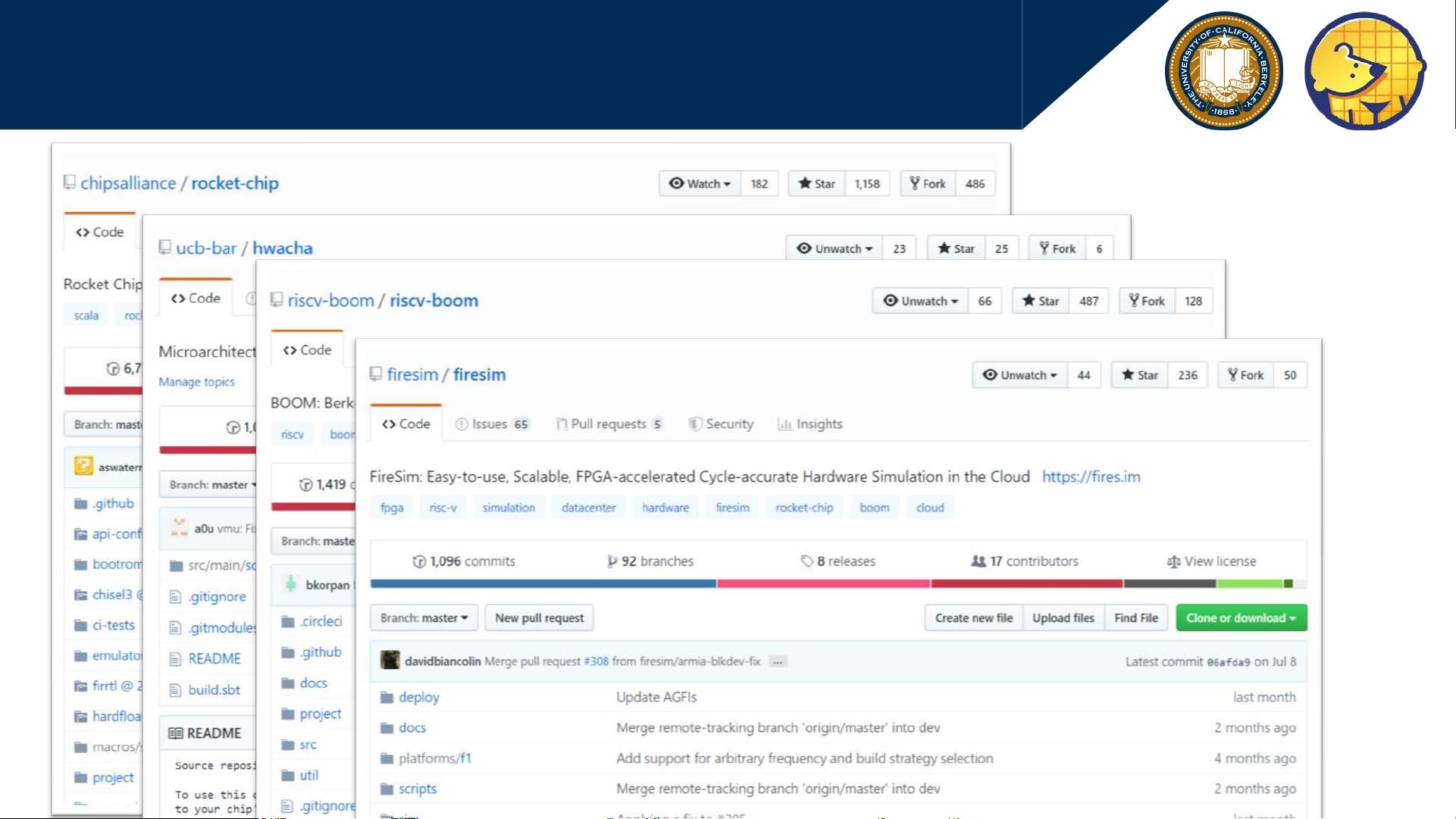

本文档介绍的是RocketChip项目,它是基于RISC-V架构的一个高度可配置的系统级芯片(SoC)生成器,由Howard Mao和Jerry Zhao在加州大学伯克利分校的架构研究团队开发,并在HotChips 2019会议上进行了展示。RocketChip的核心特性是其灵活性和可扩展性,使得用户能够根据需求替换默认的Rocket核心,添加自定义的协处理器,或者整合自己的SoC IP到未核心部分。

RocketChip包含一个库,拥有各种可重用的SoC组件,如内存协议转换器、仲裁器、跨总线生成器、时钟跨越功能和异步队列等。这些组件对于构建复杂的SoC设计至关重要,因为它们解决了不同模块间的通信和同步问题。此外,RocketChip是最大的开源Chisel代码库,Chisel是一种基于Scala的硬件构造领域特定语言(DSL)。使用Scala作为基础,Chisel允许以更编程化的方式来描述实时逻辑,同时利用面向对象和函数式编程的特性,使得复杂的参数化生成器的构建成为可能。

Chisel并不是将Scala直接转换为门级或高层次综合(HLS)的工具,而是通过提供一种更高级别的抽象来描述硬件设计。例如,以下的Chisel代码片段展示了如何使用Chisel的`TreeAdderPipeline`类来创建一个带有n个阶段的流水线树形加法器:

```scala

class TreeAdderPipeline(n: Int) extends Module {

val io = IO(new Bundle {

val in = Input(Vec(n, UInt(32.W)))

val out = Output(UInt(32.W))

})

val nStages = log2Ceil(n)

// ...

}

```

在这个例子中,`nStages`计算了树形加法器所需的阶段数,`in`和`out`分别表示输入向量和输出结果。通过这样的编程方式,设计者可以方便地创建并调整硬件结构,而无需深入到低级别的门级描述。

RocketChip的广泛应用体现在工业界和学术界,例如SiFive的Freedom E310 SoC以及UCB Hurricane-1项目都采用了这一技术。并且,由于其开源性质和强大的社区支持,包括SiFive、Chips Alliance和Berkeley在内的多个组织都在维护和推动RocketChip的发展。

RocketChip是一个强大的工具,它为RISC-V架构的SoC设计提供了灵活的框架,通过Chisel语言,设计者可以高效地构建和定制满足特定需求的硬件系统。这对于研究、教育和工业应用来说都具有很高的价值。

2024-03-29 上传

2021-04-30 上传

2023-04-25 上传

2023-04-25 上传

2023-06-10 上传

2023-03-28 上传

2023-07-27 上传

2023-06-08 上传

iiiiiiicer

- 粉丝: 1

- 资源: 10

最新资源

- AirKiss技术详解:无线传递信息与智能家居连接

- Hibernate主键生成策略详解

- 操作系统实验:位示图法管理磁盘空闲空间

- JSON详解:数据交换的主流格式

- Win7安装Ubuntu双系统详细指南

- FPGA内部结构与工作原理探索

- 信用评分模型解析:WOE、IV与ROC

- 使用LVS+Keepalived构建高可用负载均衡集群

- 微信小程序驱动餐饮与服装业创新转型:便捷管理与低成本优势

- 机器学习入门指南:从基础到进阶

- 解决Win7 IIS配置错误500.22与0x80070032

- SQL-DFS:优化HDFS小文件存储的解决方案

- Hadoop、Hbase、Spark环境部署与主机配置详解

- Kisso:加密会话Cookie实现的单点登录SSO

- OpenCV读取与拼接多幅图像教程

- QT实战:轻松生成与解析JSON数据