没有合适的资源?快使用搜索试试~ 我知道了~

首页AK4499 -DAC 解码器

AK4499 -DAC 解码器

需积分: 32 17 下载量 10 浏览量

更新于2023-03-03

评论

收藏 1.7MB PDF 举报

AK4499是采用新开发技术的32位4通道开关电阻DAC,具有业界领先的低失真和低噪声特性。 它最大对应一个768kHz的PCM输入和一个DSD512输入,适用于回放在网络音频和USB-DAC音频系统中变得越来越普遍的高分辨率音频源。 此外,它能够支持各种信号并实现低带外噪声。 AK4499具有六种类型的32位数字滤波器,可在广泛的应用中实现简单而灵活的声音再现。 The AK4499 is a 32-bit 4ch Switched Resistor DAC which adopts newly developed technology,achieving the industry’s leading level low distortion and low noise characteristics. It corresponds to a 768kHz PCM input and an DSD512 input at maximum, suitable for playback of high resolution audio sources that are becoming

资源详情

资源评论

资源推荐

[AK4499]

019001308-E-00 2019/02

- 1 -

1. General Description

The AK4499 is a 32-bit 4ch Switched Resistor DAC which adopts newly developed technology,

achieving the industry’s leading level low distortion and low noise characteristics. It corresponds to a

768kHz PCM input and an DSD512 input at maximum, suitable for playback of high resolution audio

sources that are becoming widespread in Network Audio and USB-DACs Audio systems. In addition, it

is capable of supporting a wide range of signals and achieving low out-of-band noise. The AK4499 has

six types of 32-bit digital filters, realizing simple and flexible sound reproduction in wide range of

applications.

2. Features

• 4-ch Switched Resistor DAC

• THD+N: -124 dB

• Dynamic Range, S/N: 140 dB (Mono), 137 dB (Stereo), 134 dB (4ch)

• 128x Over Sampling

• Sampling Rate: 8 kHz to 768 kHz

• 32-bit 8x Digital Filter

Short Delay Sharp Roll-off, GD = 6.0/fs

Short Delay Slow Roll-off, GD = 5.0/fs

Sharp Roll-off

Slow Roll-off

Super Slow Roll-off

Low Dispersion Short Delay Filter

• DSD64, DSD128, DSD256, DSD512 Input Support

Filter1 (fc = 37 kHz, DSD64 mode)

Filter2 (fc = 65 kHz, DSD64 mode)

• Digital De-emphasis for 32, 44.1 and 48kHz sampling

• Soft Mute

• Digital Attenuator (0 dB to -127 dB, 0.5 dB step + mute)

• Mono Mode

• External Digital Filter Interface (EXDF Mode)

• PCM/DSD, EXDF/DSD Mode Automatic Mode Switching Function

• Audio I/F Format

- MSB Justified

- LSB Justified

- I

2

S

- DSD

- TDM

• Daisy Chain

• Master Clock

- fs = 8 kHz to 32 kHz : 256fs, 384fs, 512fs, 768fs, 1152fs

- fs = 32 kHz to 54 kHz : 256fs, 384fs, 512fs, 768fs

- fs = 54 kHz to 108 kHz : 256fs, 384fs

- fs = 108 kHz to 216 kHz : 128fs, 192fs

- fs = 384 kHz : 32fs, 48fs, 64fs, 96fs

- fs = 768 kHz :16fs, 32fs, 48fs, 64fs

• Register Control Mode with 3-wire Serial or I

2

C interface

Premium Switched Resistor 4ch DAC

AK4499

[AK4499]

019001308-E-00 2019/02

- 2 -

• Pin Control Mode

• Power Supply:

Internal LDO (LDOE pin = “H”); TVDD = 3.0 3.6 V, AVDD = 4.75 5.25 V,

VDDL1/R1/L2/R2 = 4.75 5.25 V

External Supply (LDOE pin = “L”); TVDD = 1.7 3.6 V, DVDD = 1.7 to 1.98 V,

AVDD = 4.75 5.25 V, VDDL1/R1/L2/R2 = 4.75 5.25 V

• Operational Temperature: -40 to 85 C

• Digital Input Level: CMOS

• Package: 128-pin HTQFP

[AK4499]

019001308-E-00 2019/02

- 3 -

3. Table of Contents

1. General Description ........................................................................................................................ 1

2. Features .......................................................................................................................................... 1

3. Table of Contents ............................................................................................................................ 3

4. Block Diagram and Functions ......................................................................................................... 4

4.1. Block Diagram ................................................................................................................................. 4

4.2. Functions ......................................................................................................................................... 5

5. Pin Configurations and Functions ................................................................................................... 6

5.1. Pin Configurations ........................................................................................................................... 6

5.2. Functions ......................................................................................................................................... 7

5.3. Handling of Unused Pin .................................................................................................................. 11

6. Absolute Maximum Ratings .......................................................................................................... 13

7. Recommended Operating Conditions .......................................................................................... 14

8. Electical Characteristics ................................................................................................................ 15

8.1. Analog Characteristics ................................................................................................................... 15

8.2. DAC Digital Filter Characteristics (PCM Mode) ............................................................................ 19

8.3. DAC Digital-Filter Characteristics (DSD Mode) ............................................................................. 29

8.4. DC Characteristics ......................................................................................................................... 30

8.5. Switching Characteristics .............................................................................................................. 31

8.6. Timing Diagram .............................................................................................................................. 36

9. Functional Descriptions ................................................................................................................ 41

9.1. Control Mode ................................................................................................................................. 41

9.2. D/A Conversion Mode .................................................................................................................... 42

9.3. System Clock ................................................................................................................................. 45

9.4. Audio Interface Format .................................................................................................................. 51

9.5. Digital Filter .................................................................................................................................... 64

9.6. De-emphasis Filter (PCM Mode) ................................................................................................... 65

9.7. Digital Attenuator ........................................................................................................................... 66

9.8. Gain Adjustment Function ............................................................................................................. 67

9.9. Zero Detection, DSD Full-scale Detection .................................................................................... 68

9.10. LR Channel Output Signal Select, Phase Inversion Function .................................................... 73

9.11. PCM/DSD, EXDF/DSD Automatic Mode Switching Function ..................................................... 74

9.12. LDO .............................................................................................................................................. 83

9.13. Power Up/Down Sequence ......................................................................................................... 84

9.14. Power Down, Standby and Reset Function ................................................................................ 89

9.15. Synchronize Function (PCM Mode, EXDF Mode) ...................................................................... 93

9.16. Register Control Interface............................................................................................................ 95

9.17. Register Map ............................................................................................................................... 99

9.18. Register Definitions ................................................................................................................... 100

10. Recommended External Circuits ................................................................................................ 106

10.1. External Connection Example ................................................................................................... 106

10.2. Grounding and Power Supply Decoupling ................................................................................ 108

10.3. Reference Voltage ..................................................................................................................... 108

10.4. Analog Output ............................................................................................................................ 108

11. Package .......................................................................................................................................114

11.1. Outline Dimensions (HTQFP14 x 14-128, Unit: mm) ...........................................................114

11.2. Material & Terminal Finish .....................................................................................................115

11.3. Marking ..................................................................................................................................115

12. Ordering Guide ............................................................................................................................116

13. Revision Histroy ...........................................................................................................................116

IMPORTANT NOTICE ...........................................................................................................................117

[AK4499]

019001308-E-00 2019/02

- 4 -

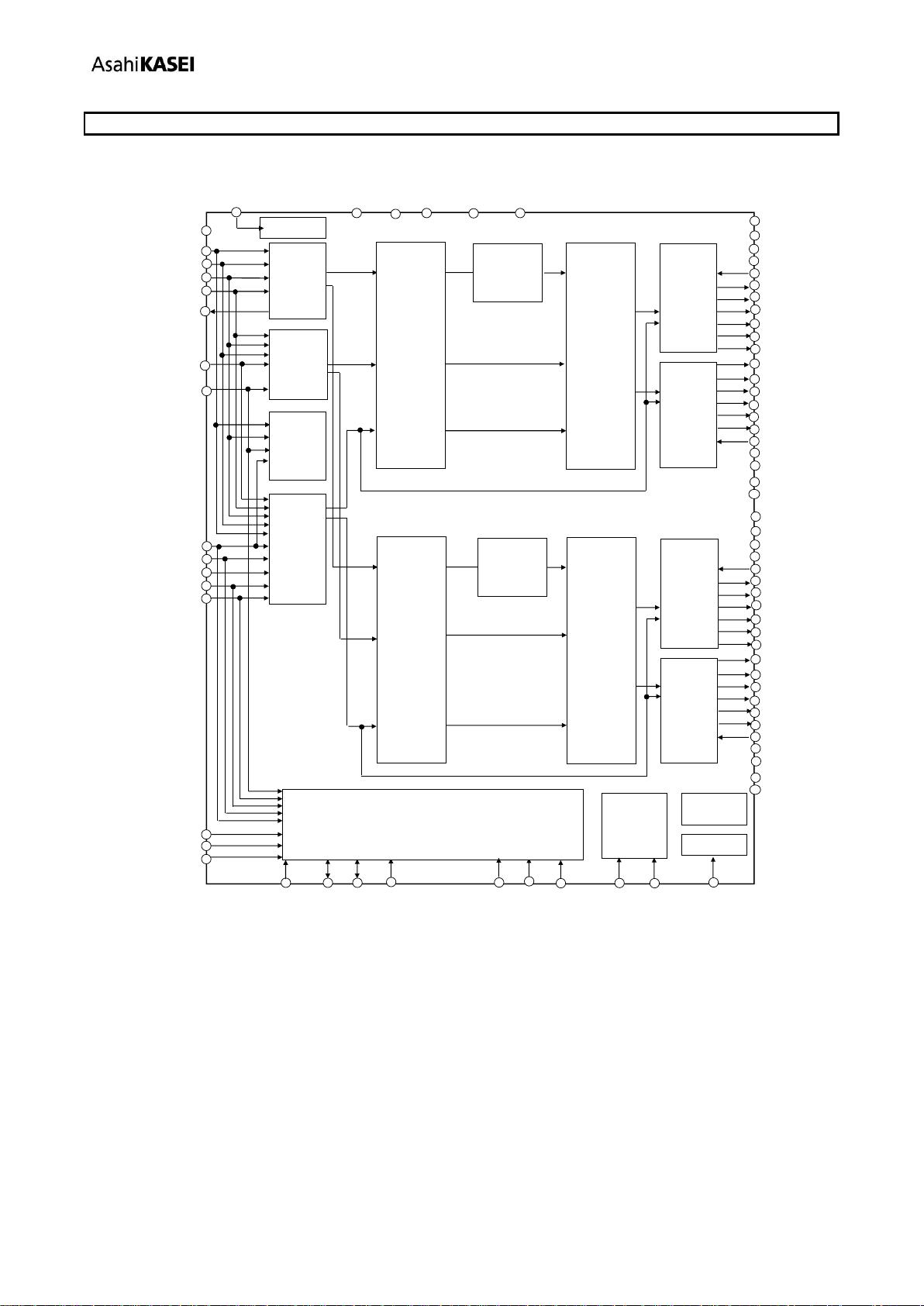

4. Block Diagram and Functions

4.1. Block Diagram

MCLK

SDATA1/DINL1/DSDL1

SMUTE/CSN

BICK/BCK/DCLK

SD/ CCLK/SCL

SLOW/CDTI/SDA

PDN

AVDD

SR

DACL1

Clock

Divider

DVSS

DVDD

SSLOW/WCK

ACKS/

CAD1

PSN

DIF0/

DZFL

DIF2/

CAD0

AVSS

Control

Register

LRCK/DINR1/DSDR1

DIF1/

DZFR

DATT

Soft Mute

Modulator

Volume Bypass

DSDD bit “1”

Normal path

DSDD bit “0”

MCLK Stop

Detection

TVDD

LDO

LDOE

TDM0/DCLK

DEM0/DSDL1

DSDR1

TDMO

INVR/

I2C

TEST

EXTR

IREF

VREFHL1

VREFLL1

1

VREFLR1

VREFHR1

EXTCL1P

EXTCL1N

OPINL1N

IOUTL1N

De-emphasis

&

Interpolator

DSD

Data

Interface/

DSD

Filter

OPINL1P

IOUTL1P

VCOMR1

SR

DACR1

EXTCR1P

EXTCR1P

OPINR1N

OPINR1P

IOUTR1P

IOUTR1N

VTSEL

VCOML1

8x

Interpolator

DATT

Soft Mute

Modulator

Volume Bypass

DSDD bit “1”

Normal path

DSDD bit “0”

De-emphasis

&

Interpolator

SDATA2/DINL2/DSDL2

L

DINR2/DSDR2

PCM

Data

Interface

External

DF

Interface

TDM1/DSDL2

2

VSSL1

VDDL1

VSSR1

VDDR1

SR

DACL2

VREFHL2

VREFLL2

21

VREFLR2

VREFHR2

EXTCL2P

EXTCL2N

OPINL2N

IOUTL2N

OPINL2P

IOUTL2P

VCOMR2

SR

DACR2

EXTCR2P

EXTCR2P

OPINR2N

OPINR2P

IOUTR2P

IOUTR2N

VCOML2

VSSL2

VDDL2

VSSR2

VDDR2

DCHAIN/DSDR2

PCM/DSD

EXDF/DSD

Automatic

Mode

Switching

Figure 1. AK4499 Block Diagram

[AK4499]

019001308-E-00 2019/02

- 5 -

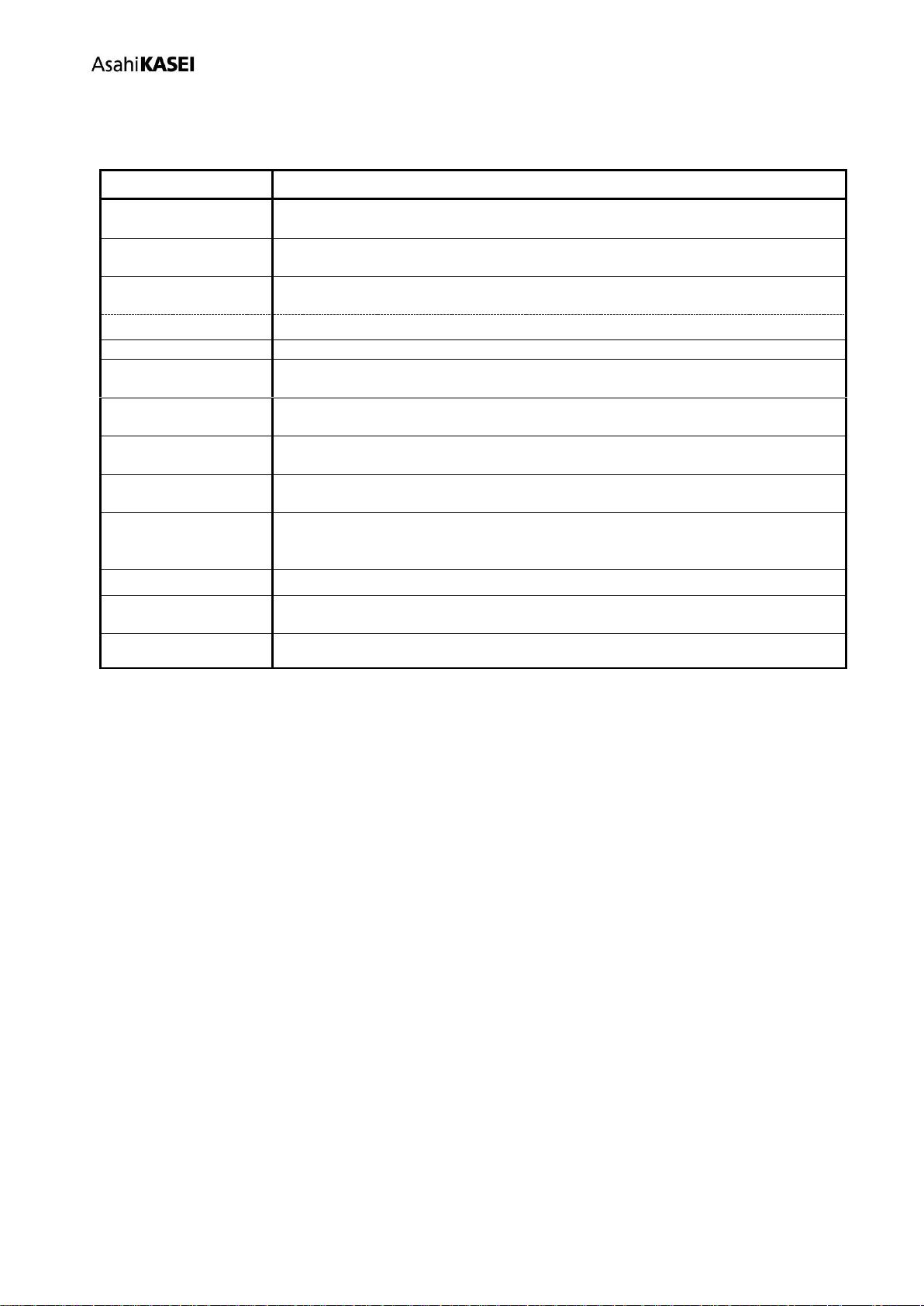

4.2. Functions

Block

Function

PCM Data Interface

Execute serial/parallel conversion of SDATA1/2 input data by synchronizing

with LRCK and BICK, and generate TDM output data.

External DF Interface

Receive external digital filter outputs. Execute serial/parallel conversion of

DINL1/2 and DINR1/2 input data by synchronizing with BICK.

DSD Data Interface

1-bit data that is input from DSDL1/2 and DSDR1/2 pins is received by

synchronizing with DCLK.

DSD Filter

FIR filter that reduces high frequency noise of DSD input data

DATT, Soft Mute

Apply DATT and Soft Mute process to input data.

De-emphasis &

Interpolator

A digital filter that applies De-emphasis process to input data and executes

over sampling.

ΔΣ Modulator

Output multi-bit data to SR DAC. This block consists of a third-order digital

delta-sigma modulator.

SR DAC

Convert multi bit output of ΔΣ Modulator into analog signal. This block consists

of a switched resistor DAC.

Control Register

Keep register settings for each mode. Control registers are accessed in 3-wire

(CSN, CCLK, CDTI) or I2C-Bus (SCL, SDA) control mode.

Clock Divider

Divide Master Clock

In PCM mode, master clock is divided automatically by fs rate auto detection

function. In DSD mode, the master clock frequency is set by DCKS bit.

MCLK Stop Detection

Detects when the master clock input is absent.

IREF

Generate reference current from the reference voltage generated internally,

using an external resistor.

LDO

Generate power for internal digital circuit (1.8V typ.).

剩余116页未读,继续阅读

fei634334

- 粉丝: 7

- 资源: 11

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0