ALTERA DDR3内存设计教程:PCB布局与DIMM脚印

"ALTERA DDR3 pcb layout MT41J64M16LA DDR3 DIMM footprint DDR3 layout .pdf"

本文档主要介绍了ALTERA公司关于DDR3 SDRAM设计的教程,特别关注DDR3 PCB布局方面的知识。DDR3内存是DDR(Double Data Rate)内存的第三代产品,具有更高的数据传输速率和更低的功耗,广泛应用于现代电子系统,特别是高性能计算和嵌入式系统中。

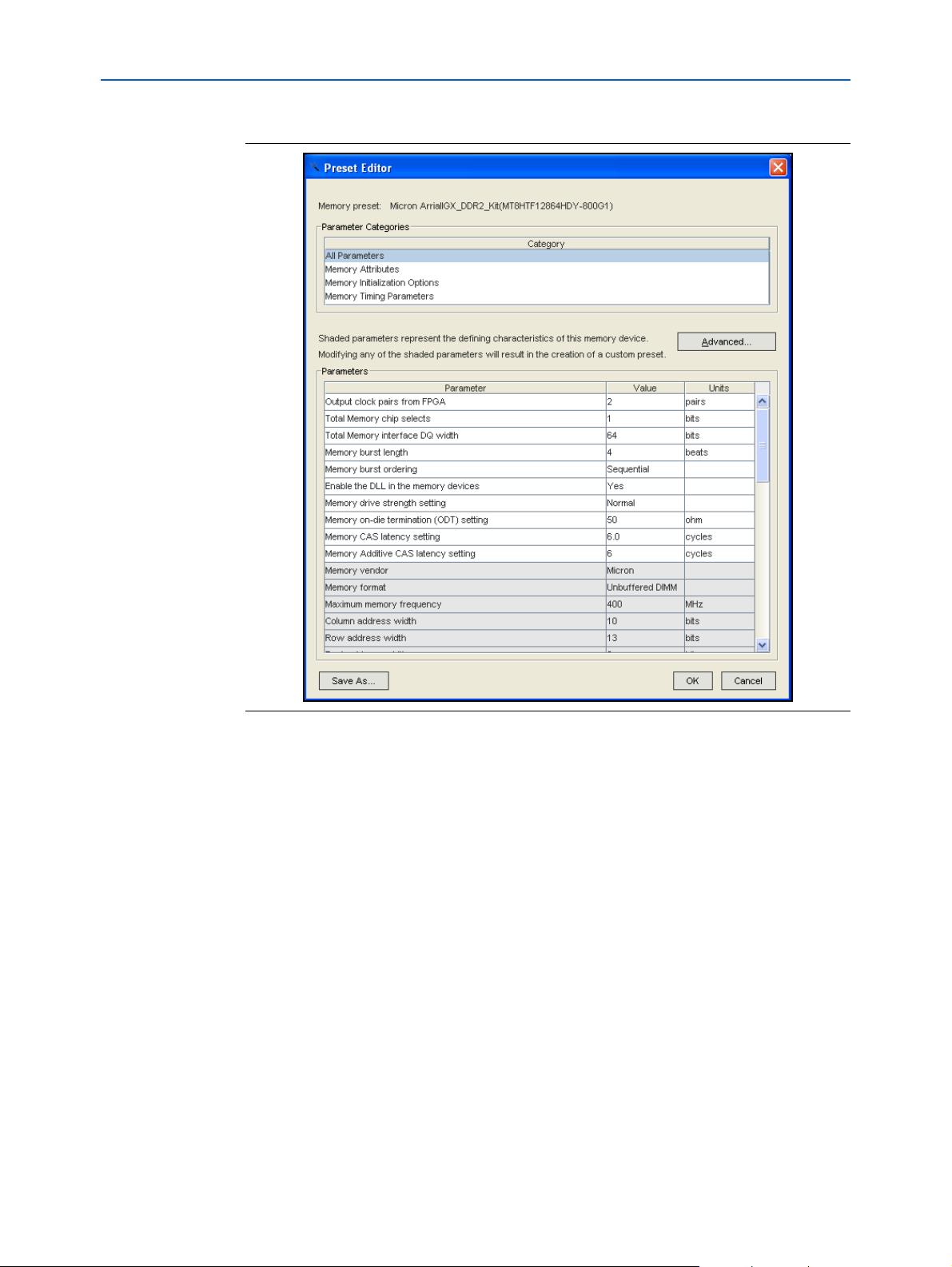

DDR3内存模块(DIMM)的布局设计是确保系统性能和稳定性的关键因素。MT41J64M16LA是一款DDR3 SDRAM芯片,其型号表明它是一个64Mx16位的设备,意味着它有64兆位的数据宽度,并以16位为单位进行存储和读取操作。在PCB布局中,正确放置这些内存芯片至关重要,以保证信号完整性、减少信号反射和串扰,同时满足电气规范。

文档可能涵盖以下关键知识点:

1. **DDR3内存工作原理**:DDR3内存利用时钟周期的上升沿和下降沿来传输数据,从而实现比DDR2更快的数据传输速度。它还引入了更精细的时钟调校机制,如ODT(On-Die Termination)和ZQ校准,以改善信号质量。

2. **DDR3内存模块结构**:DDR3 DIMM通常包含多个DRAM芯片,这些芯片通过地址、命令和数据线连接到主板上的内存控制器。了解这些接口的布局对于优化信号路径至关重要。

3. **PCB布线策略**:为了减少信号损失和噪声,DDR3内存走线应尽可能短且直。差分对的布线必须保持对称,以减小信号之间的相位差异。电源和地线的布局也非常重要,它们需要提供足够的去耦以降低电源噪声。

4. **DDR3时序和时钟管理**:DDR3内存需要精确的时序控制,包括CAS(列地址选通)、RAS(行地址选通)和WR(写使能)延迟。布局时需要考虑这些时序参数,确保所有组件都能同步工作。

5. **热管理**:DDR3内存运行时会发热,因此在布局时要考虑散热问题,可能需要在内存芯片周围设置适当的散热片或热沉。

6. **信号完整性**:DDR3的高速特性使得信号完整性成为设计挑战。通过合理布局,使用适当的阻抗控制和过孔设计,可以减少信号反射和串扰,提高系统可靠性。

7. **EMI(电磁干扰)控制**:DDR3的高速信号可能导致电磁辐射增加,设计时应遵循最佳实践,如使用屏蔽层、合理布线和选择低电磁发射的元器件,以降低对外部设备的干扰。

8. **兼容性和标准**:DDR3内存的设计需要符合JEDEC(Joint Electron Device Engineering Council)的标准,确保与各种主板和处理器的兼容性。

文档可能还会涉及故障排查、测试方法和性能优化技巧等内容,帮助工程师进行有效的DDR3内存模块设计。由于ALTERA是一家知名的FPGA(现场可编程门阵列)供应商,这份教程可能还会包含如何将DDR3内存集成到ALTERA FPGA系统中的指导。

这份文档是DDR3 PCB布局设计的重要参考资料,对于理解和实现高效、可靠的DDR3内存系统具有很高的价值。

2012-11-25 上传

2018-12-14 上传

2022-09-22 上传

2022-09-23 上传

2019-05-19 上传

2007-05-16 上传

2007-07-06 上传

2014-12-04 上传

hmanhcc

- 粉丝: 1

- 资源: 16

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南