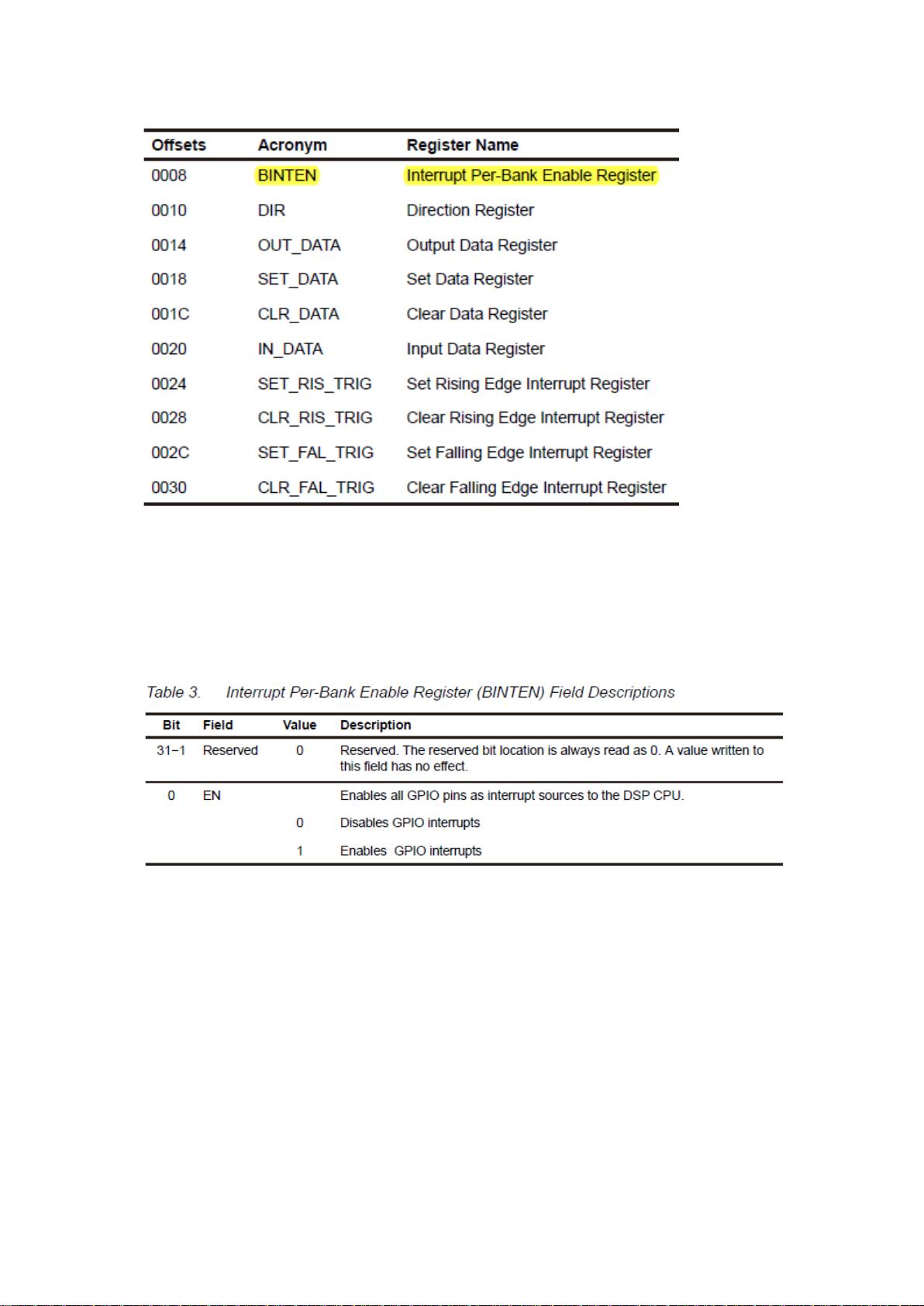

"DSP6455中断与GPIO系统.pdf" 本文将探讨TI的TMS320C6455 DSP中的GPIO(通用输入输出)系统及其与中断系统的结合,这是在DSP与FPGA之间利用EDMA(直接内存访问)进行高效数据传输的关键组成部分。在基于DSP和FPGA的嵌入式系统中,用于视频采集、编解码和传输的方案,理解这些底层硬件机制至关重要。 首先,C6455 DSP提供了16个可配置的GPIO管脚,它们可以设置为通用输入、输出或中断和EDMA事件触发器。GPIO的配置由DIR寄存器决定,其中0表示输出模式,1表示输入模式。在输出模式下,SET_DATA和CLR_DATA寄存器分别用来设置管脚为高电平和低电平,但写入0则无效。当配置为输入时,可通过读取IN_DATA寄存器获取管脚状态。 中断系统在C6455中扮演着重要角色,它允许CPU对特定事件作出快速响应,如外部设备的信号。GPIO作为中断源时,可以触发中断服务例程,从而实现对实时性要求高的任务处理。同时,这些GPIO也可以与EDMA(即芯片内的“协处理器”)协同工作,当GPIO状态改变时,可以启动预定义的EDMA传输,实现数据的自动搬移,减轻CPU负担。 EDMA模块在C6455中是高度灵活的,它支持异步传输,可以独立于CPU进行大量数据的高速传输,这对于视频处理尤其重要。EDMA可以预先编程,配置成在GPIO事件发生时自动开始或结束传输,从而在DSP与FPGA之间建立高效的通信链路。 此外,理解DSP-C6000系列的EMIFA(扩展存储器接口)也很关键,因为这涉及到外部存储器的访问,对于大量数据的存储和读取至关重要。FPGA的乒乓RAM(Ping-Pong RAM)则提供了高速缓存功能,能够在数据处理过程中提供连续的存储空间,减少延迟。 在视频处理系统中,还需要熟悉特定的视频格式,如VGA或PAL,以及相应的编解码算法,这些决定了数据的组织和处理方式。通过综合运用这些技术,可以构建高性能的视频处理平台。 理解TMS320C6455的GPIO、中断系统和EDMA机制是实现高效FPGA-DSP通信的基础,对于构建复杂的嵌入式视频处理系统至关重要。通过深入学习和应用这些知识,可以设计出能够满足实时需求并优化性能的解决方案。

剩余15页未读,继续阅读

- 粉丝: 171

- 资源: 2138

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 前端面试必问:真实项目经验大揭秘

- 永磁同步电机二阶自抗扰神经网络控制技术与实践

- 基于HAL库的LoRa通讯与SHT30温湿度测量项目

- avaWeb-mast推荐系统开发实战指南

- 慧鱼SolidWorks零件模型库:设计与创新的强大工具

- MATLAB实现稀疏傅里叶变换(SFFT)代码及测试

- ChatGPT联网模式亮相,体验智能压缩技术.zip

- 掌握进程保护的HOOK API技术

- 基于.Net的日用品网站开发:设计、实现与分析

- MyBatis-Spring 1.3.2版本下载指南

- 开源全能媒体播放器:小戴媒体播放器2 5.1-3

- 华为eNSP参考文档:DHCP与VRP操作指南

- SpringMyBatis实现疫苗接种预约系统

- VHDL实现倒车雷达系统源码免费提供

- 掌握软件测评师考试要点:历年真题解析

- 轻松下载微信视频号内容的新工具介绍

信息提交成功

信息提交成功