17

TLV320AIC3109-Q1

www.ti.com.cn

ZHCSGM5A –AUGUST 2017–REVISED NOVEMBER 2017

版权 © 2017, Texas Instruments Incorporated

7.3 Feature Description

7.3.1 Hardware Reset

The TLV320AIC3109-Q1 requires a hardware reset after power-up for proper operation. After all power supplies

are at their specified values, the RESET pin must be driven low for at least 10 ns. If this reset sequence is not

performed, the TLV320AIC3109-Q1 may not respond properly to register reads or writes.

This device also offers a software reset (page 0, register 1) that can be used by the host to reset all registers on

page 0 and page 1 to their reset values. In cases where changes are needed only for routing or volume-control

registers, these changes can be accomplished by writing directly to the appropriate registers rather than using

the software or hardware reset.

In cases where the ESD events generate a device reset, a minimum 1-nF capacitor is recommended to be

connected between the RESET pin and DVSS. This capacitor avoids ESD events that can place the codec in

default state.

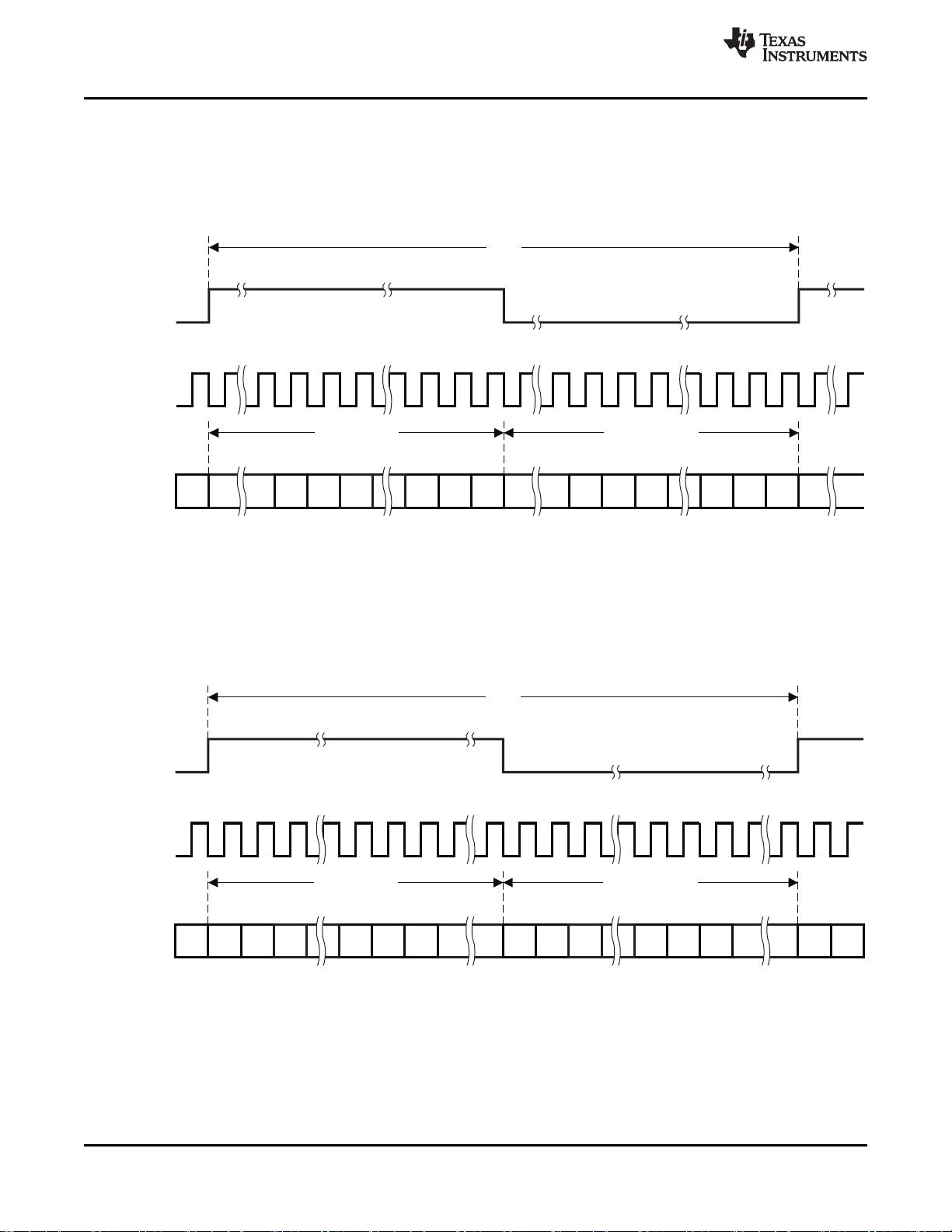

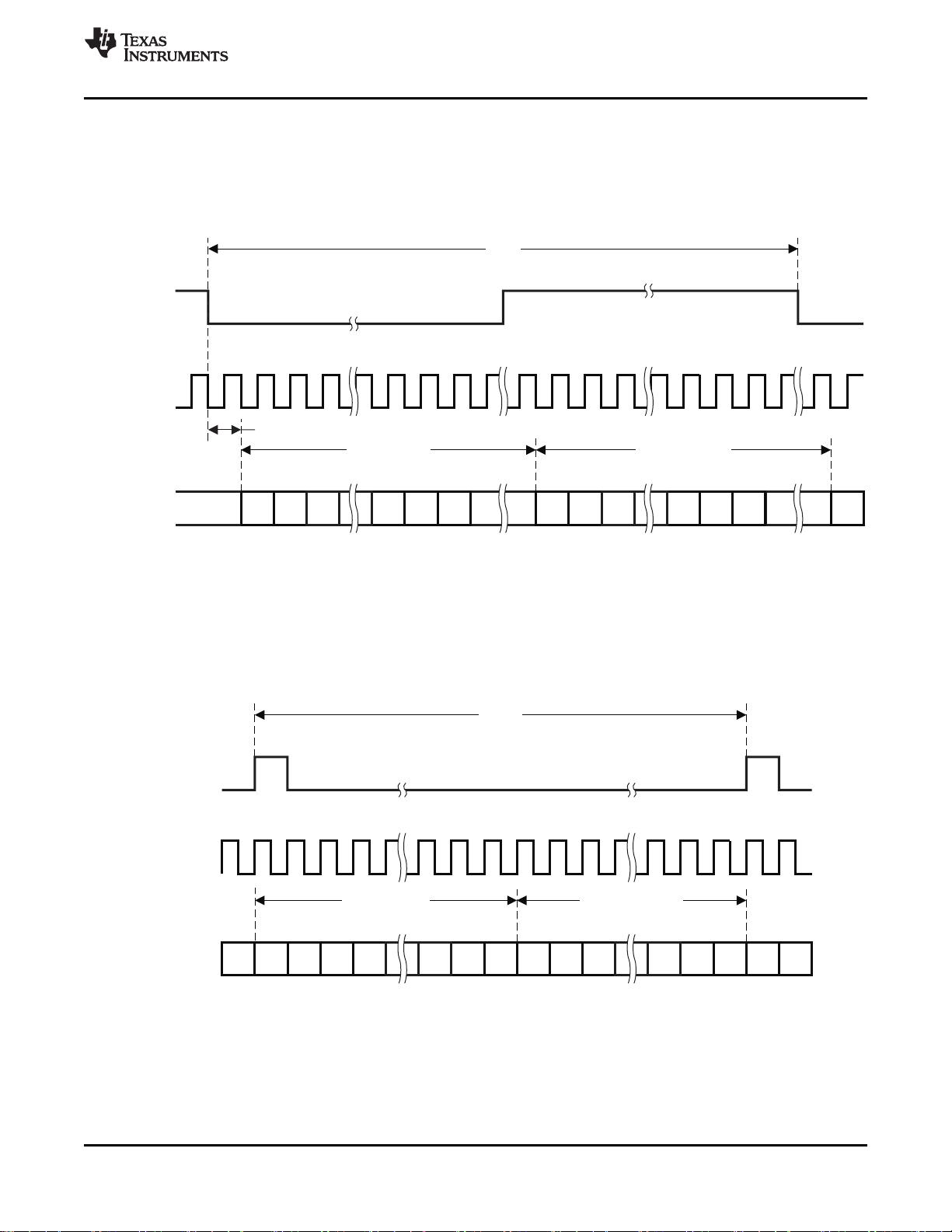

7.3.2 Digital Audio Data Serial Interface

Audio data are transferred between the host processor and the TLV320AIC3109-Q1 via the digital audio data

serial interface. The audio bus of the TLV320AIC3109-Q1 can be configured for left- or right-justified, I

2

S, DSP,

or TDM modes of operation, where communication with standard PCM interfaces is supported within TDM mode.

These modes are all MSB-first, with data width programmable as 16, 20, 24, or 32 bits. In addition, the word

clock (WCLK) and bit clock (BCLK) can be independently configured in either master or slave mode for flexible

connectivity to a wide variety of processors.

The word clock (WCLK) is used to define the beginning of a frame, and can be programmed as either a pulse or

a square-wave signal. The frequency of this clock corresponds to the selected ADC and DAC sampling

frequency.

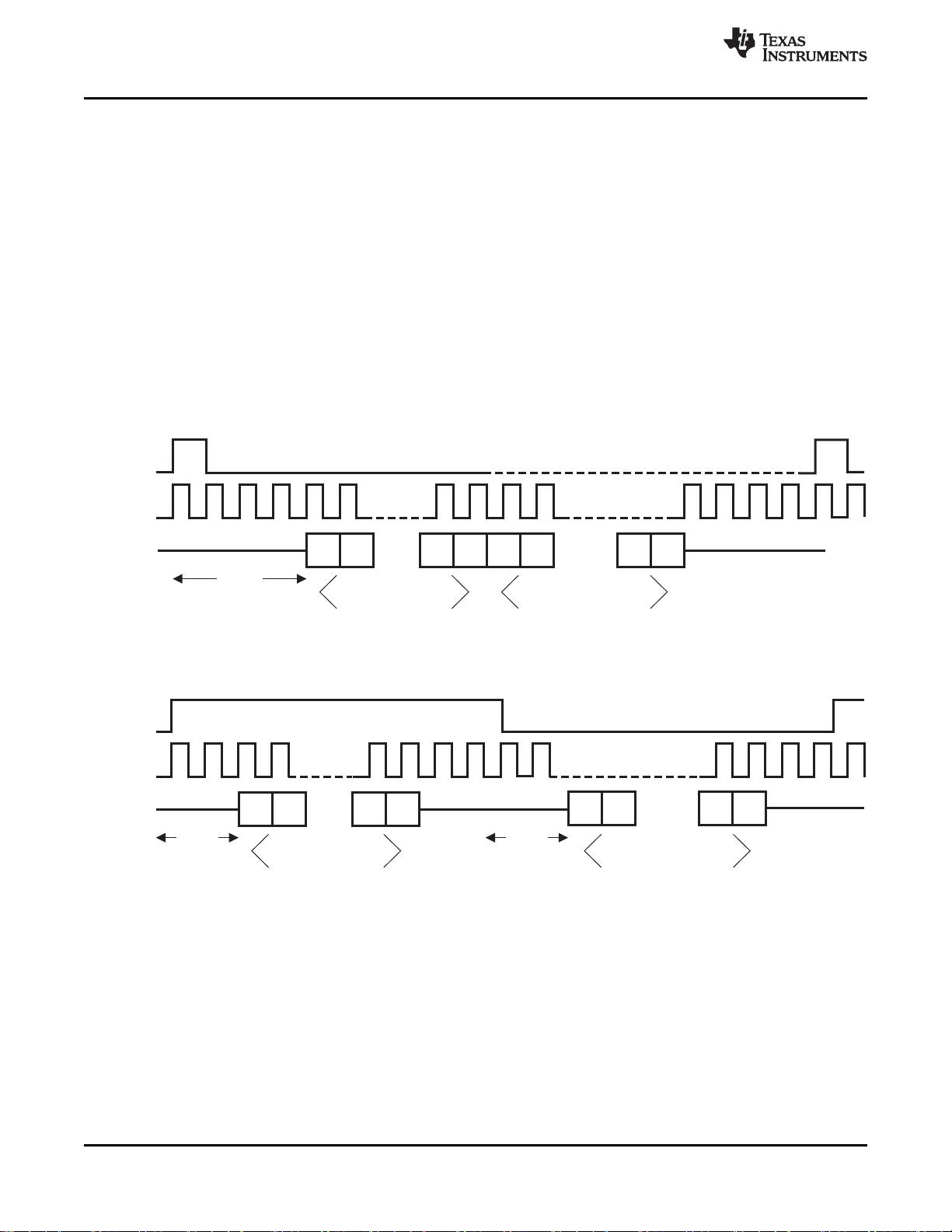

The bit clock (BCLK) is used to clock in and out the digital audio data across the serial bus. When in master

mode, this signal can be programmed in two further modes: continuous transfer mode, and 256-clock mode. In

continuous transfer mode, only the minimal number of bit clocks required to transfer the audio data are

generated, so in general the number of bit clocks per frame is two times the data width. For example, if the data

width is chosen as 16 bits, then 32-bit clocks are generated per frame. If the bit clock signal in master mode is to

be used by a PLL in another device, then the 16-bit or 32-bit data-width selections are recommended be used.

These cases result in a low-jitter bit clock signal being generated, with frequencies of 32 f

S

or 64 f

S

. For a 20-bit

and 24-bit data width in master mode, the bit clocks generated in each frame are not all of equal period because

the device does not have a clean 40-f

S

or 48-f

S

clock signal readily available. The average frequency of the bit

clock signal is still accurate in these cases (40 f

S

or 48 f

S

), but the resulting clock signal has higher jitter than in

the 16-bit and 32-bit cases.

In 256-clock mode, a constant 256 bit clocks per frame are generated, independent of the data width chosen.

The TLV320AIC3109-Q1 further includes programmability to place the DOUT line in the high-impedance state

during all bit clocks when valid data are not being sent. By combining this capability with the ability to program at

what bit clock in a frame the audio data begins, time-division multiplexing (TDM) can be accomplished, resulting

in multiple codecs able to use a single audio serial data bus.

When the digital audio data serial interface is powered down when configured in master mode, the pins

associated with the interface are put into a high-impedance state.

The following subsections describe the supported data interface protocols. These protocols can be used for left-

and right-channel applications. Only one of the two possible channels can be selected because the

TLV320AIC3109-Q1 is a mono audio codec. Only the left channel is valid for DOUT (output data). For DIN (input

data), valid data can be selected with bits 4 and 3 of register 7, page 0.